您的位置:電子發燒友網 > 電子技術應用 > 嵌入式技術 > FPGA/ASIC技術 >

PLD設計速成(6)-編譯和布線(3)

2012年05月18日 17:08 來源:本站整理 作者:秩名 我要評論(0)

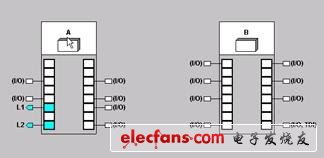

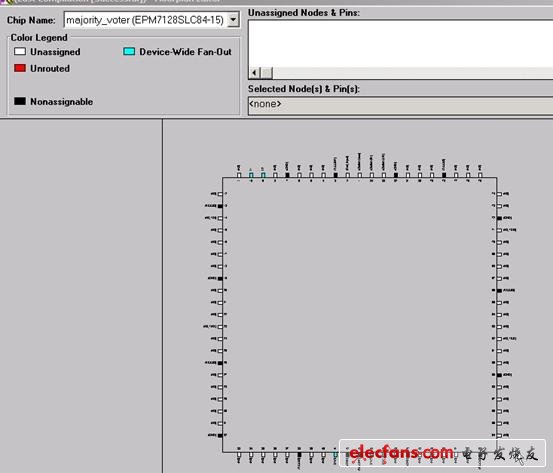

編譯后可以看到IO在芯片上的分布:MAX plusII-> Froorplan Editor

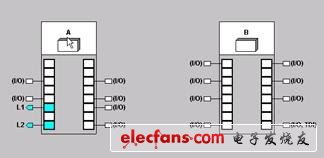

將彈出一窗口如下圖

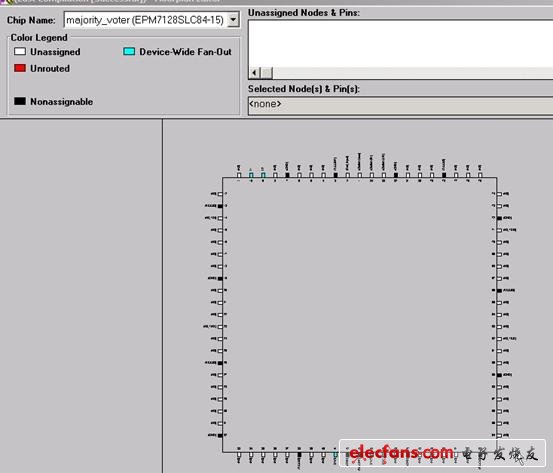

雙擊空白處,可以看到下圖所示IO在芯片EPM7128SLC84上的布局

創建一個設計的符號

(此和本設計無關,僅供其他設計在高層調用)

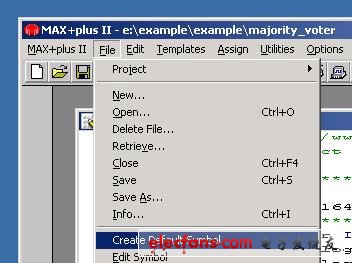

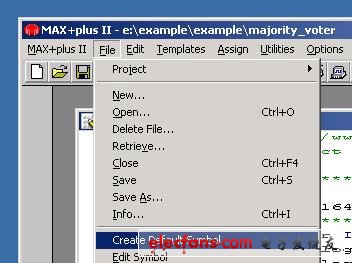

在 File菜單中選擇 Create Default Symbol 項,即可創建一個設計的符號。該符號可被高層設計調用。

此時會產生一個COMPILE窗口,直接點Start,完成后點確認

本文導航

- 第 1 頁:PLD設計速成(6)-編譯和布線(1)

- 第 2 頁:指定以下管腳

- 第 3 頁:編譯后