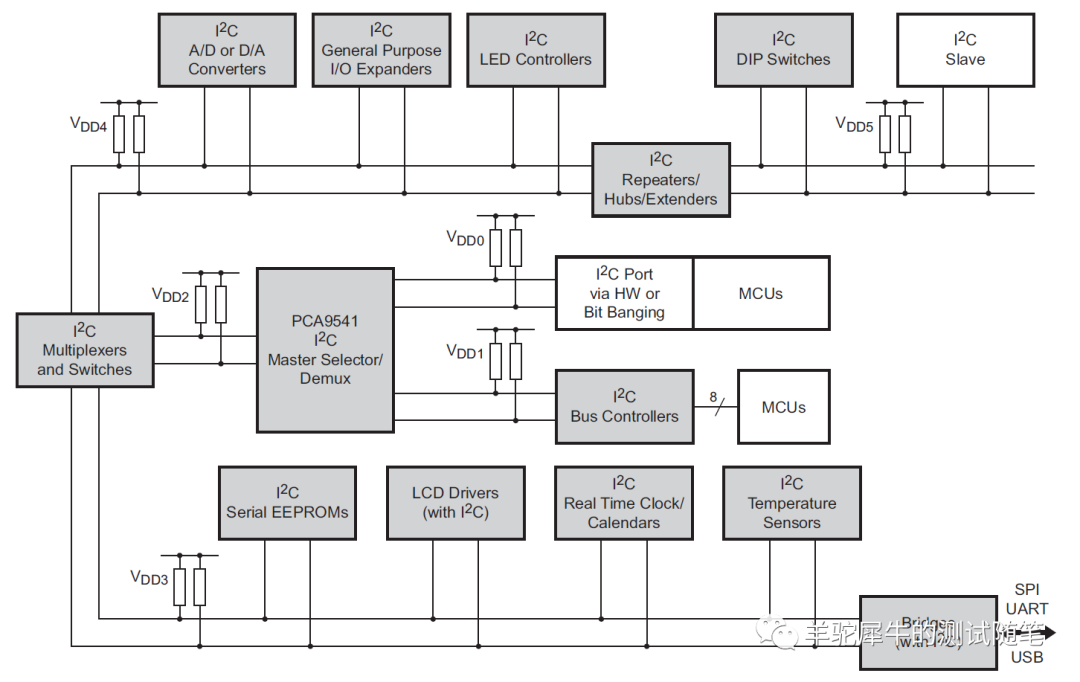

前面一章講解了I2C總線的基本原理,那么在電路設(shè)計完成打板回來,肯定要做信號測試來驗證設(shè)計;

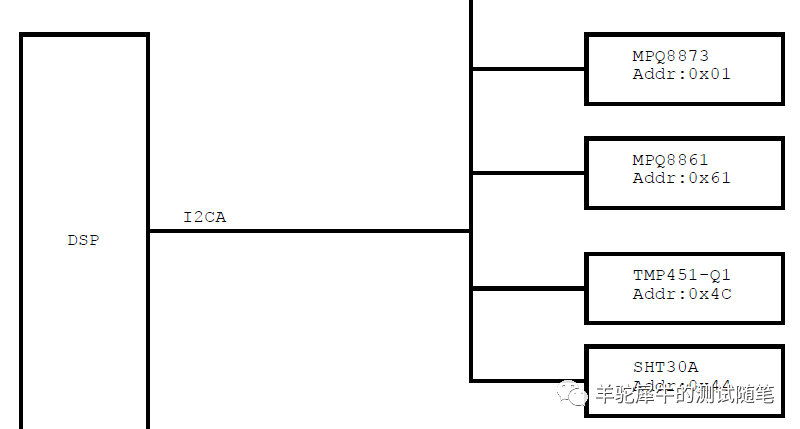

1、梳理測試內(nèi)容,根據(jù)電路圖上梳理出I2C總線,包括每一路I2C一共有幾個主機,幾個從機,以及從機的地址信息;

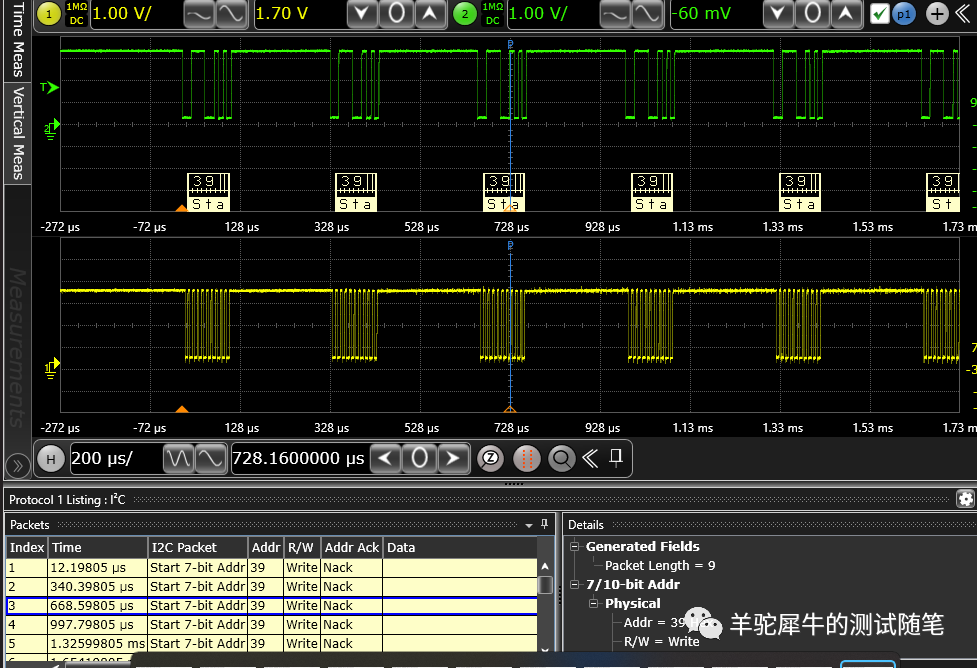

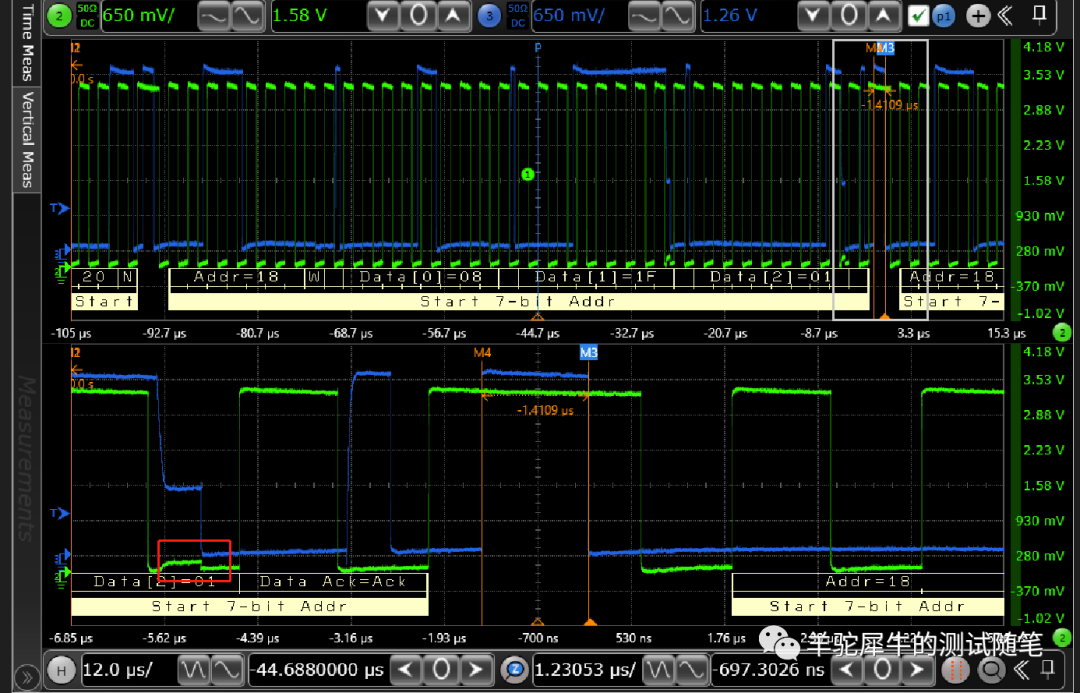

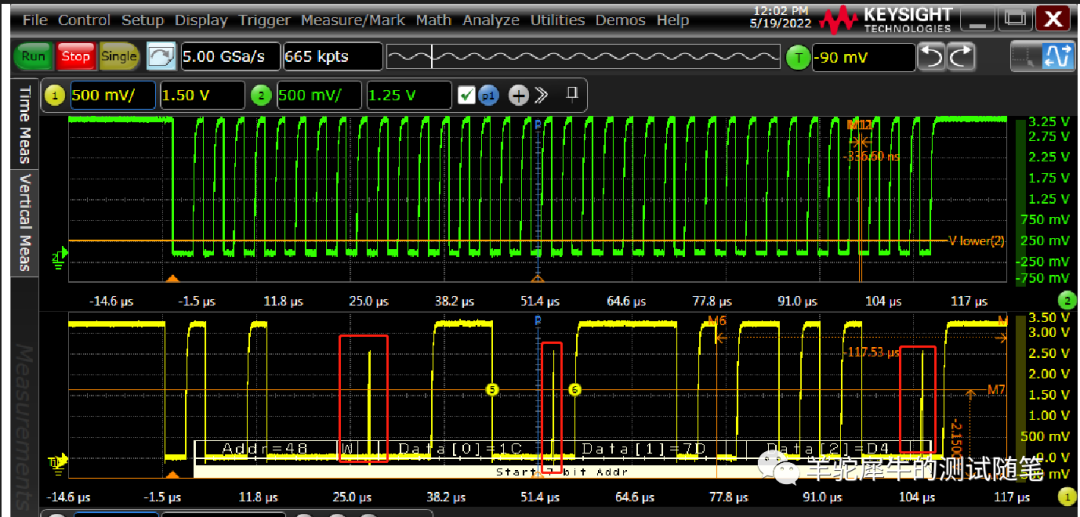

2、使用示波器的I2C協(xié)議分析功能或者其他I2C解析工具,將總線上的實時數(shù)據(jù)抓取解析,看一下是否包括電路設(shè)計上的所有器件地址,或者是有多余的地址信息;

因為小編在測試中遇到太多實測地址比設(shè)計少的,這個好理解,一個是冗余設(shè)計,當前沒有使用,一個原因是軟件上漏掉了;此外,實測到設(shè)計上沒有的地址信息,這個大概率發(fā)生在后期改版過程中,硬件設(shè)計更換了總線上的器件,地址也給到軟件做更改,但是軟件代碼上沒有將之前的不再使用的地址信息刪掉,導(dǎo)致總線還是存在訪問此地址信息的請求數(shù)據(jù);

無論是多了還是少了地址,對于測試來講都是有問題的,必須搞清楚,是問題的話,就分析解決,不是的話,就做個澄清說明;

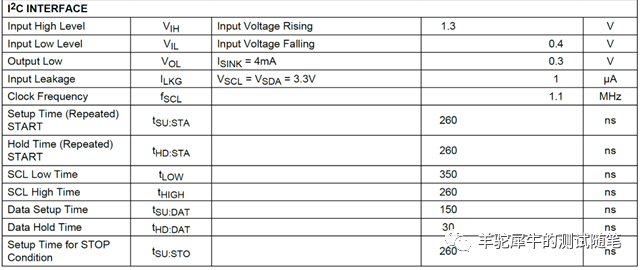

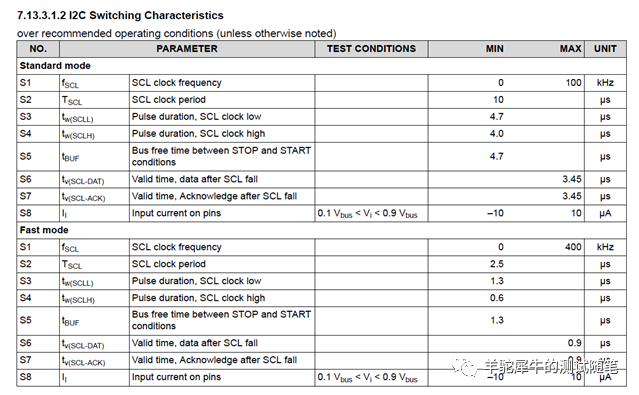

3、整理各個器件對于I2C總線的電平與時序要求;詳細如下:

頻率:指的是SCL的時鐘頻率,測量這個參數(shù)的意義在于判定總線是單一的速率還是多種速率模式混合,其次確定了時鐘頻率,有助于后面時序參數(shù)的確認,因為不同速率數(shù)據(jù)時序的要求是不一樣的。

正/負脈寬:SCL的高低電平寬度,因為I2C是高電平進行數(shù)據(jù)采樣,低電平時SDA電平變化,所以,無論高電平還是低電壓都一定有個最小值來滿足采樣和電平變化;

邏輯高/低電平:SCL和SDA均要測量,只有測量值滿足高低電平的要求,才真正意義上能被識別為邏輯1或0;此處要注意的是,即使總線電平是同一個VCC,不同器件對于邏輯電平門限也是不太一樣;

上升/下降時間:指的是SCL和SDA的邊沿在高低電平門限之間的持續(xù)時間,一般取30%~70%,這也只是一個相對的經(jīng)驗值,因為大多數(shù)的I2C器件邏輯高低電平門限是30%Vcc和70%Vcc;追求準確度來說,要根據(jù)實際器件的高低電平門限值來卡這個時間;前文講到總線電容和上拉電阻的值會影響上升時間的值,若測試有問題,可以通過調(diào)節(jié)上拉電阻的值來改善。

Vmax/Vmin:總線數(shù)據(jù)的最大電平和最小電平值;主要看是否有上下過沖,若過沖超過芯片要求,很可能會損壞芯片。

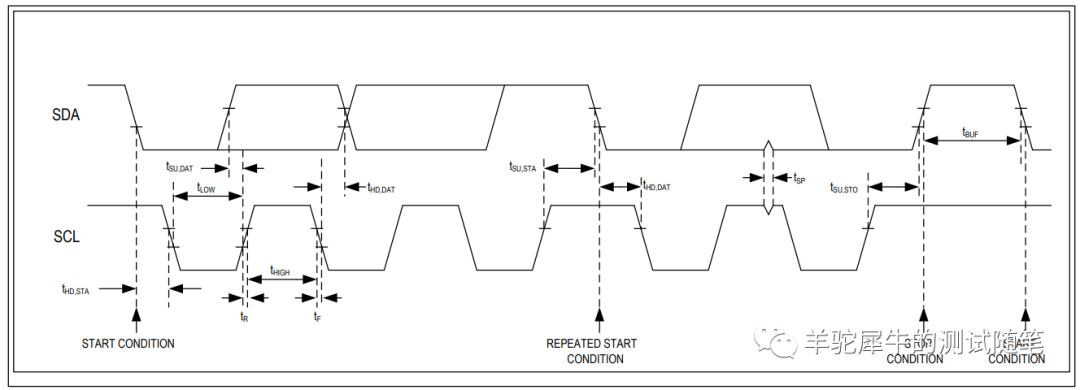

Tbuf:幀間隔時間,即SDA線的上一幀傳輸結(jié)束到下一幀開始之間的間隔時間。

開始標志位的保持時間(tHD:STA):在SCL為高電平時SDA由高變低的邊沿到SCL第一個下降沿的時間。

結(jié)束標志位的建立時間(tSU:STO):在SCL為高電平時SDA由低變高的邊沿到SCL前一個上升沿的時間。

重復(fù)起始標志位的建立時間(tSU:STA):在第9個時鐘之后。在SCL為高的上升沿到SDA的下降沿之間的時間間隔。

數(shù)據(jù)建立時間(tSU:DAT):一個比特周期內(nèi),SDA變化沿到SCL上升沿的時間間隔。

數(shù)據(jù)保持時間(tHD:DAT):一個比特周期內(nèi),SDA變化沿到SCL下降沿的時間間隔。

4、搭建測試環(huán)境,實操測試

- 測試所需設(shè)備:示波器(最好有協(xié)議分析軟件)、示波器探頭(有源探頭優(yōu)選)、待測DUT(加載I2C總線通訊的軟件)

- 選擇信號測試點:測量寫信號,在從器件端靠近芯片pin腳;測量讀信號,在主器件端靠近芯片pin腳;

- 注意事項:探頭的接地線盡可能短,避免引額外電感量影響測試準確性。

下面以實際的例子來演示:

- 待測I2C總線只有一主一從,從機地址為 0x39,用示波器抓取總線數(shù)據(jù)并解析,確認是只有0x39地址的數(shù)據(jù);

- 主從器件的I2C時序要求

常見問題:

1、上升下降時間不滿足

更改上拉電阻的阻值

2、建立保持時間不滿足

①是否速率太低,調(diào)高至fast mode或者更高速率看一下

②數(shù)據(jù)SDA變化沿調(diào)整,前移或者后移

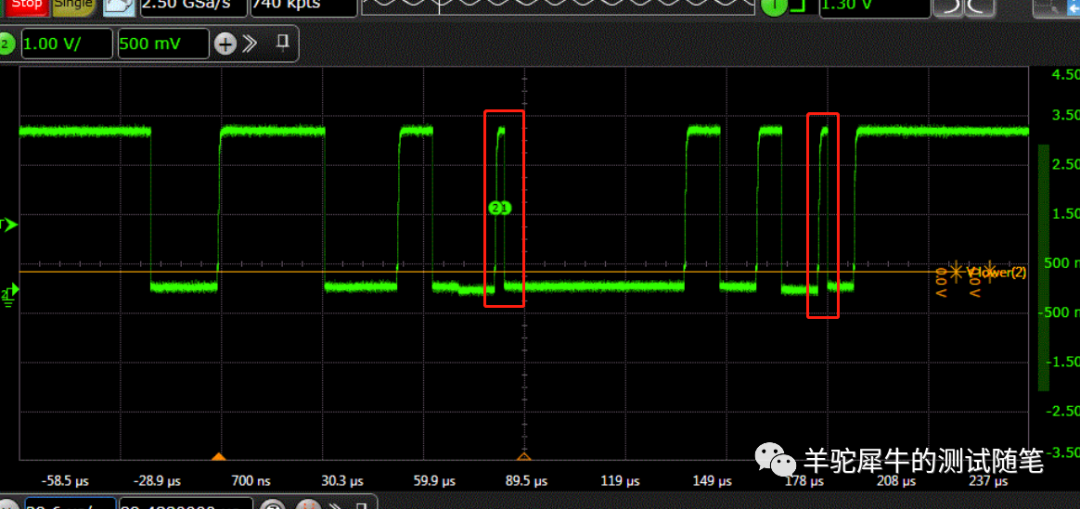

3、SDA邊沿有臺階

①一般發(fā)生在主從對總線控制的切換時

②若芯片內(nèi)部有上拉,外部還上拉至Vcc,那么在主機釋放總線后會被內(nèi)部上拉電阻分壓至臺階電平,然后再被從機拉低

4、我最開始學(xué)習(xí)I2C總線,對于總線協(xié)議了解的不清楚,造成了一個誤解如圖所示紅的框出來的波形,起初以為像第一張圖里脈寬很小,電壓也不高的是毛刺信號,第二張的是數(shù)據(jù)信號;其實都不對,兩張圖片里的是同一個東西,即應(yīng)答信號前釋放總線造成的;為什么電平與脈寬大小不一,是跟上拉電阻和從器件響應(yīng)時間決定的。上升時間長的話,主機釋放總線,電平從低開始緩慢升高,在還未升至Vcc之前,從機開始應(yīng)答,拉低總線,那么就很像毛刺;若上升時間很快,從機還沒響應(yīng)之前就會有一段時間的高電平;

-

上拉電阻

+關(guān)注

關(guān)注

5文章

363瀏覽量

30734 -

示波器

+關(guān)注

關(guān)注

113文章

6282瀏覽量

185855 -

I2C總線

+關(guān)注

關(guān)注

8文章

406瀏覽量

61173 -

SDA

+關(guān)注

關(guān)注

0文章

124瀏覽量

28266 -

SCL

+關(guān)注

關(guān)注

1文章

239瀏覽量

17178

發(fā)布評論請先 登錄

相關(guān)推薦

I2C總線原理詳解

i2c總線ppt(I2C總線器件應(yīng)用)

i2c總線的特點

I2C總線接口模塊設(shè)計

基于CPLD的I2C總線接口設(shè)計

互聯(lián)IC總線(I2C)

i2c總線用來做什么_i2c總線數(shù)據(jù)傳輸過程

I2C總線的基本通信總結(jié)

I2C總線信號與測試案例(二)

I2C總線信號與測試案例(二)

評論