1 引言

ESD(Electric Static Discharge)保護結構的有效設計是CMOS集成電路可靠性設計的重要任務之一,其ESD結構與工藝技術、特征尺寸密切相關,隨著IC工藝技術的進一步發展,特征尺寸越來越小,管子的柵氧層厚度越來越薄,芯片的面積規模越來越大,而外圍的使用環境并未改變,因此ESD的失效問題面臨越來越嚴峻的考驗,在亞微米CMOS IC中,通常做LDD(Lightly-Doped Drain)注入,在深亞微米超大規模CMOS IC設計中,通常有Silicide 或Salicide技術,這些技術的使用有助于提高電路的速度、集成度、可靠性等,但這些技術對電路的抗ESD性能極為不利,降低了ESD可靠度。在亞微米以下的電路設計中,需要對電路進行全芯片的ESD保護結構的設計。如何使全芯片有效面積盡可能小、ESD性能可靠性滿足要求且不需要增加額外的工藝步驟成為全芯片設計者的主要考慮的問題。

2 電路實例

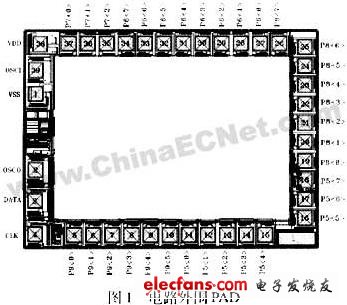

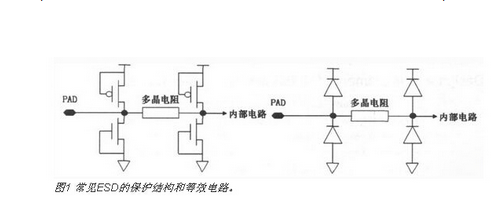

電路為鍵盤編碼控制電路,采用0.5μm-0.6μm SPSM CMOS阱工藝,工作電壓為3V、5V,除ROM外集成度約5000門,面積為2.0×1.5mm2,一共有39個PAD,其中I/O引腳36個,一個時鐘振蕩輸入腳,一個VDD,一個VSS。PAD排列如圖1所示。

?

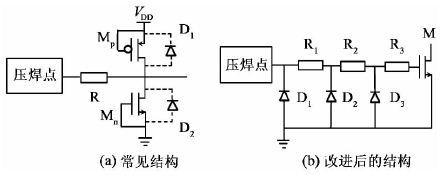

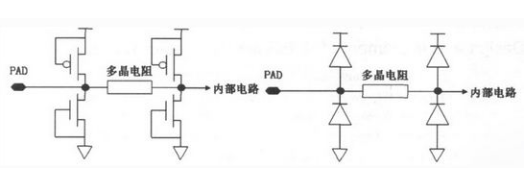

I/O口的保護結構為Finger型MOS輸出管及GGNMOS管,VDD與VSSPAD旁邊各有一個VDD-VSS電壓鉗位保護電路,邏輯結構如圖2。該結構在電路正常上電工作時,N1管作為一個VDD與VSS之間的反向二極管,而在ESD發生時,N1管開啟,作為ESD瞬時低阻抗大電流泄放通道,VDD與VSS之間的電壓則被鉗位,從而起到保護內部電路的作用。該結構又稱為ESD瞬態檢測電壓電路,其中R是由N阱電阻構成,C為MOS電容。

?

用ESD模型之一的人體模型工業測試標準HBMMIL-STD-883C method 3015.7對其進行ESD打擊實驗。

結果在I/O-VDD、I/O-VSS、I/O-I/O模式下,其抗擊電壓可達到4kV以上,但在VDD-VSS模式下,只能達到750V,在1kV時,電源與地短路從而造成整個電路失效。

初步分析的結果為,電源與地之間的保護結構如圖2,在版圖的設計上有薄弱環節,使該結構自身的健壯性級差,從而影響了整個電路的ESD性能。

為了驗證這一想法并找到改進的辦法,對該電路做了下述實驗。

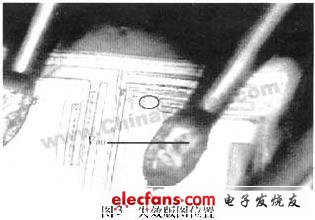

首先,對電路做液晶分析實驗,即在電路上滴上幾滴特殊的化學物質(具有流動性),然后在VDD與VSS的管腳灌入大電流,該化學液體聚集在VDD與VSS通路上電流最集中處,從而找到了擊穿點。該擊穿點就在VDDPAD附近,見圖3中畫圈的地方。

?

然后,對該電路進一步做了FIB實驗,即用激光把電路中該結構去掉,再做ESD打擊實驗,ESD結果顯示:VDD-VSS模式下,ESD抗擊電壓超過5kV,但I/O-VDD、I/O-VSS、I/O-I/O模式下最差的只能達到1.3kV電路就短路失效了。

所以,從本電路的ESD實驗結果及所做的實驗分析可得到:

(1)電路中,VDD-VSS電壓鉗位保護結構對提高整個電路的ESD性能非常必要,不能輕易去掉。

(2)該結構自身必須要有一定的健壯性,所以該結構中各器件的設計尺寸及版圖設計規則非常重要。

下面將進一步探討在亞微米CMOS IC ESD結構的設計中,VDD-VSS電壓鉗位結構的有效設計。

在HBM(Human Body Model)模型中,主要包含三種ESD的打擊方案:

(1)I/O-VDD/VSS;(2)I/O-I/O;(3)VDD-VSS;

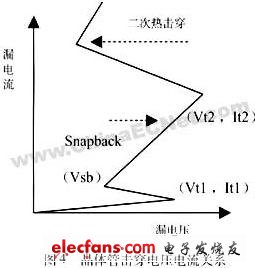

幾種方式相對獨立也相互影響,其中I/O-VDD/VSS模式下主要利用每個I/O口對VDD、VSS直接的保護結構,通常放置在每個I/O PAD的兩側,如一對簡單的二極管,Finger型的GGNMOS(Gate-Ground NMOS)、TFO(Thick-Field-Oxide)場管、SCR或幾個結構的組合等,主要利用晶體管的Snap back-down驟回崩潰區對電壓進行鉗位,見圖4,其中PS-mode及ND-mode模式下電路易損壞;I/O-I/O及VDD-VSS模式則與VDD、VSS間直接的ESD保護結構的設備及全芯片的ESD保護結構設計極為相關。特別是全芯片VDD、VSS間直接有效的ESD低阻抗大電流泄放通道的設計能有效提高電路的整體抗ESD性能,關于全芯片的ESD結構設計將在文章的最后予以簡單的闡述。

?

3 仿真分析及具體設計結果

3.1 仿真分析

在亞微米的ESD結構的設計中,一種常見的具體的ESD瞬態檢測電壓如圖2 VDD-VSS間的電壓鉗位結構。其原理如下:

主要利用結構中的RC延遲作用,一般T=RC被設計為100ns-1000ns之間,而ESD脈沖通常為納秒級,其上升時間為十幾納秒。初始狀態,IC處于懸空狀態下,當個正ESD電壓出現在VDD電源線上,而VSS相對為0時,Vx通過RC開始充電,由于其充電常數T比VDD的上升時間大的多,致使Vx無法跟隨VDD的變化,從而使P0管打開,N0管關閉,Vg電壓迅速上升,N1大管開啟,從而提供了一個從VDD到VSS的低阻抗大電流泄放通道并對內部的VDD與VSS有一個電壓鉗位作用,從而有效地保護了內部電路。 在正常上電時,因為正常的上電時間為毫秒級,所以Vx的充電可以跟隨VDD變化,當上升到一定電壓時,N0管開啟,P0管一直關閉,Vg=0,N1管一直關斷無效。

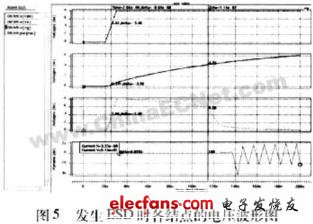

對上述例子中圖2結構的具體仿真見圖5、圖6。

?

?

從上述仿真分析及實際的ESD結果來看,該結構本身首先必須要有一定的健壯性,其自身的健壯性則與以下兩方面有關:

(1)該結構的邏輯設計,即各管子尺寸的設計,以保證該結構在正常上電時能完全關斷,使電路正常工作,當ESD發生時能有效開啟,從而保護內部結構。通常T=RC的值的設計要在100ns-1000ns之間,R可由倒比管或阱電阻實現,而C可直接由MOS電容構成,P0、N0管的寬長比W/L不用很大,其溝長比內部最小溝長稍大,該結構因為承受了ESD大電流泄放通道的任務,N1管的寬長比4W/L要比較大,在不影響面積的情況下盡可能大,管子溝長比內部最小溝長大。

?

(2)該結構的版圖設計非常關鍵,其設計不當就可能導致自身的損壞。特別是N1管子版圖設計,其漏區孔距柵要有一定距離,即有一定的壓艙(Ballast)電阻時電流開啟泄放更均勻。

3.2 具體設計及結果

上述例子中,主要是版圖的設計不當造成在ESD發生時自身結構的損壞。經過分析,對該版圖結構做了一些修改優化。

原因:針對上述理論分析及例子中實際的擊穿點,該結構在1000V即被擊穿的原因主要是N1管的漏區孔距柵的距離d太小所致,d=1.35μm;

目標:改動盡量少的版次達到全面提升該電路的ESD性能的目標;

方案:N1管的L修改為1.2μm,d修改為3μm,改動的版次為多晶版和孔版;

結果:I/O-VDD、I/O/-VSS、I/O-I/O模式下,最低的P95可達到2.50kV,P50、P51、P54、P57、P84可達2.8kV,其余的I/O在3.1kV時仍然通過;在VDD-VSS模式下,當ESD加+3.40kV時,VDD-VSS間短路,所以該模式下抗ESD電壓為3.1kV。

可見,通過修改優化VDD-VSS鉗位結構,其圖2結構自身的抗ESD健壯性大大增強,VDD-VSS的抗ESD能力提高到3kV以上,其余I/O也得到了進一步的提升,使該電路總體ESD性能提高到2.20kV以上,滿足了民品電路的ESD性能要求。要進一步提高該電路的ESD性能,需要對該結構繼續優化,如再增大N1管的漏區孔距柵的距離d及W/L等,其他I/O口的GGNMOS管也需要相應的優化修改,但其總面積可能會相應增加。

4 VDD-VSS兩種電壓鉗位結構的比較

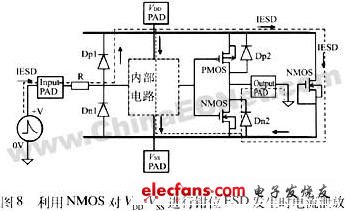

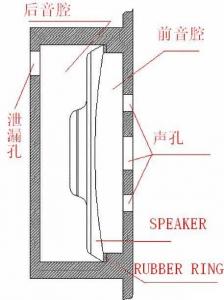

圖8為一種常見的全芯片ESD保護結構的設計,左邊為一個輸入PAD,右邊為一個輸出PAD,最右邊的NMOS管則是常規CMOS工藝電路中最常見的VDD-VSS電壓鉗位結構的設計。其設計要注意管子本身尺寸的邏輯設計,也要注意其版圖的詳細規則設計。它不屬于電壓檢測電路。在電路正常工作時,相當于一個反向二極管;當有ESD發生時,則NMOS管漏區的PN結反向擊穿,寄生的NPN導通從而泄放大電流并使VDD-VSS間的電壓鉗位。

圖9中最右邊的VDD-VSS電壓鉗位結構的設計則為一種ESD瞬態檢測電路,該電路一種詳細的設計方案即為圖2的結構設計。具體作用上面已經進行了詳細的分析闡述。主要是比較一下圖8、圖9兩種VDD-VSS電壓鉗位結構的優劣。

?

?

在ESD發生時,兩個結構對VDD-VSS都有電壓鉗位作用,關鍵是各自電流的泄放能力的差異。一般管子的正向導通比反向擊穿能力耐更高的ESD電壓,承受更大、更低阻抗的ESD電流,且ESD電流泄放更均勻。在亞微米CMOS IC中,VDD-VSS直接的GGNMOS大管可能不足以耐較高的ESD電壓,該結構更有利于ESD性能的提升,同時其版圖設計面積也更大。只有在亞微米以下的CMOS電路的設計中,才需要考慮。

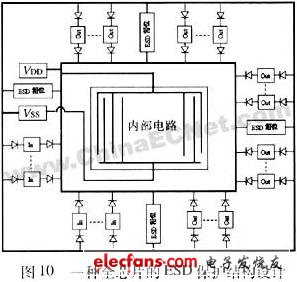

5 全芯片ESD保護結構的設計

如要進一步優化電路的抗ESD性能,需要從全芯片ESD保護結構的設計來進行考慮,在亞微米全芯片ESD保護結構的設計中,不僅要設計每個I/O對VDD、VSS直接的保護結構,以提供外圍直接的ESD低阻抗大電流泄放通道及對內部電壓鉗位,更要重點設計全芯片外圍VDD-VSS之間低阻抗大電流泄放通道及對內部VDD-VSS電壓的鉗位,如上述例子中若去掉圖2的結構,則I/O-VDD(VSS)的ESD性能下降許多,特別是對于面積較大、特征尺寸較小的電路,電源線、地線走線較長,則電路的不同位置電源線、地線對VDD、VSS根部有較大的電阻壓降,在VDDPAD上出現ESD脈沖時,距VDDPAD較遠的電源線上就有了一定的RC延遲,所以即使完全相同的ESD保護結構,由于每個I/O PAD距VDD、VSSPAD位置的不同,其ESD性能也不完全相同,離VDD、VSS近的I/O口ESD性能更好,反之較差,上述例子中優化改版后,有幾個管腳如P95、P51、P54等抗ESD變的更差就與其位置離VDD、VSS最遠有關,若在芯片的左下角再加一個VDD-VSS如圖2的保護結構,則全芯片的抗ESD性能會得到進一步的提高。

在全芯片的ESD結構設計時,注意以下關鍵幾點:

(1)外圍VDD、VSS走線盡可能寬,減小走線上的電阻;

(2)設計一種VDD-VSS之間的電壓鉗位結構,且在發生ESD時能提供VDD-VSS直接低阻抗電流泄放通道,如文章所述的結構。對于面積較大的電路,最好在芯片的四周各放置一個這樣的結構,若有可能,在芯片外圍放置多個VDD、VSSPAD,也可以增強整體電路的抗ESD能力;

(3)外圍保護結構的電源地的走線盡量與內部走線分開,外圍ESD保護結構盡量做到均勻設計,避免版圖設計上出現ESD薄膜環節;

(4)ESD保護結構的設計要在電路的ESD性能、芯片面積、保護結構對電路特性的影響如輸入信號完整性、電路速度、輸出驅動能力等進行平衡考慮設計,還需要考慮工藝的容差,使電路設計達到最優化。一個全芯片的ESD保護結構的設計見圖10。

?

在實際設計的一些電路中,如0.8μm以上的電路中,有時沒有直接的VDD-VSS電壓鉗位保護結構,此時,VDD-VSS之間的電壓鉗位及ESD電流泄放主要利用全芯片整個電路的阱與襯底的接觸空間。所以在外圍電路要盡可能多地增加阱與襯底的接觸,且N+P+的間距一致。若有空間,則最好在VDD、VSSPAD旁邊及四周增加VDD-VSS電壓鉗位保護結構,不僅增強了VDD-VSS模式下的抗ESD能力,也增強了I/O-I/O模式下的抗EESD能力,且自身的抗ESD能力要具有很強的健壯性,避免自身可能首先被ESD擊穿損壞從而成為全芯片的最薄弱環節。

6 總結

對于深亞微米超大規模CMOS IC的ESD結構設計,常規的ESD保護結構通常不再使用了,通常大多是深亞微米工藝的Foundry生產線都有自己的外圍標準的ESD結構提供,有嚴格標準的ESD結構設計規則等,設計廠商只需調用其結構就可以了,這可使芯片設計師把更多精力放在電路本身的功能、性能方面的設計等。

電子發燒友App

電子發燒友App

評論