8GB DDR3低電壓版內存也來了

相關推薦

完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表

電子發燒友網站提供《完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表.pdf》資料免費下載

2024-03-13 13:58:12 0

0

0

0適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩壓器數據表

電子發燒友網站提供《適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩壓器數據表.pdf》資料免費下載

2024-03-13 13:53:03 0

0

0

0英睿達在英亞上架12GB DDR5內存

該內存速度高達5600MT/s,并可同時兼容5200和4800 MT/s。據詳情頁介紹,其工作電壓僅為1.1V,相較于DDR4 3200內存,性能提升幅度為1.5倍,且將于本月底開始出貨。

2024-03-13 11:43:05 91

91

91

91具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表

電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表.pdf》資料免費下載

2024-03-13 11:24:34 0

0

0

0具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內存電源解決方案數據表

電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內存電源解決方案數據表.pdf》資料免費下載

2024-03-13 11:13:44 0

0

0

0完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表

電子發燒友網站提供《完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-03-13 10:16:45 0

0

0

0谷歌Pixel 8a手機預計將于今年面世,配置8GB內存及降頻版Tensor G3處理器?

此外,IT之家透露,谷歌預計在Pixel8a上沿用Pixel7a的8GB內存配置,同時計劃在已有128GB容量的基礎上再增加256GB版本。

2024-03-11 10:45:40 134

134

134

134iPhone 16 配備 8GB 內存,支持 Wi-Fi 6E

據分析師杰夫·普(Jeff Pu)公布的消息透露,即將來臨的新款iPhone 16及 iPhone 16 Plus均具備8GB運行內存,相比iPhone 15與iPhone 15 Plus搭載

2024-01-16 13:40:03 204

204

204

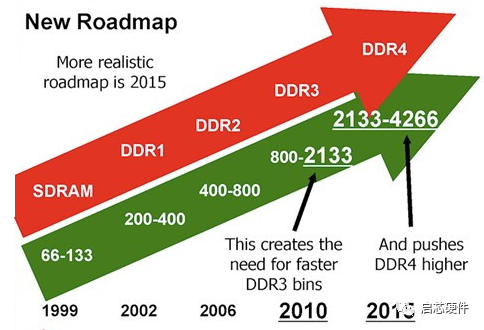

204DDR6和DDR5內存的區別有多大?怎么選擇更好?

的型號。 首先,我們來看一下DDR6內存。DDR6是目前市場上最新的內存技術,它在DDR5的基礎上進行了一些改進。DDR6內存的關鍵特點如下: 1. 帶寬更大:DDR6內存的帶寬比DDR5內存更大。DDR6內存的帶寬可以達到每秒14.4 GB,而DDR5內存的帶寬則為每秒12.8 GB。這意味著DDR6內存可

2024-01-12 16:43:05 2850

2850

2850

2850DDR5內存沖上8400MHz!DDR3L依然大行其道

硬件世界拉斯維加斯現場報道:CES 2024大展期間,雷克沙帶來了豐富的存儲方案,涵蓋SSD、內存、存儲卡等,包括頂級的PCIe 5.0 SSD、DDR5高頻內存。

2024-01-12 10:32:27 282

282

282

282

兆易創新:NOR Flash和SLC Nand Flash價格已趨于平穩

對于DRAM業務,這個公司的主要是低端市場,如小容量DDR4、DDR3等產品,且正在積極投入8Gb DDR4等新型DRAM研發,以便完善標準接口DRAM產品線,推動DRAM業務發展,滿足客戶需求。

2023-12-27 13:58:31 247

247

247

247可制造性案例│DDR內存芯片的PCB設計

)

DDR3內存條,240引腳(120針對每側)

DDR4內存條,288引腳(144針對每側)

DDR5內存條,288引腳(144針對每側)

DDR芯片引腳功能如下圖所示:

DDR數據線的分組

2023-12-25 14:02:58

可制造性案例│DDR內存芯片的PCB設計!

)

DDR3內存條,240引腳(120針對每側)

DDR4內存條,288引腳(144針對每側)

DDR5內存條,288引腳(144針對每側)

DDR芯片引腳功能如下圖所示:

DDR數據線的分組

2023-12-25 13:58:55

影馳20周年紀念版星曜DDR5-7200 24GB內存性能測試

影馳20周年紀念版星曜DDR5-7200 24GB內存采用了海力士M-Die顆粒,其超頻潛力可與SK海力士的A-Die顆粒相媲美。

即便頻率高達7200MHz,內存時序依舊被壓制在36-46-46-116 CR2,電壓則是1.4V。

2023-12-21 15:53:31 120

120

120

120

DDR3存儲廠迎漲價商機 華邦、鈺創、晶豪科等訂單涌進

法人方面解釋說:“標準型dram和nand目前由三星、sk hynix、美光等跨國企業主導,因此,中臺灣企業在半導體制造方面無法與之抗衡。”在ddr3 ddr3的情況下,臺灣制造企業表現出強勢。ddr3的價格也隨之上漲,給臺灣半導體企業帶來了很大的幫助。

2023-11-14 11:29:36 405

405

405

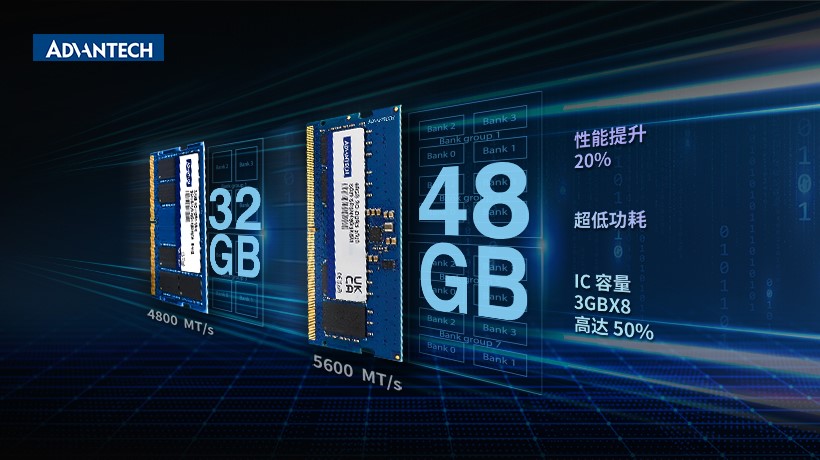

405高效邊緣計算解決方案:研華工業內存 SQRAM DDR5 5600 系列

? 研華推出 SQRAM DDR5 5600 系列工業內存。該系列緊跟計算機內存全新風潮,支持DDR5, 數據傳輸速度高達5600MT/s 。SQRAM 5600 系列的速度快如閃電,帶寬從 8GB

2023-11-02 16:26:56 537

537

537

537

DDR4和DDR3內存都有哪些區別?

DDR4和DDR3內存都有哪些區別? 隨著計算機的日益發展,內存也越來越重要。DDR3和DDR4是兩種用于計算機內存的標準。隨著DDR4內存的逐漸普及,更多的人開始對兩者有了更多的關注。 DDR3

2023-10-30 09:22:00 3885

3885

3885

3885闡述DDR3讀寫分離的方法

DDR3是2007年推出的,預計2022年DDR3的市場份額將降至8%或以下。但原理都是一樣的,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。

2023-10-18 16:03:56 516

516

516

516

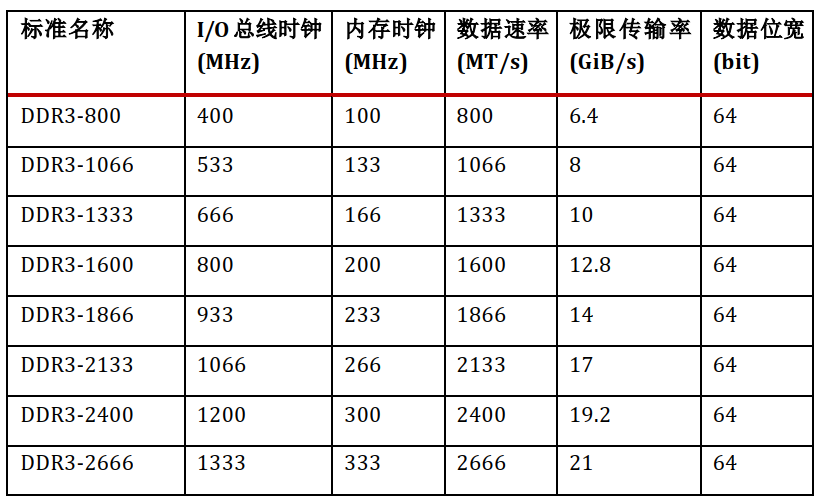

DDR3和DDR4的技術特性對比

摘要:本文將對DDR3和DDR4兩種內存技術進行詳細的比較,分析它們的技術特性、性能差異以及適用場景。通過對比這兩種內存技術,為讀者在購買和使用內存產品時提供參考依據。

2023-09-27 17:42:10 1088

1088

1088

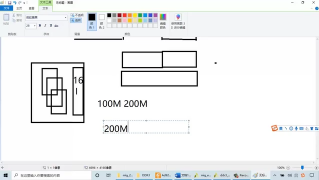

1088【紫光同創PGL50H】小眼睛科技盤古50K開發板試用體驗之測測DDR3

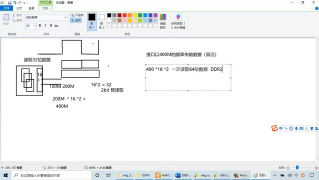

的時鐘周期,就可以完成DDR3的帶寬統計。

圖中顯示共消耗了1296026個時鐘周期,就是消耗了12960260ns,總計完成了32MB的數據寫入到DDR3中。

得到 32 * 8

2023-09-21 23:37:30

DDR4與DDR3的不同之處 DDR4設計與仿真案例

相對于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內存下部設計為中間稍微突出,邊緣變矮的形狀,在中央的高點和兩端的低點以平滑曲線過渡,這樣的設計可以保證金手指和內存插槽有足夠的接觸面

2023-09-19 14:49:44 1478

1478

1478

1478

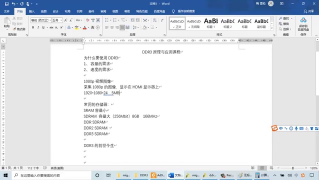

DDR3的規格書解讀

以MT41J128M型號為舉例:128Mbit=16Mbit*8banks 該DDR是個8bit的DDR3,每個bank的大小為16Mbit,一共有8個bank。

2023-09-15 15:30:09 629

629

629

629

XMP DDR5 8000內存性能測試詳解

在全默認設置的情況下,影馳HOF OC Lab幻跡S DDR5 8000內存的工作速率為DDR5 4800,延遲設定為40-40-40-76,因此在這個設置下它的內存性能并不突出,與普通的DDR5 4800內存相當。

2023-09-15 10:40:42 750

750

750

750

為什么DDR3/4不需要設置input delay呢?

內置校準: DDR3和DDR4控制器通常具有內置的校準機制,如ODT (On-Die Termination)、ZQ校準和DLL (Delay Locked Loop)。這些機制可以自動調整驅動和接收電路的特性,以優化信號完整性和時序。

2023-09-11 09:14:34 420

420

420

420【米爾-全志T113-S3開發板- 極致雙核A7國產處理器-試用體驗】初玩全志T113-S3開發板試跑最高頻率測試

。

核心板資源及參數核心板擴展信號底板外設接口資源軟件資源參數

名稱

配置

選配

處理器型號

T113-S3,2*Cortex-A7@1.2G

電源管理

分立電源

內存

內置128MB DDR3

2023-09-09 18:07:13

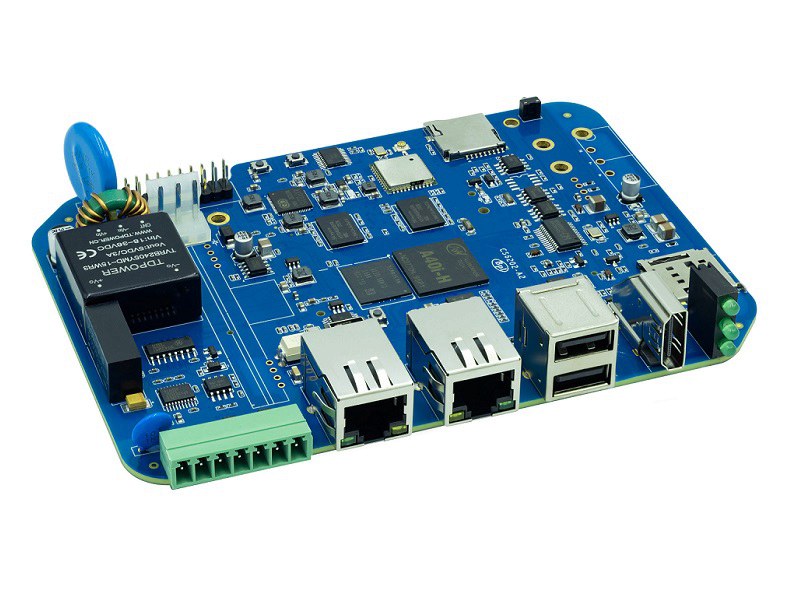

BananaPi BPI-6202工業控制板全志科技A40i、24V DC輸入、RS485接口

Banana Pi BPI-6202“嵌入式單板計算機”采用工業級全志A40i四核Cortex-A7處理器,工業溫度范圍和長生命周期,2GB DDR3,8GB eMMC閃存,M.2 SATA插槽等。

2023-09-04 09:38:17 493

493

493

493

Banana Pi BPI-6202工業控制板A40i、24V DC輸入、RS485接口

Banana Pi BPI-6202“嵌入式單板計算機”采用工業級全志A40i四核Cortex-A7處理器,工業溫度范圍和長生命周期,2GB DDR3,8GB eMMC閃存,M.2 SATA插槽等。

2023-09-04 09:25:46 366

366

366

366

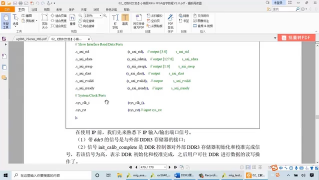

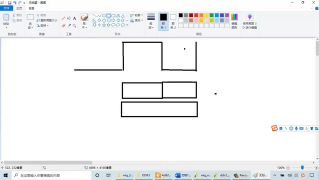

基于AXI總線的DDR3讀寫測試

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1887

1887

1887

1887

關于MCU200T的DDR3的配置和原理圖的問題

MCU200T的DDR3在官方給的如下圖兩份文件中都沒有詳細的介紹。

在introduction文件中只有簡略的如下圖的一句話的介紹

在schematic文件中也沒有明確表明每個接口的具體信息

2023-08-17 07:37:34

從里可以找到DDR200T的DDR3的配置和約束文件?

在配置DDR200T的DDR3時,一些關鍵參數的選擇在手冊中并沒有給出,以及.ucf引腳約束文件也沒有提供,請問這些信息應該從哪里得到?

2023-08-16 07:02:57

LightPulse HBA產品Line16Gb和8gb光纖通道HBA

電子發燒友網站提供《LightPulse HBA產品Line16Gb和8gb光纖通道HBA.pdf》資料免費下載

2023-08-15 10:29:04 0

0

0

0LightPulse LPe15004 8gb光纖通道HBAs

電子發燒友網站提供《LightPulse LPe15004 8gb光纖通道HBAs.pdf》資料免費下載

2023-08-15 10:15:46 0

0

0

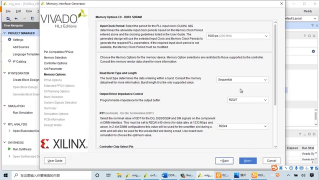

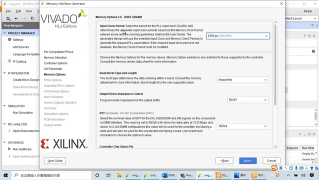

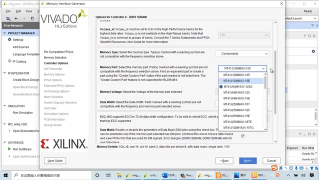

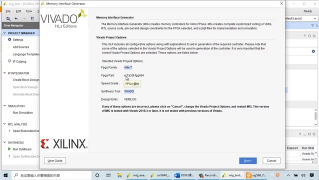

0DDR3緩存模塊仿真平臺構建步驟

復制Vivado工程路徑vivado_prj\at7.srcs\sources_1\ip\mig_7series_0下的mig_7series_0文件夾。粘貼到仿真路徑testbench\tb_ddr3_cache(新建用于DDR3仿真的文件夾)下。

2023-08-12 11:08:27 735

735

735

735ddr5的主板可以用ddr4內存嗎 幾代CPU才能上DDR5

DDR5的主板不支持使用DDR4內存。DDR5(第五代雙倍數據率)和DDR4(第四代雙倍數據率)是兩種不同規格的內存技術,它們在電氣特性和引腳布局上存在明顯差異。因此,DDR5內存模塊無法插入DDR4主板插槽中,也不兼容DDR4內存控制器。

2023-08-09 15:36:25 12792

12792

12792

12792Arm?CoreLink? DMC-620動態內存控制器技術參考手冊

以下內存設備:

?雙倍數據速率3(DDR3)SDRAM。

?低壓DDR3 SDRAM。

?雙倍數據速率4(DDR4)SDRAM。

2023-08-02 11:55:49

可制造性案例│DDR內存芯片的PCB設計

DDR是運行內存芯片,其運行頻率主要有100MHz、133MHz、166MHz三種,由于DDR內存具有雙倍速率傳輸數據的特性,因此在DDR內存的標識上采用了工作頻率×2的方法。 ? DDR芯片

2023-07-28 13:12:06 1877

1877

1877

1877

PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用

電子發燒友網站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用.pdf》資料免費下載

2023-07-24 09:50:47 0

0

0

0芝奇幻鋒戟Z5 RGB DDR5內存評測分析

今天我們測試的這款芝奇幻鋒戟Z5 RGB DDR5內存,在1.35V的電壓上就上到了7200MHz高頻,時序也控制在CL36-46-46-115 CR2,并且單條容量達到了24GB。

2023-06-26 10:39:41 869

869

869

869

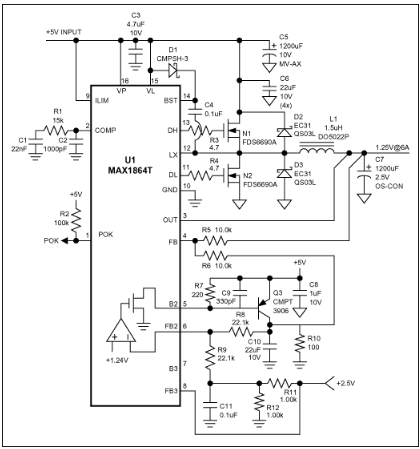

DDR內存終端電源

本設計筆記顯示了用于工作站和服務器的高速內存系統的雙倍數據速率 (DDR) 同步 DRAM (SDRAM)。使用MAX1864 xDSL/電纜調制解調器電源,電路產生等于并跟蹤VREF的終止電壓(VTT)。

2023-06-26 10:34:36 549

549

549

549

紫光同創FPGA入門指導:DDR3 讀寫——紫光盤古系列50K開發板實驗教程

解決方案,配置方式比較靈活,采用軟核實現 DDR memory 的控制,有如下特點:

?支持 DDR3

?支持 x8、x16 Memory Device

?最大位寬支持 32 bit

?支持裁剪的 AXI4

2023-05-31 17:45:39

使用帶有ECC芯片的4GB DDR3 RAM連接到T1040處理器DDR控制器,未能成功生成DDR地址奇偶校驗錯誤的原因?

我正在使用帶有 ECC 芯片的 4GB DDR3 RAM 連接到 T1040 處理器 DDR 控制器。

我嘗試了這個序列,但未能成功生成 DDR 地址奇偶校驗錯誤:

步驟1:

ERR_INT_EN

2023-05-31 06:13:03

紫光同創FPGA入門指導:DDR3 讀寫——紫光盤古系列50K開發板實驗教程

memory 控制器解決方案,配置方式比較靈活,采用軟核實現 DDR memory 的控制,有如下特點:

?支持 DDR3

?支持 x8、x16 Memory Device

?最大位寬支持 32 bit

2023-05-19 14:28:45

MT53E1G32D2是否已經過NXP在i.MX8QM上的驗證?

我有一塊使用基于 i.MX8QM MEK 板的 i.MX8QM 的板。我使用了 2 x MT53D512M32D2(總計 4GB DDR 內存)并且它可以正常工作。

現在我想把內存加倍到 8GB。我

2023-05-04 06:39:14

i.MX8M Plus卡住了的原因?

我們有一個帶有 DDR 8GB 的??定制板,并將調試端口從 UART2 更改為 UART3。我們在 SDK 5.10.72-2.2.0 和 5.15.32-2.0.0 上進行了移植,它們都運行良好

2023-04-19 08:41:02

純國產化 復旦微FMQL45T900開發板

DDR3,數據速率1066Mbps,32bitPL端內存:1GB DDR3,數據速率1600Mbps,32bitGTX收發器:16X速度等級:對標進口-2芯片級別:工業級工作溫度:-40℃-100

2023-04-13 16:04:38

ls1043a使用 (0-2GB) DDR 數據顯示不正確怎么解決?

社會:ls1043aDDR:MT40A2G8VA-062E:B,x5,4 個用于 8GB,1 個用于 ECC。我使用 CW 獲取配置文件: 我嘗試了兩個文件來生成 img他們都在 BL2 運行時遇到問題:使用 (0-2GB) DDR 數據顯示不正確:(寫入≠讀取) 我該如何解決?謝謝

2023-04-07 06:44:48

DDR SDRAM與SDRAM的區別

DDR內存1代已經淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 2867

2867

2867

2867

如何使用codewarrior生成的ddr代碼?

我們使用 10*MT40A1G16 獲得 16GB 內存,一個 ddr 控制器連接 8GB。三個問題:1)在codewarrior ddr config上,我們應該選擇什么dram類型?NoDimm

2023-04-03 07:24:21

UBOOT在硬件2GB RAM上顯示3GB RAM是怎么回事?

我使用 MSCale DDR 工具在基于 iMX8mq-evk 的定制板上進行 RAM 校準。Mscale DDR Tool RAM 顯示 RAM 的大小為 2GB(2GB 是正確的值)。然后我生成

2023-03-24 07:43:17

MSCALE_DDR_Tool使用iMX8M+定制板的LPDDR4壓力測試失敗的原因?

通過故障參考“DDR_imx8+_8GB”參考“Mscale_ddr_tool _v3.30”通過測試請參閱“LPDDR4_2000MHz_8GB”以獲取從 RPA excel for 8GB 內存生成

2023-03-24 06:54:09

電子發燒友App

電子發燒友App

評論