1 kOhms ±1% 芯片電阻 0202(0505 公制) 射頻,高頻率 厚膜

2024-03-14 21:40:29

50 Ohms ±2% 125W 芯片電阻 射頻,高頻率 厚膜

2024-03-14 20:42:31

公司有沒有穩(wěn)固的網(wǎng)絡系統(tǒng)?”來自一名金融類高頻交易員的疑問。 針對以上疑問,可想而知一個精準的時間對金融行業(yè)的重要性。選用北斗衛(wèi)星同步時鐘可以保證時間的精準交易的可靠性。 GP/GNSS 衛(wèi)星具有高精度的原子鐘,因此

2024-03-05 10:03:46 90

90

我有一個基于 4046 IC 的 VCO 電路,可產(chǎn)生隨輸入電壓變化的 TTL。

我想將這個變頻信號轉換為具有固定幅度(帶寬小于 1MHz)的正弦波。

我嘗試使用RC或LC濾波器,但是,振幅隨頻率

2024-03-01 09:07:18

detected on one of the USB endpoints. The event data will provide the endpoint number. 當高頻率發(fā)送hid數(shù)據(jù)出現(xiàn)此

2024-02-28 06:06:30

ADF4377BCCZ 具有集成壓控振蕩器(VCO)的整數(shù)N相控陣鎖定環(huán)路(PLL)非常適合數(shù)據(jù)轉換器和混合信號前端(MxFE)時鐘應用。該高性能PLL的優(yōu)點是?239 dBc/Hz、超低

2024-02-26 09:29:37

XG5032HAN晶體振蕩器通過其卓越的低抖動特性,為需要高頻率精度和穩(wěn)定性的電子設備提供了理想的解決方案。無論是在高性能的數(shù)據(jù)通信、精密測量XG5032HAN都能提供高質量、可靠的性能。同時,寬廣

2024-02-23 15:52:51 0

0 和低通濾波器進行解調制。總延遲時間由內部VCO時鐘頻率決定,用戶可以通過改變外部電阻來方便地改變VCO頻率。PT2399具有低失真(THD

2024-02-21 14:37:15 0

0 可以使用直流和交流耦合來提供。不僅限于JESD204B應用,14個輸出均可單獨配置為傳統(tǒng)高性能時鐘系統(tǒng)輸出。 超低噪聲時鐘抖動消除器SC6301具有高性能

2024-02-19 09:41:40

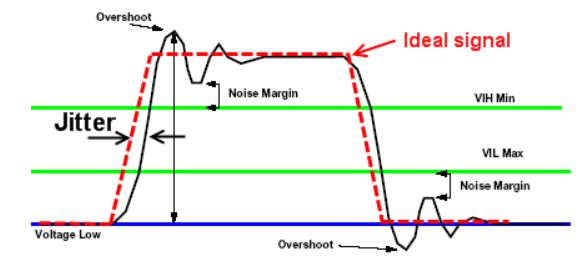

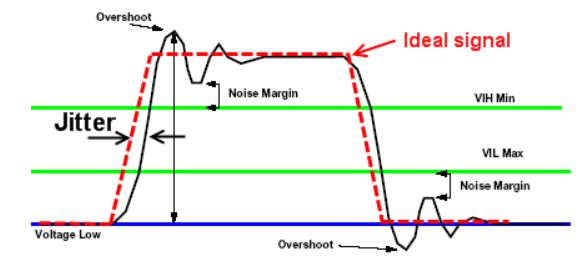

,通常低于 100 飛秒 (fs),以保持系統(tǒng)性能。這些時鐘還必須長期保持低抖動規(guī)格,且不受溫度和電壓的影響。 某些抖動是由信號路徑噪聲和失真引起的,使用重復時鐘和重定時技術可以在一定程度上減少抖動。不過,抖動也是由時鐘源產(chǎn)生的,時鐘源通常是振蕩器。這是由于各

2024-02-13 17:47:00 621

621

在ILLD看到使用20M晶振能夠達到200M,用40M晶振,可以達到400M,找不到最高頻率的,好心人給說下,謝謝了

2024-02-05 09:08:55

鎖相環(huán)中的壓控振蕩器的固定頻率是怎么確定的?是要和電網(wǎng)頻率一致嗎? 鎖相環(huán)(PLL)是一種常見的電路和控制系統(tǒng),廣泛應用于通信、信號處理、時鐘同步等領域。鎖相環(huán)中的壓控振蕩器(VCO)是其核心部件

2024-01-31 15:42:45 144

144 電子發(fā)燒友網(wǎng)站提供《毫微微時鐘網(wǎng)絡同步器、抖動衰減器和時鐘發(fā)生器RC32112A 數(shù)據(jù)表.pdf》資料免費下載

2024-01-31 10:09:17 0

0 基于MG7050 HAN的聲表差分多輸出晶體振蕩器(HCSL),采用兩路或四路差分HCSL(高速電流驅動邏輯)輸出,可以減少外部扇出緩沖區(qū),特別適用于需要超低抖動、高頻率范圍內穩(wěn)定工作的應用場

2024-01-29 15:37:22 0

0 相位抖動是從哪來的?通信中有哪些抖動? 相位抖動是指信號在傳輸過程中產(chǎn)生的相位變化,導致信號的相位偏離理想值的現(xiàn)象。它是由多種因素引起的,包括時鐘不準確、傳輸介質不穩(wěn)定、信號傳輸路徑不確定等。 時鐘

2024-01-25 15:29:28 171

171 會導致晶振的輸出頻率出現(xiàn)一定的不穩(wěn)定性,從而影響到系統(tǒng)的時鐘同步和信號處理。相位抖動常常以皮克-到-皮克的相位偏移量來衡量,通常以ps級別或fs級別來表示。相位抖動在通信系統(tǒng)、時鐘系統(tǒng)和高精度測量設備中都是非常重要

2024-01-25 13:51:07 126

126 云計算機、高性能計算機、nVME存儲、以太網(wǎng)絡及AI加速器應用。 原理方框圖典型特征◆符合PCIe 3.0◆PCIe 3.0相位抖動:0.48ps RMS(典型高頻)◆兼容LVDS輸出◆電源電壓為

2024-01-24 17:31:16

晶振頻率和時鐘頻率本質上有何區(qū)別呢?時鐘頻率有什么作用? 晶振頻率和時鐘頻率是兩個相關但又有所不同的概念。下面我們將逐一介紹這兩個概念的含義、區(qū)別和作用。 首先,我們來了解晶振頻率。晶振是一種

2024-01-24 16:11:35 307

307 EMC傳導高頻不過怎么改善? 電磁兼容性(EMC)是指不同電子設備在相互操作時,能夠互不干擾且不受外界電磁干擾的能力。在實際場景中,高頻傳導是EMC問題中常見的一種情況。本文將詳細介紹高頻傳導的原因

2024-01-23 13:53:03 1576

1576 ,包括時鐘抖動、噪聲抖動、跳變抖動和漂移抖動。 時鐘抖動是指時鐘信號在頻率和相位上的變化。時鐘信號是大多數(shù)電子系統(tǒng)中用于同步和定時的關鍵信號,其穩(wěn)定性對系統(tǒng)的性能有著重要影響。時鐘抖動會導致測量結果的不確定性

2024-01-19 15:01:31 253

253 飛秒 (fs))以保持系統(tǒng)性能。盡管溫度和電壓會發(fā)生變化,但它們還必須隨著時間的推移保持其低抖動規(guī)格。 一些抖動是由信號路徑噪聲和失真引起的,使用時鐘恢復和重定時技術可以在一定程度上減少抖動。然而,抖動也由時鐘源產(chǎn)生,時鐘源通常是一個振蕩器。這

2024-01-01 13:55:00 264

264

我是用萬用板做的電路.輸出高頻率的方波波形失真比較大.是不是采用萬用板的原因??,有經(jīng)驗的指點一下,如何解決.謝謝!

2023-12-25 07:46:47

小型化高頻率恒溫晶振是一款尺寸為25.4*25.4*12.7mm的高穩(wěn)定、高性價比OCXO。具有2E-10業(yè)內同級別最高的溫度穩(wěn)定性,日老化優(yōu)于0.2ppb/天性能;廣泛應用于基站、LTE、GSM

2023-12-22 11:02:38

注意哪些事項?次部分的參考地是否需進行與模擬/數(shù)字地進行一定的隔離處理?

疑問2:如果外部沒有高精度的時鐘源設備,是否有替代方案可以實現(xiàn)單端轉差分時鐘輸出?并且時鐘抖動質量可以在

2023-12-22 08:19:31

等應用已集成越來越多的PCIe終端,矽力杰新一代高性能PCIe時鐘緩沖器SQ82100可以為系統(tǒng)提供20路超低附加抖動的LP-HCSL參考時鐘,能夠簡化系統(tǒng)布局,進一步提高

2023-12-20 08:19:38 240

240

IC設計為什么需要仿真模擬?仿真模擬的重要性有哪些? IC設計(集成電路設計)是指利用EDA工具(電子設計自動化工具)設計出滿足特定功能和性能要求的集成電路芯片。仿真模擬是IC設計過程中至關重要

2023-12-19 11:35:38 850

850 晶振標稱頻率是什么?如何區(qū)分高頻率晶振和低頻率晶振? 晶振標稱頻率是指晶振器在設計和生產(chǎn)過程中設定的頻率,通常以赫茲(Hz)為單位表示。它表示了晶振器在正常工作條件下振蕩的頻率,也是晶振器用于計時

2023-12-18 14:30:52 373

373 同步整流芯片U7116是一款高頻率、高性能、CCM 同步整流開關,可以在 GaN 系統(tǒng)中替代肖特基整流二極管以提高系統(tǒng)效率。

2023-12-14 16:32:19 352

352 、引腳等。

3、信號輸出(白噪聲)。

通常來說,晶體振蕩器的相位噪聲在遠離中心頻率的頻率下有所改善。TCXO和OCXO振蕩器以及其它利用基波或諧波方式的晶體振蕩器具有最好的相位噪聲性能。采用鎖相環(huán)

2023-12-14 09:19:08

AC1571 是用于 5G 基站應用的基于 PLL的時鐘發(fā)生器,該芯片采用全數(shù)字鎖相環(huán)技術,以實現(xiàn)最佳的高頻低相噪性能,并具有低功耗和高PSRR能力。典型應用場景:· 無線基站·

2023-12-12 14:25:17

你好,我們在設計中需要使用 hmc7044 產(chǎn)生一系列頻率為 204MHz 且相位對齊的時鐘,并且所有的 204MHz 時鐘都由 外部VCO輸入時鐘 816MHz 所產(chǎn)生。

目前所有的時鐘都已經(jīng)獲取

2023-12-01 10:15:39

的時鐘發(fā)生器件的選擇上往往少有考慮。目前市場上有性能屬性大相徑庭的眾多時鐘發(fā)生器。然而,如果不慎重考慮時鐘發(fā)生器、相位噪聲和抖動性能,數(shù)據(jù)轉換器、動態(tài)范圍和線性度性能可能受到嚴重的影響。...

2023-11-28 14:33:57 0

0 電子發(fā)燒友網(wǎng)站提供《時鐘抖動對ADC性能有什么影響.pdf》資料免費下載

2023-11-28 10:24:10 1

1 電子發(fā)燒友網(wǎng)站提供《時鐘和頻率合成的應用領域.pdf》資料免費下載

2023-11-27 10:41:13 2

2 同步整流是一種電力變換技術,用于將交流電轉換為直流電。同步整流技術就是大大減少了開關電源輸出端的整流損耗,從而提高轉換效率,降低電源本身發(fā)熱。U7612同步整流ic是一款高頻率、高性能、CCM同步整流開關,可以在GaN系統(tǒng)中替代肖特基整流二極管以提高系統(tǒng)效率。典型應用于30W快充應用。

2023-11-15 09:38:55 272

272

STM32F103最高頻率是72Mhz,mm32F103最高主頻為96MHz。

2023-11-09 06:15:52

時鐘抖動是相對于理想時鐘沿實際時鐘存在不隨時間積累的、時而超前、時而滯后的偏移稱為時鐘抖動,簡稱抖動

2023-11-08 15:08:01 892

892

相位噪聲和抖動是對時鐘頻譜純度的兩種表述形式,一個是頻域一個是時域,從原理上來說,它們是等效的。

2023-10-30 16:02:46 686

686

頻率的比例決定了鎖定的頻率倍數(shù),因此對于VCO的頻率穩(wěn)定性要求比較高。 2. 延遲:VCO的輸出延遲對于PLL系統(tǒng)的工作非常重要。如果VCO的輸出延遲太大,則可能會導致鎖定時間變長或者無法鎖定。 3. 噪聲:VCO的輸出噪聲會影響PLL系統(tǒng)的性能和穩(wěn)定性。因此,要求VCO的輸出噪聲較

2023-10-30 10:46:44 358

358 電機驅動系統(tǒng)如何在提高頻率的同時抑制噪聲? 通過電機驅動系統(tǒng)在提高頻率的同時抑制噪聲是當今電力機械行業(yè)面臨的一個普遍問題。為了滿足客戶的要求,提高電機驅動的效率和可靠性,同時減少噪聲和振動,電機驅動

2023-10-29 16:23:53 555

555 至15V 這款高性能PLL可用于生成混頻器本振(LO)頻率或ADC/DAC時鐘,適用于微波點對點系統(tǒng)、測試和測量設備或汽車雷達中的應用。 本應用筆記

2023-10-28 14:45:41 6895

6895 能檢測較高頻率振動傳感器有哪些?震動頻率1hz到1000hz,不知道加速度陀螺儀能否勝任。

2023-10-27 06:41:38

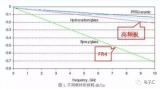

高頻板是指電磁頻率較高的特種線路板,用于高頻率(頻率大于300MHZ或者波長小于1米)與微波(頻率大于3GHZ或者波長小于0.1米)領域的PCB,是在微波基材覆銅板上利用普通剛性線路板制造方法的部分工序或者采用特殊處理方法而生產(chǎn)的電路板。一般來說,高頻板可定義為頻率在1GHz以上線路板。

2023-10-26 17:21:47 2357

2357

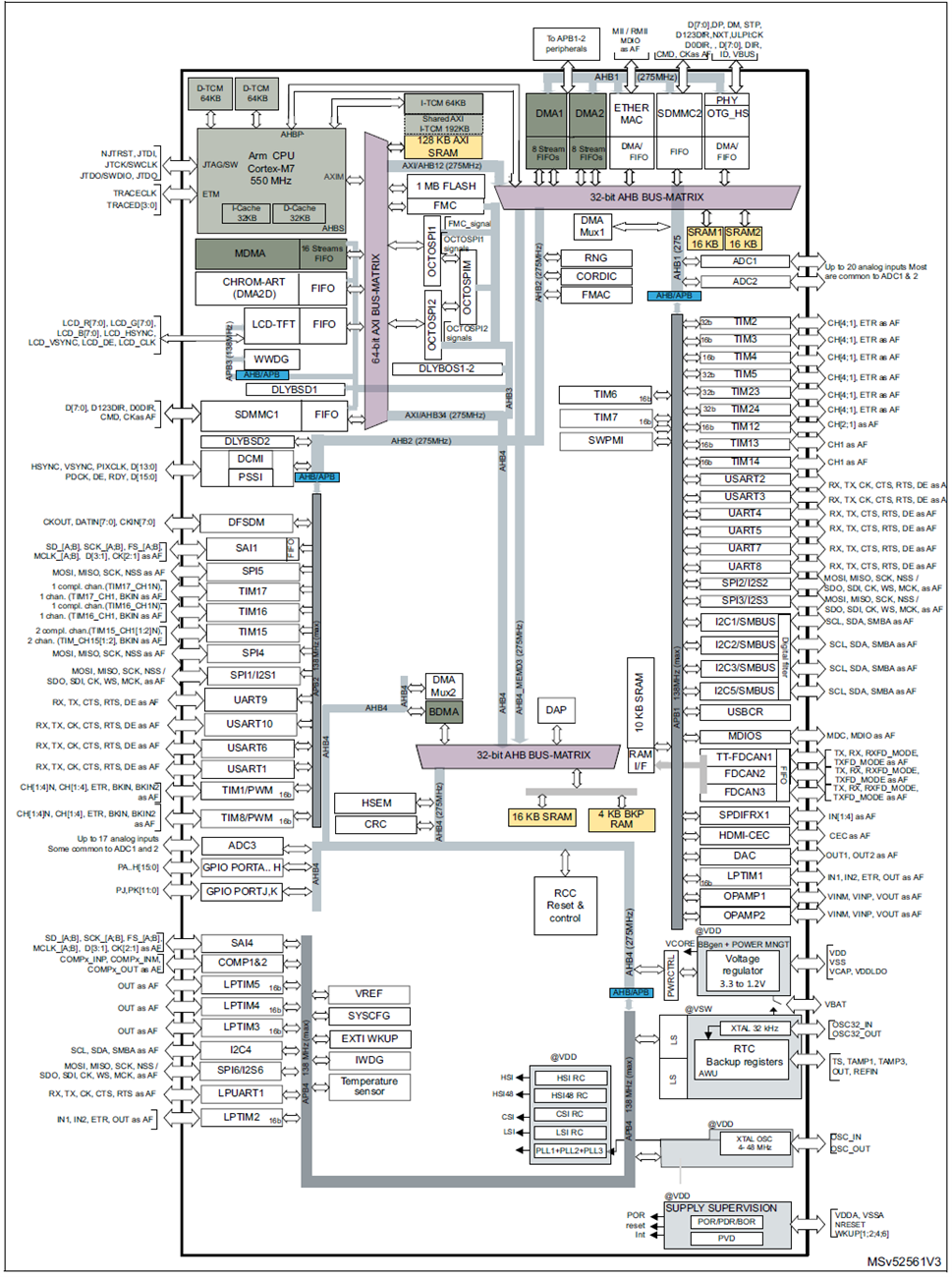

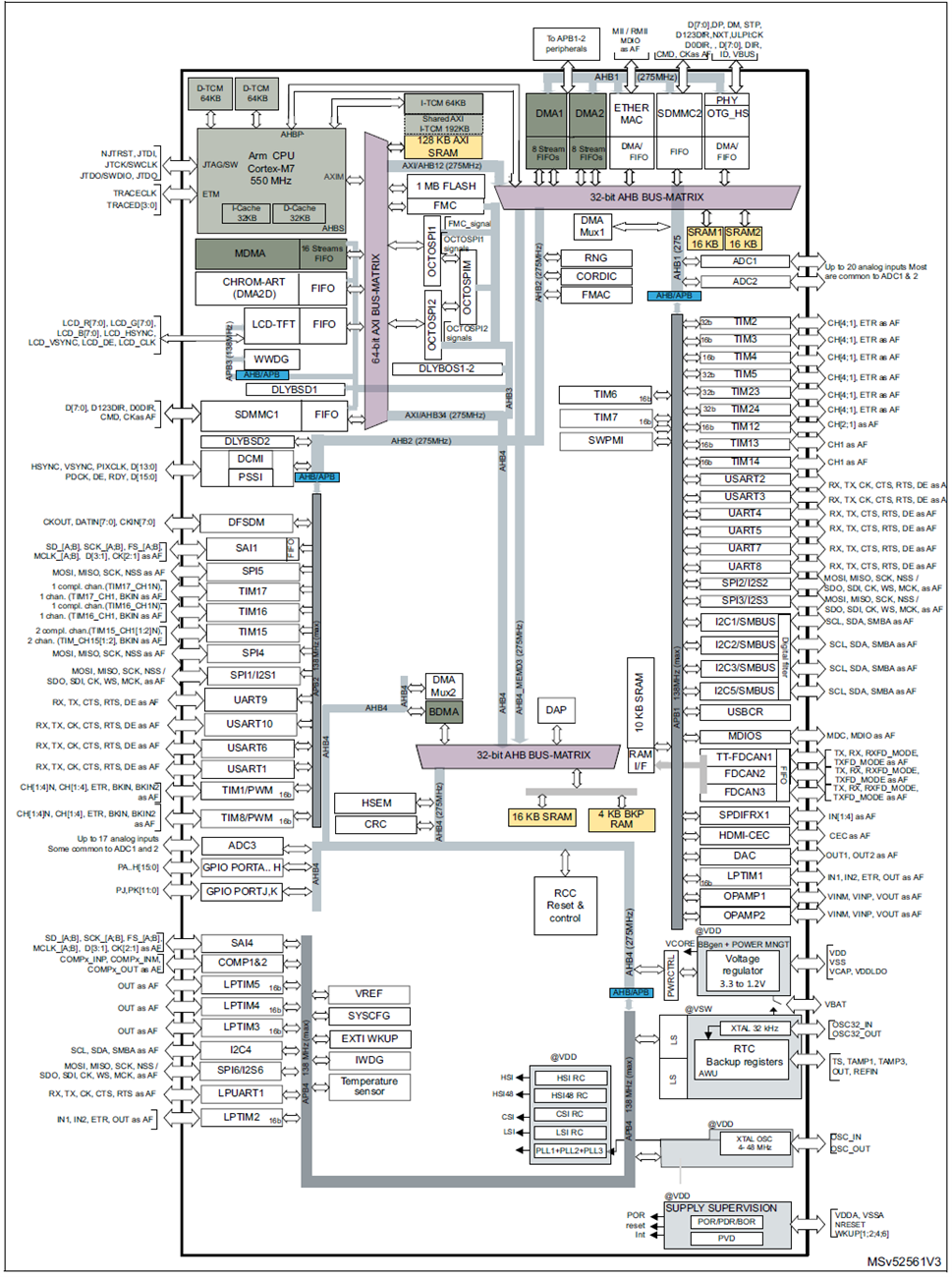

針對常規(guī)STM32系列性能測試所引起的準確度低、可靠性差、操作困難等問題,文中提出了一種關于I/O響應頻率以及定時器最高頻率的極限性能測試方法。通過對STM32H7時鐘頻率進行最高頻率配置,分別

2023-10-24 14:51:18 666

666

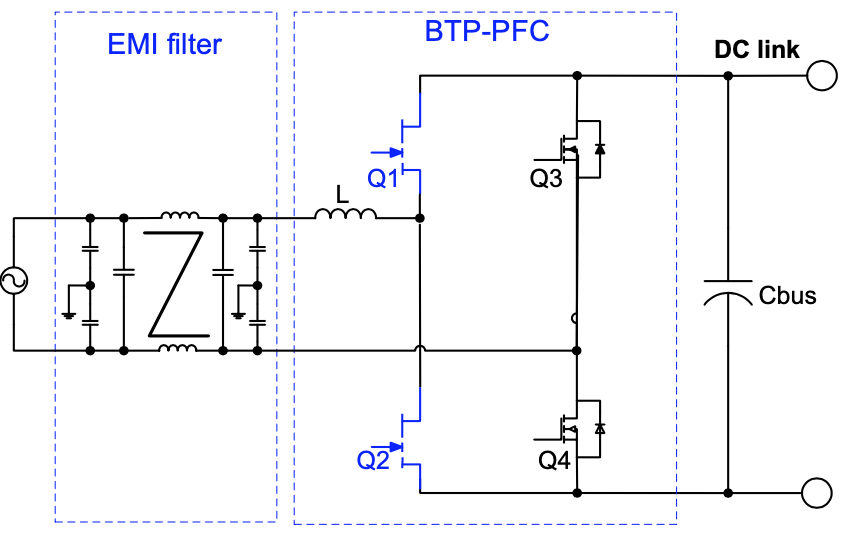

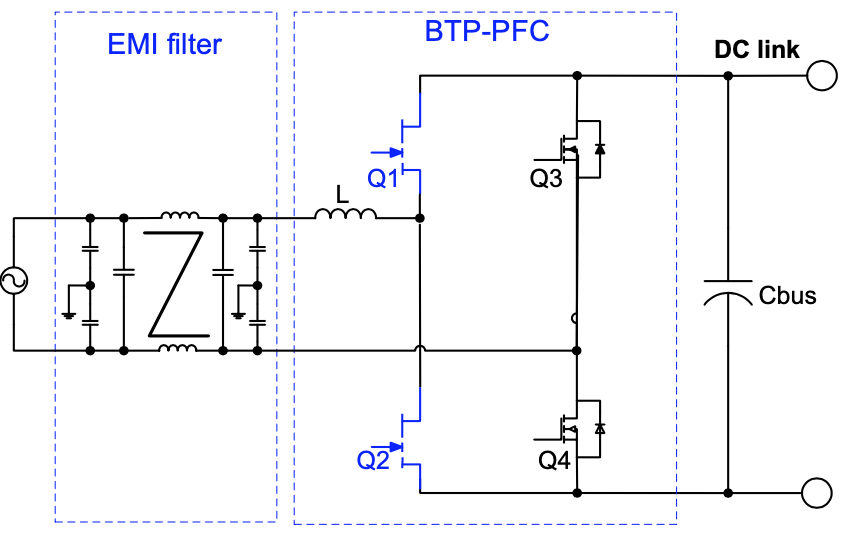

眾所周知,氮化鎵功率器件為電力電子系統(tǒng)提高頻率運行,實現(xiàn)高功率密度和高效率帶來可能。然而,在高頻下需要對EMI性能進行評估以滿足EMC法規(guī)(例如EN55022 B類標準)要求。

2023-10-16 14:32:45 1139

1139

at89c51的io輸出pwm,級數(shù)256級,用定時器實現(xiàn)那么它的最高頻率能到多少

2023-10-08 07:16:15

如果時鐘是12mhz輸入的話,那么捕獲可以多高頻率

2023-09-25 07:10:57

如果供電是3.6v,不考慮其他因素,能工作的最高頻率是多少

2023-09-22 06:27:35

在之前的 IC 設計中,關注的參數(shù)主要是性能(timing)和面積(area)。 EDA 工具在滿足性能要求的情況下,最小化面積。功耗是一個不怎么關心的問題。 CMOS 工藝在相對較低的時鐘頻率下

2023-09-21 07:38:14

在芯片設計中,為了便于定位故障,有時候需要確認部分時鐘頻率是否正確,需要部分debug手段。常見的方式是:將時鐘信號引到芯片管腳,通過儀器測量。這類方式必須要測量儀器,并且需要熟練使用,耗時較長。還有一種簡單的方式,通過時鐘計數(shù)的方式判斷時鐘頻率是否正確。

2023-09-20 14:17:06 384

384

太赫茲頻率范圍和甚高頻率的區(qū)別? 太赫茲頻率范圍和甚高頻率(SHF)是電子工程中兩個重要而又有區(qū)別的概念。在電磁波譜中,太赫茲頻率范圍介于毫米波和紅外線之間,主要集中在0.1-10 THz范圍內

2023-09-19 17:49:56 565

565 高頻率的測試需求,并增加全新的“模擬特征分析”功能,通過圖形快速分析元器件的好壞。R2 可手動操作使源阻抗從100Ω切換到1.4kΩ,提高了低電阻測量的穩(wěn)定性。為

2023-09-17 21:05:43

時鐘分頻電路通過將輸入的高頻時鐘信號分頻,生成較低頻率的時鐘信號。它通常基于計數(shù)器和邏輯門實現(xiàn),用于將高頻時鐘信號分解成系統(tǒng)所需的各種頻率。

2023-09-14 14:53:57 4881

4881 如何確定濾波器共模插損的最高頻率? 濾波器是一種通信系統(tǒng)中常用的電路元件,它可以濾除信號中不需要的頻率成分,使得信號只包含期望的頻率成分,在電路系統(tǒng)中有非常廣泛的運用。 在濾波器

2023-09-12 11:50:09 322

322 的濾波器是非常重要的,因為過濾頻率對電器設備的性能和安全性有直接影響。因此,本文將深入探討如何依據(jù)電源線共模騷擾的最高頻率來選擇濾波器插損的最高頻率。 1. 理解電源線共模騷擾 電源線共模騷擾是由于電力系統(tǒng)中所產(chǎn)生的

2023-09-12 11:48:05 426

426 時鐘抖動技術適合于各種周期性的脈沖信號,典型的是電力電子設備中的PWM電壓和數(shù)字電路中的時鐘信號。

2023-09-11 10:55:34 502

502

同步整流芯片U7612是一款高頻率、高性能、CCM 同步整流開關,可以在GaN系統(tǒng)中替代肖特基整流二極管以提高系統(tǒng)效率。

2023-09-06 15:54:13 910

910 高頻變壓器頻率對電壓的影響? 高頻變壓器是近年來越來越廣泛使用于電子工業(yè)的一種電子元件。它是由磁性材料、繞組及鐵芯組成,用來實現(xiàn)電壓變換、隔離、阻抗匹配和電能傳遞的器件。與低頻變壓器相比,高頻變壓器

2023-09-04 17:23:44 1307

1307 數(shù)字頻率和模擬頻率的關系 數(shù)字頻率和模擬頻率是電子領域中經(jīng)常涉及到的兩個概念。這兩個概念雖然有所相似,但在實際應用中又有所不同。數(shù)字頻率以數(shù)字化信號為主要參考,而模擬頻率則以連續(xù)變化的模擬

2023-08-27 15:37:02 4185

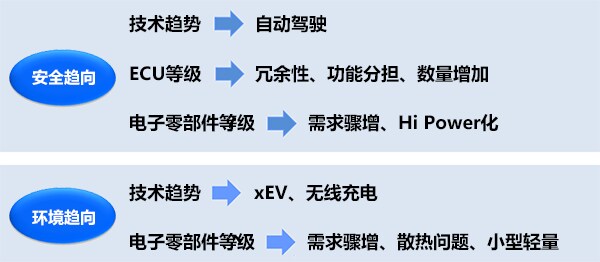

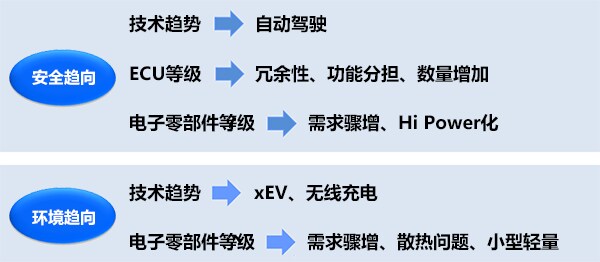

4185 車載可降低故障風險的高可靠性高頻率功率電感器方案。 目次 汽車電子的動向 車載零部件要求的環(huán)境的變化 針對各種ECU分別提出最佳解決方案 高可靠性車載用高頻率功率電感器的產(chǎn)品概述 高可靠性車載用高頻率功率電感器的產(chǎn)品概要、

2023-08-22 16:26:24 371

371

基于FPGA的高頻時鐘的分頻和分頻設計

2023-08-16 11:42:47 0

0 電子發(fā)燒友網(wǎng)站提供《PI6C5913004最低輸出抖動緩沖器IC 確保40GE/100GE設計性能.pdf》資料免費下載

2023-07-25 14:45:10 0

0 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現(xiàn)效果;如果使用不當,不但會影響設計的工作頻率和穩(wěn)定性等,甚至會導致設計的綜合、實現(xiàn)過程出錯

2023-07-24 11:07:04 655

655

本文主要介紹了時鐘偏差和時鐘抖動。

2023-07-04 14:38:28 959

959

在電磁兼容的輻射發(fā)射測試中,最常見的就是時鐘輻射超標,隨著系統(tǒng)設計復雜性和集成度的大規(guī)模提高,電子系統(tǒng)的時鐘頻率越來越高,處理的難度也越來越大。時鐘輻射的癥結在于,時鐘信號對應的頻域為窄帶頻譜,能量

2023-06-27 14:45:22 649

649

、氧化鋯等陶瓷材料為基板,通過特殊工藝制作而成的,具有耐高溫、高頻率、高穩(wěn)定性等特點,是高頻電路設計中不可替代的材料之一。

2023-06-19 16:45:58 670

670 ,經(jīng)過內部的PLL倍頻為較高頻率,F(xiàn)PGA需要25M或一下的時鐘輸入。

我的問題是DSP和FPGA的時鐘信號如何產(chǎn)生?

2023-06-19 06:43:17

橋式拓撲結構中放大了氮化鎵的頻率、密度和效率優(yōu)勢,如主動有源鉗位反激式(ACF)、圖騰柱PFC 和 LLC(CrCM 工作模式)。隨著硬開關拓撲結構向軟開關拓撲結構的轉變,初級 FET 的一般損耗方程可以被最小化。更新后的簡單方程使效率在 10 倍的高頻率下得到改善。

2023-06-15 15:35:02

先來聊一聊什么是時鐘抖動。時鐘抖動實際上是相比于理想時鐘的時鐘邊沿位置,實際時鐘的時鐘邊沿的偏差,偏差越大,抖動越大。實際上,時鐘源例如PLL是無法產(chǎn)生一個絕對干凈的時鐘。這就意味著時鐘邊沿出現(xiàn)在

2023-06-09 09:40:50 1121

1121

高性能的時鐘器件是高帶寬、高速率、高算力、大模型的基礎。核芯互聯(lián)近日推出面向下一代數(shù)據(jù)中心應用的超低抖動全新20路LP-HCSL差分時鐘緩沖器CLB2000,其業(yè)界領先的附加抖動性能遠超PCIe Gen 5和PCIe Gen 6的標準。

2023-06-08 15:29:55 805

805

如何改變spi的時鐘頻率? 改變SPI的時鐘頻率需要以下步驟: 1. 選擇合適的時鐘源和分頻器:SPI接口的時鐘源可以是內部時鐘或外部時鐘,需要根據(jù)具體情況選擇;同時需要根據(jù)所需的SPI時鐘頻率

2023-06-03 16:36:02 2126

2126 高頻響應壓力變送器的種類很多,其中應用最早的是磁致伸縮爆震傳感器,主要由磁芯、永磁體和感應線圈組成。高頻響應壓力變送器的作用是測量發(fā)動機抖動的程度,在發(fā)動機爆震時調整點火提前角。下面將介紹高頻響應壓力變送器的工作原理、工作頻率、安裝位置及故障維修。

2023-06-03 10:31:05 488

488

和大俠簡單聊一聊數(shù)字電路設計中的抖動,話不多說,上貨。

既然說到了抖動,那么什么是抖動?那首先我們就來了解一下什么是抖動。

一、抖動的幾個重要概念

1、抖動的基本概

在理想情況下,一個頻率固定

2023-06-02 17:53:10

首先,我們需要理解什么是時鐘抖動。簡而言之,時鐘抖動(Jitter)反映的是時鐘源在時鐘邊沿的不確定性(Clock Uncertainty)。

2023-06-02 09:09:06 1020

1020

我們使用 RFID IC NXP MFRC 500-01T PACKAGE SOIC-32,我想要 MFRC 500-01T 的替代推薦 IC。

2023-05-30 13:23:41

) 以及其他通常要求時域抖動規(guī)范(如周期)的應用生成時鐘- 周期和周期抖動。 然而,對于串行解串器 (SerDes)、千兆以太網(wǎng) (GbE)、10 GbE、同步光網(wǎng)絡/同步數(shù)字體系 (SONET/SDH) 和光纖通道等高速接口,情況就不同了。有嚴格的頻域抖動要求。 為了正常運行,這些高速接口依賴于低頻

2023-05-26 22:15:02 1385

1385 無線通信系統(tǒng)需要采用較高頻率的信號的原因是什么?

2023-05-10 17:14:16

PD/QC快充電源ic U6648具有±5%的隨機頻率抖動功能,開關頻率抖動分散了諧波擾動能量,獲得良好的EMI特性。

2023-05-08 10:53:03 259

259 隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設計越來越多。在調試這些FPGA樣機時,需要從寫代碼時就要小心謹慎,否則寫出來的代碼可能無法滿足時序要求。

2023-05-06 09:33:27 773

773

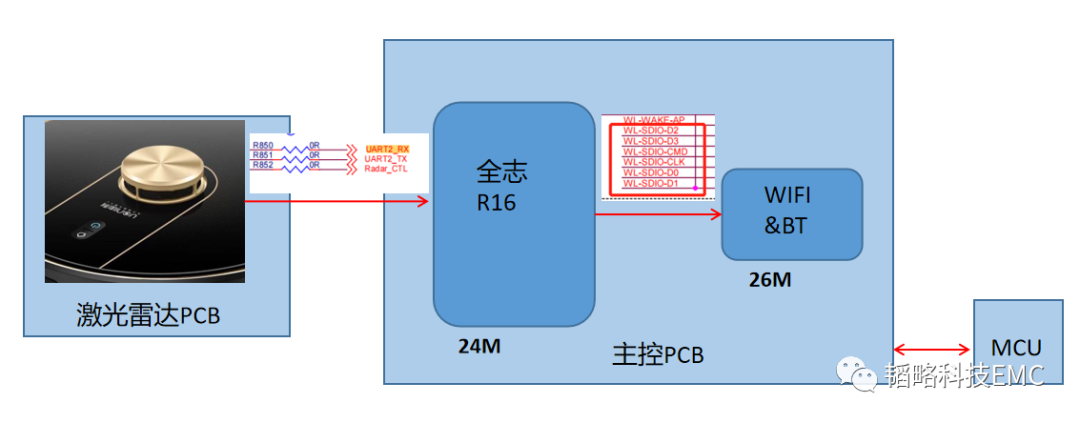

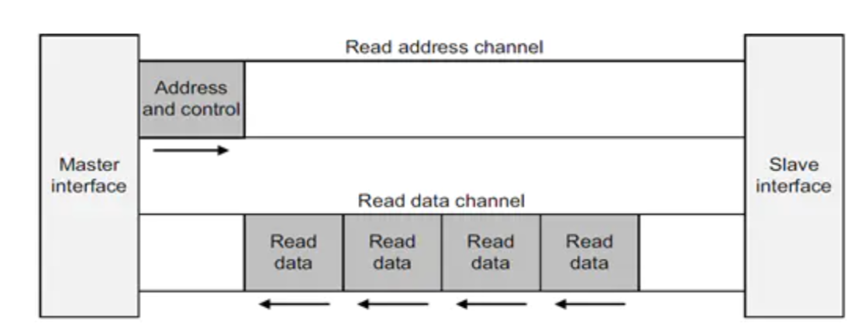

AMBA AXI協(xié)議支持用于主從模塊之間通信的高性能、高頻率系統(tǒng)設計。

2023-05-04 14:35:14 1246

1246

當鎖相環(huán)達到鎖定狀態(tài)時,VCO輸出頻率與參考頻率相等(假設沒有分頻),那么它們的相位是不是相等呢?還是保持恒定的相位差呢?如果是相位相等,那么是怎么使它們的初相相等的呢?如果是保持恒定的相位差,那么

2023-04-24 11:32:51

鑒頻鑒相器,當兩輸入信號頻率相同但相位不同的時候,有電壓差輸出,然后去控制VCO,改變反饋信號頻率。這不是導致兩輸入頻率不同了,這如何鎖住相位啊,使VCO的頻率等于參考信號的頻率?求高人指點。

2023-04-24 10:23:02

) 頻帶內和頻帶外 (VCO) 噪聲的影響。基準時鐘發(fā)生器的相位噪聲性能需要在PLL環(huán)路帶寬內和帶寬外都表現(xiàn)得很出色,以符合更加嚴格的抖動技術規(guī)格要求。

2023-04-17 10:37:30 357

357

展頻IC在4M時鐘上的應用

2023-04-14 10:12:27 0

0 需要保護模擬輸出的瞬態(tài)過電與其產(chǎn)生的低壓(<24V)和低頻率(<10kHz)信號差異巨大。工業(yè)瞬態(tài)過電為高壓(高達15kV)、高頻率(通常時間短于100ns)。您的電路應當利用這些差別提供保護,同時不影響模擬輸出的信號質量。

2023-04-13 09:23:46 564

564

本文討論電源噪聲干擾對基于PLL的時鐘發(fā)生器的影響,并介紹幾種用于評估由此產(chǎn)生的確定性抖動(DJ)的測量技術。派生關系顯示了如何使用頻域雜散測量來評估時序抖動行為。實驗室臺架測試結果用于比較測量技術,并演示如何可靠地評估參考時鐘發(fā)生器的電源噪聲抑制(PSNR)性能。

2023-04-11 11:06:39 810

810

模擬電路大佬,關于差分電路+環(huán)形振蕩器結構,對比兩種結構是否能夠提高頻率!!!圖一為原電路,圖二為改良電路。

2023-04-08 21:24:03

系統(tǒng)時序設計中對時鐘信號的要求是非常嚴格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準。但實際中時鐘信號往往不可能總是那么完美,會出現(xiàn)抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 1633

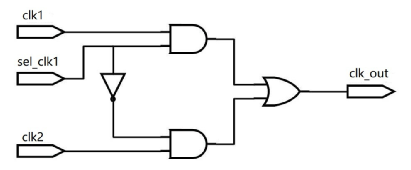

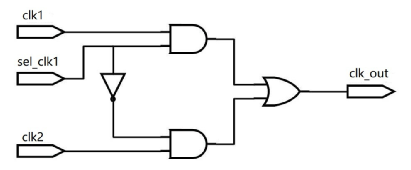

1633 隨著各種應用場景的限制,芯片在運行時往往需要在不同的應用下切換不同的時鐘源,例如低功耗和高性能模式就分別需要低頻率和高頻率的時鐘。兩個時鐘源有可能是同源且頻率比呈倍數(shù)關系,也有可能是不相關的。直接使用選擇邏輯進行時鐘切換大概率會導致分頻時鐘信號出現(xiàn)毛刺現(xiàn)象,所以時鐘切換邏輯也需要進行特殊的處理。

2023-03-29 11:41:29 908

908

過濾器高頻率 2200PF 0805

2023-03-28 15:00:04

抖動和相位噪聲是晶振的非常重要指標,本文主要從抖動和相位噪聲定義及原理出發(fā),闡述其在不同場景下對數(shù)字系統(tǒng)、高速串行接口、數(shù)據(jù)轉換器和射頻系統(tǒng)的影響。

2023-03-26 09:09:11 693

693

電子發(fā)燒友App

電子發(fā)燒友App

評論