要滿足苛刻的頻率合成器要求,通常需要做到一定程度的設(shè)計靈活性。基本的鎖相環(huán)(PLL)頻率合成器能以低成本、高空間效率、低功耗封裝提供合理的頻譜純度和頻率捷變,因此它在射頻(RF)系統(tǒng)核心位置發(fā)揮作用

2022-10-14 10:30:36 2025

2025 ,這是為了支持掃頻而引入的。利用第二個累加器來提供一個穩(wěn)定增加的變量。先進DDS可將該變量增加到基本頻率調(diào)諧字上,從而獲得一個頻率穩(wěn)定變化的信號。也可以將其與POW結(jié)合以實現(xiàn)相位掃描。或者將其與ASF結(jié)合

2018-08-01 07:29:23

本文由ADI時鐘和信號部市場經(jīng)理JLKeip撰寫 在上篇內(nèi)容 DDS or PLL? 中承諾,我會對DDS/PLL優(yōu)勢對比表的一些微妙之處做一個評述。 這里先談?wù)勎艺J為更適合DDS的一些特點。 頻率

2019-01-18 13:19:36

本文由ADI時鐘和信號部市場經(jīng)理JLKeip撰寫在上篇內(nèi)容 DDS or PLL? 中承諾,我會對DDS/PLL優(yōu)勢對比表的一些微妙之處做一個評述。 這里先談?wù)勎艺J為更適合DDS的一些特點。頻率

2018-10-11 11:15:23

合成一個正弦信號,那么了解一點直接數(shù)字式頻率合成器(Direct Digital Synthesizer,DDS)會有助于您確定最佳解決方案哦~ 多數(shù)工程師在求學時接觸過鎖相環(huán)(PLL),但DDS不是

2019-02-13 11:54:20

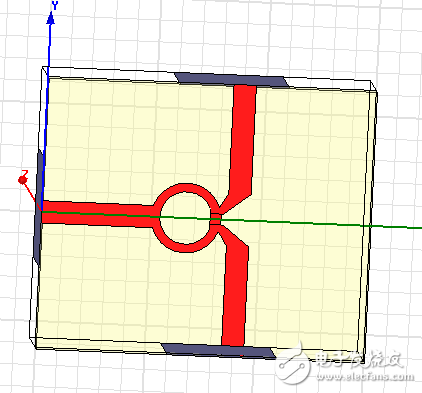

Ka波段E面和H面90°彎接頭的設(shè)計

2010-09-08 17:41:55

幾何尺寸縮小,這一差距也會縮小,但規(guī)模經(jīng)濟也會導致其縮小。PLL使用更廣泛,生產(chǎn)規(guī)模要大得多,有助于改善成本結(jié)構(gòu)。如果是針對大規(guī)模應(yīng)用,并且DDS方案有一些優(yōu)勢,那么在價格上應(yīng)該有一定的協(xié)商空間。寬頻

2018-10-31 10:57:30

設(shè)備量大,導致體積大、成本高。DDS+PLL合成方式包括DDS激勵PLL的方式、DDS內(nèi)插入PLL做分頻器以及DDS與PLL混頻的方式。DDS激勵PLL做分頻器的方式由于DDS最大輸出頻率不高,需要多次

2019-06-21 06:32:34

資料下載。希望大家喜歡哦! 本講義涉及以下主題內(nèi)容五種類型的頻率合成什么是時鐘? 常用頻率是多少?鎖相環(huán)(PLL)基本模型鑒頻鑒相器(PFD) 驅(qū)動電荷泵(CP)數(shù)字PLL框圖 —— 分頻器PLL中輸入

2018-10-26 09:16:36

FPGA實現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法介紹了利用現(xiàn)場可編程邏輯門陣列FPGA實現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點介紹了DDS技術(shù)在FPGA中的實現(xiàn)

2012-08-11 18:10:11

【作者】:潘曉艷;【來源】:《信息與電子工程》2010年01期【摘要】:介紹一種模塊化的L波段細步進捷變頻頻率綜合器,采用直接數(shù)字頻率合成器實現(xiàn)細步進,采用上變頻器+倍頻器來提高并擴展帶寬。討論其

2010-04-22 11:47:59

TGA4508 Ka波段低噪聲放大器重要參數(shù)頻率范圍:30-42GHz增益 :21dB噪聲系數(shù) :2.8dB適用于VSAT 和 電子戰(zhàn) 項目TGA2595 Ka波段功率放大器重要參數(shù)頻率范圍

2020-05-29 08:55:33

`上海迦美信息通訊技術(shù)有限公司PLL/頻率綜合器15K-30K上海1-3年碩士及以上全職職位誘惑: 年底三薪,員工旅游,定期體檢,餐飲補貼 職位描述:崗位職責:1.PLL及相關(guān)電路模塊設(shè)計,如LC

2016-01-07 11:01:43

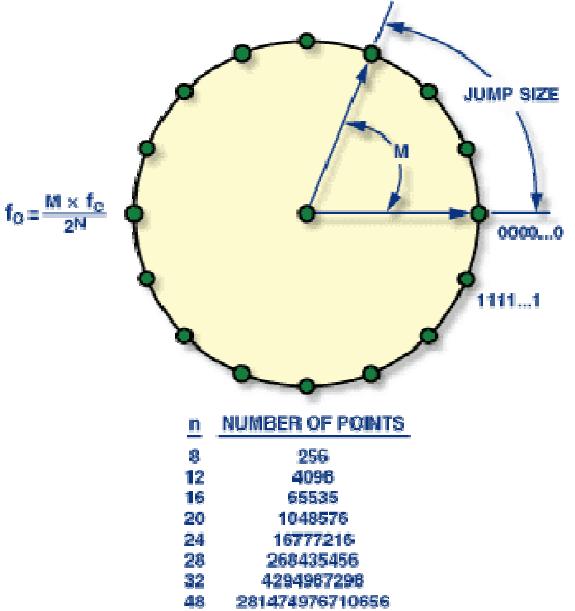

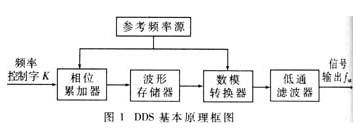

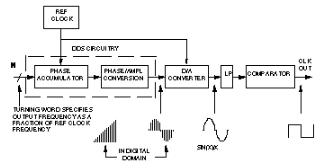

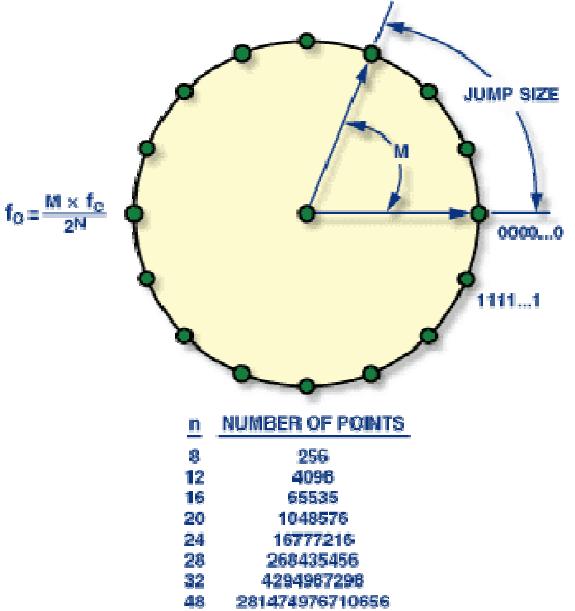

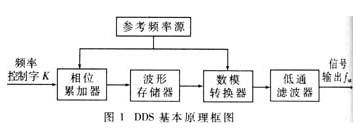

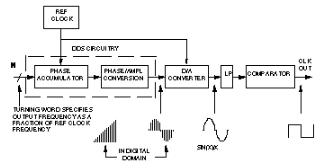

的設(shè)計方案。 1 DDS的結(jié)構(gòu)及工作原理 DDS的基本結(jié)構(gòu)由參考時鐘、相位累加器、ROM、DAC(數(shù)模轉(zhuǎn)換器)和LPF(低通濾波器)組成,見圖1。 DDS的工作原理是:在參考時鐘fr的控制下,頻率

2011-07-16 09:09:54

變化的敏感; A型我電荷泵的PLL頻率合成器是在這項工作中提出。閉環(huán)系統(tǒng)的穩(wěn)定是實現(xiàn)使用一個離散時間環(huán)路濾波器。 I型系統(tǒng)架構(gòu)導致開關(guān)速度快。離散時間環(huán)路濾波器的相位/頻率檢測器和VCO調(diào)諧節(jié)點之間的隔離。因此性能可以達到一個良好的刺激。PLL博士論文_全集成頻率綜合器[hide][/hide]

2011-12-15 11:17:56

請教有經(jīng)驗的射頻工程師,采用DDS+PLL的方式設(shè)計雷達發(fā)射源,要求發(fā)射信號為26GHz單頻連續(xù)波信號以及三角形LFMCW信號,25.5GHz~26.5GHz,調(diào)制周期2ms,通過單片機控制波形切換,請推薦DDS和PLL芯片型號,以及晶振的選擇,十分感謝

2018-10-09 17:39:06

直接數(shù)字頻率合成(DDS)在過去十年受到了頻率合成器設(shè)計工程師極大的歡迎,它被認為是一種具有低相位噪聲和優(yōu)良雜散性能的靈活的頻率源,基于DDS的頻率合成器在許多應(yīng)用中能比基于鎖相環(huán)(PLL)頻率

2019-07-08 07:26:17

的重要部件。基于矩形波導的功率分配/合成網(wǎng)絡(luò)由于本身低損耗、應(yīng)用頻率高的特點成為研究人員的研究重點。在毫米波段,對于二進制功率分配波導單元結(jié)構(gòu)多采用3-dB 波導E-面分支結(jié)構(gòu),該波導分支結(jié)構(gòu)具有

2019-06-19 06:26:05

GSPS轉(zhuǎn)換器是當下熱門,其優(yōu)勢在于既能縮短RF信號鏈,又能在FPGA中創(chuàng)建更多資源結(jié)構(gòu)以供使用,例如:減少前端的下變頻以及后級的數(shù)字下變頻器 (DDC)。但相當多的應(yīng)用仍然需要高頻率的原始模擬帶寬

2019-09-11 11:51:24

與POR或ASF能力的結(jié)合。下面是輔助累加器迄今最有意義的用法:1. 最初,這是為了支持掃頻而引入的。利用第二個累加器來提供一個穩(wěn)定增加的變量。先進DDS可將該變量增加到基本頻率調(diào)諧字上,從而獲得一個頻率

2018-10-31 10:53:03

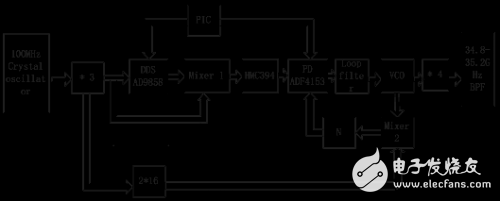

本文將介紹DDS和PLL的工作原理,并結(jié)合一電臺(工作頻率2 MHz~500 MHz)的設(shè)計,給出DDS做參考的PLL頻率合成器的設(shè)計方案。

2021-04-20 06:42:27

信號發(fā)生器是一種常用的信號源,廣泛應(yīng)用于通信、測量、科研等現(xiàn)代電子技術(shù)領(lǐng)域。信號發(fā)生器的核心技術(shù)是頻率合成技術(shù),主要方法有:直接模擬頻率合成、鎖相環(huán)頻率合成(PLL)、直接數(shù)字合成技術(shù)(DDS

2019-09-29 08:08:12

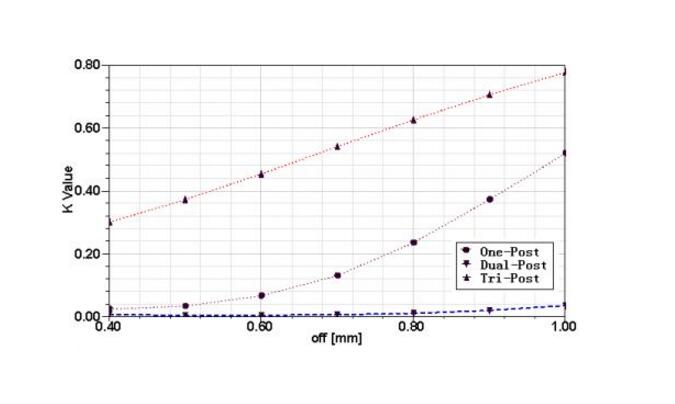

信號能力,具有寬帶、小步進、低雜散的頻率源也就變得越來越重要。 直接數(shù)字式頻率合成源(DDS)驅(qū)動鎖相環(huán)(PLL)方式,近端環(huán)路內(nèi)雜散按20lgN惡化(N為鎖相環(huán)倍頻次數(shù))[1],其電路結(jié)構(gòu)簡單,易于

2020-12-03 16:06:44

直接數(shù)字頻率合成(DDS)具有快速頻率切換和調(diào)制能力,應(yīng)用廣泛。但是,當?shù)凸暮偷统杀臼侵饕紤]因素時,DDS常常不得不退居其次,讓位于模擬鎖相環(huán)(PLL)。AD9913改變了這一局面,不僅

2011-09-06 14:47:52

測試木材的介電常數(shù)。從低頻段到高頻段(ka波段),具體波段可以根據(jù)實際討論,低一些也行。

2019-07-01 19:21:58

AD9850 是AD I 公司采用先進的DDS 技術(shù), 1996年推出的高集成度DDS 頻率合成器, 它內(nèi)部包括可編程DDS 系統(tǒng)、高性能DAC 及高速比較器, 能實現(xiàn)全數(shù)字編程控制的頻率合成器和時鐘

2008-04-10 13:14:29 83

83 利用反向并聯(lián)二極管對的二倍頻原理,設(shè)計了Ka波段二倍頻器。用高級設(shè)計系統(tǒng)ADS設(shè)計軟件包的射頻設(shè)計軟件對二倍頻器的電路進行了模型設(shè)計和仿真分析,并對設(shè)計出的二倍頻器

2008-11-17 23:24:09 50

50 給出了Ka 波段相對論繞射輻射振蕩器(RDG)的輻射功率測量方法和實驗結(jié)果。器件采用帶反射器兩段式過模慢波結(jié)構(gòu),由于器件的過模結(jié)構(gòu)特點,實驗選擇用空間積分方法測試輻射功

2009-02-28 17:02:18 19

19 雜散抑制差和輸出頻率低是DDS的兩大缺點,并且隨著輸出帶寬的增加雜散性能更加惡化。傳統(tǒng)的解決方法是采用更好的算法和改進DDS芯片本身的結(jié)構(gòu)。該文在分析了DDS雜散性能和

2009-03-11 22:09:22 19

19 DDS直接頻率合成,由Quicklogicw公司提供

2009-05-14 10:51:37 26

26 DDS(直接數(shù)字頻率合成)技術(shù)是一門在頻率合成領(lǐng)域的新興技術(shù),具有響應(yīng)時間短,精度高等優(yōu)點。而PLL(Phase Locked Loop)鎖相環(huán)技術(shù)雖然工作速度慢,但穩(wěn)定可靠。VXI 總線具有

2009-06-01 16:12:24 17

17 DDS的結(jié)構(gòu)和在系統(tǒng)設(shè)計中的優(yōu)勢以及D A轉(zhuǎn)換器在DDS中的應(yīng)用:

2009-06-10 11:11:09 34

34 ALA0025 - Ka 波段 25 KHz 穩(wěn)定性 PLL LNB ALA0025 規(guī)格轉(zhuǎn)換增益 55 dB ty p.(50dB m in.

2022-11-14 09:21:10

ALB0025 - Ka 波段 25 KHz 穩(wěn)定性 PLL LNB ALB0025 規(guī)格轉(zhuǎn)換增益 55 dB ty p.(50dB m in.

2022-11-14 09:33:33

針對PLL體系結(jié)構(gòu)的頻率合成及規(guī)劃:In many applications, it is desired to generate a set of frequencies from

2009-08-17 09:52:31 8

8 本文討論了DDS+PLL 結(jié)構(gòu)頻率合成器硬件電路設(shè)計中需要考慮的幾方面問題并給出了設(shè)計原則,依此原則我們設(shè)計了一套短波波段頻率合成器,實驗結(jié)果證實了其可行性。

2009-09-07 16:07:29 34

34 直接數(shù)字合成(DDS)是近年發(fā)展起來的一種新型合成技術(shù),有頻率分辨率高,轉(zhuǎn)換時間短,相位噪聲低等特點,與鎖相合成技術(shù)(PLL)配合,可以設(shè)計出頻帶寬、分辨率高的頻率

2009-09-11 15:55:32 13

13 Ka波段低噪聲放大器的研鑭:本文介紹了~種毫米波低噪聲放大器的設(shè)計技術(shù),應(yīng)用CAD技術(shù)設(shè)計了波導到微帶的過渡,結(jié)合其它電路設(shè)計和組裝工藝,研制出了工作帶寬為3GHz的Ka波

2009-11-01 14:56:59 16

16 針對直接數(shù)字頻率合成(DDS)和集成鎖相環(huán)(PLL)技術(shù)的特性,提出了一種新的DDS 激勵PLL 系統(tǒng)頻率合成時鐘發(fā)生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用濾波的方法

2009-12-14 10:22:00 36

36 直接數(shù)字合成(DDS)是近年發(fā)展起來的一種新型合成技術(shù),有頻率分辨率高,轉(zhuǎn)換時間短,相位噪聲低等特點,與鎖相合成技術(shù)(PLL)配合,可以設(shè)計出頻帶寬、分辨率高的頻率合

2010-08-04 15:57:03 0

0 DDS,什么是DDS,DDS的結(jié)構(gòu)

DDS概述

直接數(shù)字式頻率綜合器DDS(Direct Digital Synthesizer),

2009-09-03 08:42:40 4227

4227

U波段常用電臺頻率表

頻道號

發(fā)信頻率

收信頻率

2009-10-20 15:21:46 7228

7228 DDS是什么意思,DDS結(jié)構(gòu),DDS原理是什么

什么叫DDS

直接數(shù)字式頻率合成器DDS(Direct Digital Synthesizer),實際

2010-03-08 16:56:38 45260

45260 DDS+PLL高性能頻率合成器的設(shè)計方案

頻率合成理論自20世紀30年代提出以來,已取得了迅速的發(fā)展,逐漸形成了直接頻率合成技術(shù)、鎖相頻率合成技術(shù)、直接數(shù)字式頻率

2010-04-17 15:22:13 3209

3209

休斯和Avanti擴展Ka波段衛(wèi)星服務(wù)范圍一宗為期多年的4200萬美元交易,由休斯公司向Avanti提供Ka波段技術(shù),以擴展HYLAS 1 & 2衛(wèi)星在歐洲/中東和非洲的寬帶服務(wù)范圍

&nb

2010-04-29 16:45:17 491

491 對寬帶多媒體衛(wèi)星通信系統(tǒng)的需求進行分析的基礎(chǔ)上,對基于星載ATM交換的KA波段寬帶多媒體衛(wèi)星通信系統(tǒng)的技術(shù)特點 系統(tǒng)組成、協(xié)議棧結(jié)構(gòu)及工作模式進行簡要介紹

2011-03-22 15:50:39 164

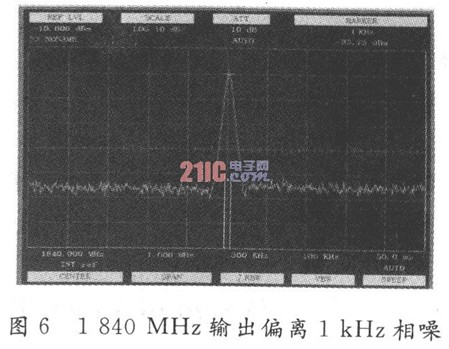

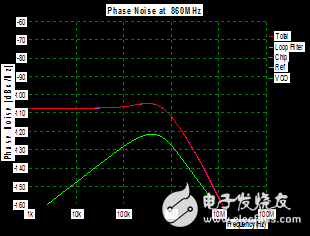

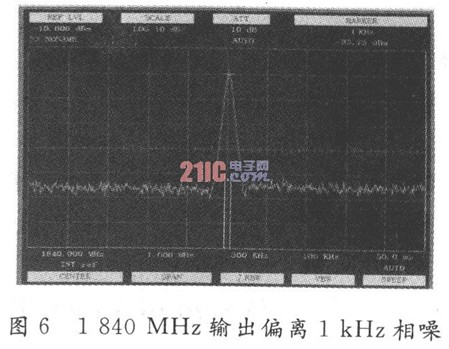

164 針對高性能DDS芯片AD9858設(shè)計寬帶 頻率合成器 , 分析DDS的工作原理,給出寬帶頻率合成器的原理框圖和實現(xiàn)過程,并對軟件控制流程進行了詳細說明,結(jié)合理論對系統(tǒng)的相位噪聲和雜散

2011-06-22 10:49:03 50

50 本文將介紹DDS和PLL的工作原理,并結(jié)合一電臺(工作頻率2 MHz~500 MHz)的設(shè)計,給出DDS做參考的PLL頻率合成器的設(shè)計方案。

2011-07-18 09:38:02 3423

3423

結(jié)合直接數(shù)字頻率合成(DDS)和鎖相環(huán)(PLL)技術(shù)完成了X波段低相噪本振跳頻源的設(shè)計。文章通過軟件仿真重點分析了本振跳頻源的低相噪設(shè)計方法,同時給出了主要的硬件選擇和詳細

2012-03-20 15:52:28 18

18 在非相參雷達測試系統(tǒng)中,頻率合成技術(shù)是其中的關(guān)鍵技術(shù).針對雷達測試系統(tǒng)的要求,介紹了一種用DDS激勵PLL的X波段頻率合成器的設(shè)計方案。文中給出了主要的硬件選擇及具體電路設(shè)

2012-06-28 17:33:39 39

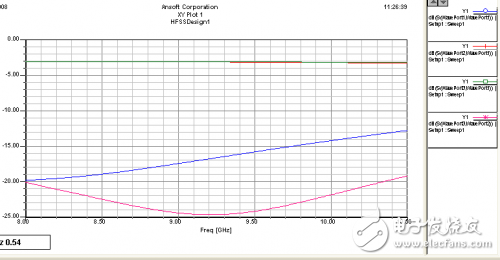

39 介紹了一種橫向Ka波段寬帶波導-微帶探針過渡的設(shè)計,基于有限元場分析軟件Ansoft HFSS對該類過渡的設(shè)計方法進行了研究。最后給出了Ka波段內(nèi)的優(yōu)化數(shù)據(jù)。仿真結(jié)果表明,該寬帶波導

2012-08-29 17:11:09 54

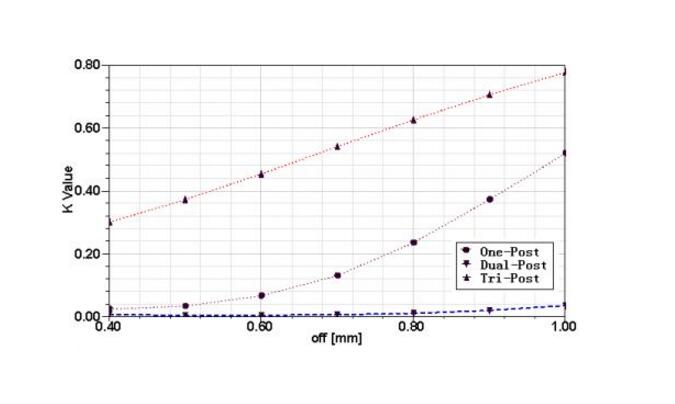

54 介紹了一種Ka波段的四路功率分配/合成網(wǎng)絡(luò)。該網(wǎng)絡(luò)采用H面波導裂縫電橋結(jié)構(gòu),只需要一個耦合單元,結(jié)構(gòu)簡單、易于加工。這種合成網(wǎng)絡(luò)將使用在基于MMIC單片TGA1141的四路功率合成器

2012-11-09 16:21:05 31

31 為了滿足寬頻段、細步進頻率綜合器的工程需求,對基于多環(huán)鎖相的頻率合成器進行了分析和研究。在對比傳統(tǒng)單環(huán)鎖相技術(shù)基礎(chǔ)上,介紹了采用DDS+PLL多環(huán)技術(shù)實現(xiàn)寬帶細步進頻綜,輸

2013-04-27 16:26:51 48

48 為了研制一種鎖定時間短、相位噪聲低、雜散抑制度高的頻率合成技術(shù),采用了直接數(shù)字式頻率合成器(DDS)驅(qū)動鎖相環(huán)(PLL)的結(jié)構(gòu)。該頻率合成器綜合了DDS頻率轉(zhuǎn)換速度快、頻率分

2013-07-26 11:55:05 42

42 一種Ka波段基片集成波導功率合成器的設(shè)計.

2016-01-04 15:21:55 0

0 DDS-PLL組合跳頻頻率合成器,有需要的都可以看看。

2016-07-20 15:48:57 42

42 詳細介紹了直接數(shù)字頻率合成器(DDS)的工作原理、基本結(jié)構(gòu)。在參考DDS 相關(guān)文獻的基礎(chǔ)上,提出了符合結(jié)構(gòu)的DDS 設(shè)計方案,利用DDS 技術(shù)設(shè)計了一種高頻率精度的多波形信號發(fā)生器,此設(shè)計基于可編程邏輯器件FPGA,采用Max+PlusⅡ開發(fā)平臺,由Verilog_HDL 編程實現(xiàn)。

2016-11-22 14:35:13 0

0 學習單片機電路圖的很好的資料——DDS-PLL組合跳頻頻率合成器

2016-11-03 15:15:39 0

0 一種基于DDS的S波段頻率源設(shè)計,下來看看

2017-01-13 13:46:17 27

27 K波段低相位噪聲頻率綜合器的設(shè)計與實現(xiàn)_鄭永華

2017-01-08 10:18:57 3

3 將DDS和PLL技術(shù)結(jié)合起來,采用DDS直接激勵PLL的混合頻率合成方案完成了X波段微波變頻信號源的設(shè)計,一定程度上解決了頻率分辨率、頻率轉(zhuǎn)換速度和相位噪聲的問題,并完成了實機研制、系統(tǒng)聯(lián)調(diào)試

2017-10-27 11:18:52 4

4 結(jié)合數(shù)字式頻率合成器(DDs)和集成鎖相環(huán)(PLL)各自的優(yōu)點,研制并設(shè)計了以DDS芯片AD9954和集成鎖相芯片ADF4113構(gòu)成的高分 辨率、低雜散、寬頻段頻率合成器,并對該頻率合成器進行了分析

2017-10-27 17:54:21 8

8 頻率源的一個重要方式,但是它體積大、設(shè)備復雜、雜散也較大。數(shù)字鎖相集成器件出現(xiàn)以來,鎖相式頻率合成器得到迅速發(fā)展,但是當需要窄頻率步進時,環(huán)路帶寬需要降低,致使鎖定時間變長,不能滿足快速跳頻的要求。DDS的出現(xiàn)恰好可

2017-11-14 15:46:48 2

2 1 引言 Ka波段具有許多讓人注目的特點,如高數(shù)據(jù)傳輸率和良好的保密性,這使得它吸引了大量工程技術(shù)人員的注意。因此大量Ka波段商用和軍用的電路得以實現(xiàn)。但是,對低成本,結(jié)構(gòu)緊湊和高性能的追求必然

2017-11-14 16:08:17 0

0 的新型通信衛(wèi)星的研發(fā)具有重要意義。由于Ka波段接收機具有頻率高、信息容量大、抗干擾性強等特點,目前我國的新型通信衛(wèi)星多采用該項技術(shù)。因此,研制高性能的Ka波段接收組件迫在眉睫。 2 系統(tǒng)組成及工作原理 該組件主要由射頻通道、混頻

2017-11-17 15:42:24 5

5 (PLL)技術(shù)的間接頻率合成器目前應(yīng)用最為廣泛。直接模擬頻率合成器(DAS)采用倍頻器、分頻器、混頻器及微波開關(guān)來實現(xiàn)頻率合成,具有最優(yōu)的近端相位噪聲和高速捷變頻特性,但結(jié)構(gòu)復雜、成本昂貴的特點限制其只能應(yīng)用于雷達等高端

2017-11-18 09:55:09 4

4 日晚,衛(wèi)星中繼終端用國產(chǎn)Ka波段行波管作為主份首次開機成功,工作正常。 實踐十六號衛(wèi)星任務(wù)是實現(xiàn)空間探測和技術(shù)試驗。該衛(wèi)星裝備的X和Ka波段兩個國產(chǎn)行波管放大器均由中國科學院電子學研究所自主研制。實踐十六號衛(wèi)星國產(chǎn)X波段、Ka波段行波管開機成

2017-12-06 09:48:14 688

688 Ka波段是電磁頻譜的微波波段的一部分,Ka波段的頻率范圍為26.5-40GHz。Ka代表著K的正上方(K-above),換句話說,該波段直接高于K波段。Ka波段也被稱作30/20 GHz波段,通常

2018-02-20 18:20:00 2661

2661

Ka波段具有許多讓人注目的特點,如高數(shù)據(jù)傳輸率和良好的保密性,這使得它吸引了大量工程技術(shù)人員的注意。因此大量Ka波段商用和軍用的電路得以實現(xiàn)。

2018-05-02 10:40:00 2179

2179

直接數(shù)字式頻率綜合器 DDS(Direct Digital Synthesizer),實際上是一種分頻器:通過編程頻率控制字來分頻系統(tǒng)時鐘(SYSTEM CLOCK)以產(chǎn)生所需要的頻率。DDS

2018-06-19 08:00:00 25

25 TrimQUT TGA45—SM是Ka波段封裝的驅(qū)動放大器。TGA45 12SM工作在28~32 GHz,是使用TrimQuin的功率PHEMT生產(chǎn)工藝設(shè)計的。

2018-08-28 11:26:00 2

2 本文檔的主要內(nèi)容詳細介紹的是TGA4507 Ka波段低噪聲放大器的詳細數(shù)據(jù)手冊免費下載

2018-08-22 11:26:00 4

4 TrimQuT TGA4541-SM是一個可變增益放大器,用作線性Ka波段應(yīng)用中的驅(qū)動放大器。TGA45 41-SM從28到31 GHz工作,并使用TrimQuin的PHEMT生產(chǎn)工藝設(shè)計。

2018-08-10 11:28:00 2

2 本文檔的主要內(nèi)容詳細介紹的是TGA4508 Ka波段低噪聲放大器的詳細數(shù)據(jù)手冊免費下載。

2018-08-02 11:29:00 9

9 本文檔的主要內(nèi)容詳細介紹的是TGA4507 Ka波段低噪聲放大器詳細數(shù)據(jù)免費下載。

2018-08-02 11:29:00 8

8 介紹了直接數(shù)字頻率合成器(Direct Digital fiequency Synthesizer,DDS)的基本結(jié)構(gòu)和工作原理,并在此基礎(chǔ)上著重論述了利用舭軟件建立DDS的理想和雜散仿真模型的方法。通過建立仿真模型,可以更方便有效地對DDS雜散分布特點進行分析。

2019-11-06 17:48:21 15

15 PLL 頻率合成器基本構(gòu)建模塊 PLL 頻率合成器可以從多個基本構(gòu)建模塊的角度來考察。我們在前面已經(jīng)提到過這個問題,下面將更加詳細地進行探討:鑒頻鑒相器(PFD) 參考計數(shù)器(R) 反饋計數(shù)器

2020-12-03 01:47:00 21

21 KU波段是指比IEEE 521-2002標準下的K波段頻率低的波段,KU的頻段通常下行從10.7到12.75GHz,上行從12.75到18.1GHz。

2020-11-27 16:14:00 30124

30124 ADMV4530:帶集成小數(shù)N PLL和壓控振蕩器的雙模Ka波段上變頻器數(shù)據(jù)表

2021-04-24 16:10:26 10

10 HMC7054:Ka波段HPA數(shù)據(jù)表

2021-04-27 12:03:55 8

8 近二十年來,隨著數(shù)字集成電路和微電子技術(shù)的發(fā)展,出現(xiàn)了一種新的頻率合成技術(shù)--直接數(shù)字合成 Direct Digital Synthesize 技術(shù)。DDS的出現(xiàn)導致了頻率合成領(lǐng)域的第二次

2021-05-20 11:10:11 5449

5449

PLL設(shè)計和時鐘頻率產(chǎn)生機理免費下載。

2021-06-07 14:36:43 22

22 直接數(shù)字頻率合成技術(shù)(DDS+PLL)資料下載。

2021-06-07 14:41:54 38

38 在典型的永久性衛(wèi)星通信設(shè)施中,室外設(shè)備和室內(nèi)設(shè)備在功能上是分開的。室外設(shè)備由Ka波段天線、低噪聲塊(LNB)和下變頻級組成,其將Ka波段信號下變頻為L波段信號,然后發(fā)送到室內(nèi)單元。

2022-08-22 11:56:09 999

999 Ka波段上運行著數(shù)據(jù)速率最高的最先進衛(wèi)星通信系統(tǒng)。由于Ka波段頻率的傳輸質(zhì)量在很大程度上取決于天氣條件,因此需要仔細規(guī)劃和選擇合適的系統(tǒng)配置。

2022-10-26 16:42:22 748

748 傳統(tǒng)Ka波段地面站衛(wèi)星通信系統(tǒng)依賴于室內(nèi)到室外配置。室外單元包含天線和塊下變頻接收機,接收機輸出L波段的模擬信號。該信號隨后被傳送到室內(nèi)單元,室內(nèi)單元包含濾波、數(shù)字化和處理系統(tǒng)。Ka波段的干擾信號

2023-01-04 10:44:30 765

765 新的集成完整DDS產(chǎn)品為敏捷頻率合成應(yīng)用提供了一種有吸引力的模擬PLL替代方案。長期以來,直接數(shù)字頻率合成 (DDS) 一直被認為是生成高精度、頻率捷變(寬范圍內(nèi)可快速變化的頻率)、低失真輸出波形的卓越技術(shù)。

2023-01-30 09:51:57 1148

1148

與基于PLL的傳統(tǒng)頻率合成器相比,NCO和DDS的顯著優(yōu)勢包括:極高的頻率分辨率、快速靈敏性,以及可輕松生成完美正交的正弦/余弦波形

2023-02-19 11:18:10 521

521 pll頻率合成器工作原理與pll頻率合成器的原理圖解釋 我們要搞清楚pll頻率合成器工作原理與pll頻率合成器的原理圖就要先搞清楚pll和頻率合成器的概念。 頻率合成器:將一個高穩(wěn)定度和高精度的標準

2023-02-24 18:19:52 8266

8266

Ka波段上運行著數(shù)據(jù)速率最高的最先進衛(wèi)星通信系統(tǒng)。Ka波段站點分集配置依賴DWDM射頻-光纖傳輸系統(tǒng)和冗余切換單元,虹科提供最合適的解決方案,確保最大的系統(tǒng)可靠性和可用性。

2022-11-02 15:43:19 587

587

頻率的產(chǎn)生有兩種方法:DDS和PLL,但是為什么射頻工程師一般用PLL多,很少用DDS呢?

2023-06-28 09:38:48 1823

1823

影響PLL的應(yīng)用領(lǐng)域。PLL鎖定時間可以根據(jù)PLL的頻率精度來計算,下面是一個詳細的討論。 PLL - 綜述 PLL是一種電路,它在輸入信號和輸出信號之間建立了一個相位鎖定環(huán),以使輸出頻率與輸入頻率之間存在固定的關(guān)系。舉例來說,如果PLL的輸入頻率為f_in,而輸出頻

2023-09-02 15:12:23 811

811 電子發(fā)燒友網(wǎng)站提供《一種橫向Ka波段寬帶波導-微帶探針過渡的設(shè)計.pdf》資料免費下載

2023-10-23 14:11:43 2

2 電子發(fā)燒友網(wǎng)站提供《一種用DDS激勵PLL的X波段頻率合成器的設(shè)計方案.pdf》資料免費下載

2023-10-24 09:10:26 4

4 電子發(fā)燒友網(wǎng)站提供《Ka波段基片集成波導帶通濾波器的設(shè)計.pdf》資料免費下載

2023-10-25 11:18:32 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論