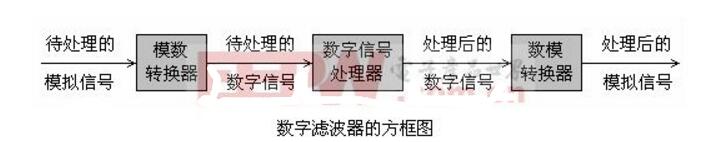

濾波器是任何信號處理系統的關鍵組成部分,隨著現代應用的日趨復雜,濾波器設計的復雜程度也日益提高。采用 FPGA 設計和實現的高性能濾波器的能力是模擬方法所望塵莫及的。另外,采用FPGA 設計的數字濾波器可以避免模擬設計中存在的某些問題,特別是組件漂移和容差(在高可靠應用中,由溫度過高、老化和輻射問題造成)。這些模擬問題會顯著降低濾波器的性能,特別是在通帶紋波等方面。

當然, 數字模型也有自身的缺陷。濾波器數學運算中的舍入可能會帶來問題,因為舍入誤差會被累加,給性能造成不良影響,比如增大濾波器的噪聲基底。工程師可以采取多種方法最大程度地減輕這種影響,例如使用收斂舍入可以獲得比傳統舍入更好的性能。最終, 舍入誤差問題的嚴重性與模擬器件相比得到了顯著降低。

將 FPGA 作為濾波器構建模塊的主要優勢之一在于,如果因為集成原因或者需求變動原因需要調整性能,允許在設計過程的后期修改或者更新濾波器的參數,且產生的影響很小。

濾波器類型和拓撲結構

大多數熟知數字信號處理的工程師都知道濾波器的主要類型有四種。低通濾波器只允許頻率低于預設截止頻率的信號通過。高通濾波器與低通濾波器相反,只允許頻率高于截止頻率的信號通過。帶通濾波器只允許頻率在預設帶寬內的信號通過,不允許其它頻率的信號通過。帶阻濾波器與帶通濾波器相反,不允許頻率在預設帶寬內的信號通過,但允許其它頻率的信號通過。

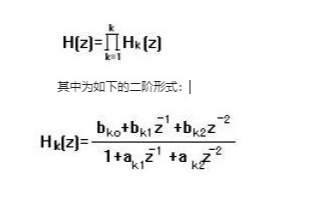

大多數數字濾波器都采用下列兩種方法之一來實現: 有限脈沖響應(FIR) 和無限脈沖響應 (IIR)。首先我們深入探討如何設計和實現 FIR 濾波器。這種濾波器也常被稱為窗口 sinc濾波器。

為什么我們首先以 FIR 濾波器為重點呢?兩種濾波器的最大區別在于有無反饋。對未采用反饋的 FIR 濾波器,在給定的輸入響應下,濾波器的輸出最終會穩定為 0。而對采用反饋的IIR 濾波器,在相同的給定輸入下,輸出不會穩定為 0。

FIR 濾波器的設計由于未采用反饋,故天生具有穩定性,因為濾波器的所有極點都與原點重合。IIR 濾波器就沒有這么幸運。由于在設計 IIR 濾波器的時候,必須精心考慮其穩定性,這樣窗口 sinc 濾波器對新接觸 DSP 技術的工程師來說,更加易于理解和實現。

如果要求工程師繪制理想低通濾波器在頻域中的原理框圖,大多數工程師會畫出和圖 1 一樣的圖。

圖 1 所示的頻率響應一般稱為“磚墻型”濾波器。這是因為通帶和阻帶之間的過渡非常陡峭,要比現實中能夠實現的陡峭很多。這種頻率響應還具備其它“理想”特性,例如沒有通帶波紋以及具有理想的阻帶衰減。

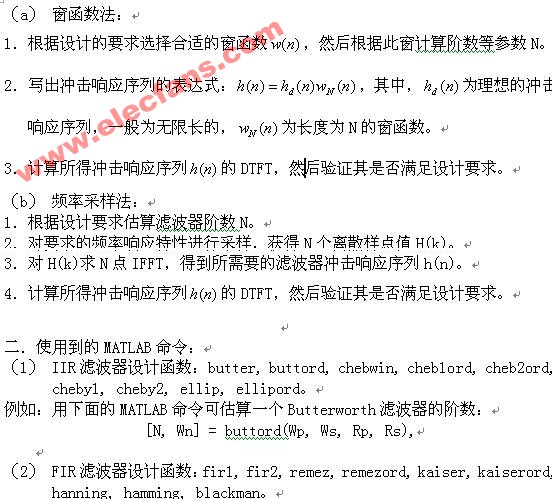

如果將該圖圍繞 0 Hz 進行對稱擴展,同時擴展到 +/- FS Hz(FS 指采樣頻率),然后對響應進行離散傅里葉逆變換 (IDFT),就可以得到該濾波器的脈沖響應,如圖 2 所示。

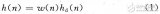

這就是圖 1 所示理想濾波器頻率響應的時域表示法,也稱為濾波器內核。FIR 或窗口 sinc 濾波器正是由這個響應而得名,因為畫出 sinc 函數的曲線可以得到脈沖響應:

結合濾波器階躍響應, 頻率響應、脈沖響應和階躍響應提供了有關濾波器性能的所有信息,可用于判斷濾波器是否滿足設計要求。

頻率響應

頻率響應是工程師在考慮濾波器時所習慣關注的問題。它代表著濾波器改變頻域信息的性能。

通過頻率響應可以觀察到截止頻率、阻帶衰減和通帶波紋。在該響應中還可以清晰地觀察到通帶和阻帶之間的滾降,也稱為過渡帶。通帶中的波紋會給濾波信號造成影響。阻帶衰減則表明濾波器輸出中存在多少不必要的頻率。這對需要抑制特定頻率的應用意義重大,比如在通信系統中為頻分多路復用通道濾波。

脈沖響應

從脈沖響應中可以抽象出濾波器的系數。但是,要實現濾波器的最佳性能,標準的方法是采用窗函數。窗函數指給截斷的脈沖響應應用額外的數學函數,以求減輕截斷帶來的副作用。

在圖 2 中,由于紋波的存在,脈沖響應向外無限延伸,盡管紋波的振幅顯著降低,但永遠不會降低至 0。因此,必須圍繞位于中心的主瓣,在兩側對稱地按 N+1 的系數截斷脈沖響應,這里 N 是期望的濾波器長度(切記 N應為偶數)。脈沖響應被突然截斷會給濾波器的頻域性能帶來不良影響。如果對截斷的脈沖響應進行離散傅里葉變換 (DFT),可以觀察到通帶和阻帶都有波紋出現以及滾降性能的下降。這就是為什么一般會采用窗函數來改善性能的原因。

階躍響應

對脈沖響應進行積分所得的階躍響應體現著濾波器的時域性能以及濾波器自身如何影響該性能。觀察階躍響應時應重點關注的三大參數分別是上升時間、過沖以及線性度。

上升時間指從振幅級的 10% 上升到 90% 所需的樣本數量,可顯示濾波器的速度。要在最終系統中具有實用性,濾波器必須能夠區分輸入信號中的不同事件,因此階躍響應必須短于信號中各事件之間的間隔。

過沖是指濾波器添加至其正在處理的信號時產生的失真。降低階躍響應中的過沖有助于判斷信號的失真是來自系統,還是來自系統正在測量的信息。過沖不但可增大失真來源的不確定性,降低最終系統性能,而且還可導致系統無法滿足所需的性能要求。

如果信號的上半部分和下半部分是對稱的,則濾波器的相位響應具有線性相位,這是確保階躍響應的上升沿和下降沿相同的要件。

優化濾波器,以在時域和頻域中同時實現良好的性能是非常困難的,在這一點上它也是毫無價值的。因此,必須明白需要處理的信息位于哪一個域中。對于 FIR 濾波器而言,需要處理的信息位于頻域中,因而頻率響應占主導地位。

濾波器加窗

使用截斷脈沖響應不能提供最佳性能數字濾波器,因為它不能展示任何理想的特性。因此設計人員可采用視窗函數來改善濾波器的通帶紋波、滾降以及阻帶衰減性能。對于截斷正弦函數,有許多視窗函數可以使用,如高斯、巴特利特、海明、布萊克曼以及凱塞等。不過最常用的兩種視窗函數是海明和布萊克曼。下面將詳細介紹這兩種視窗。

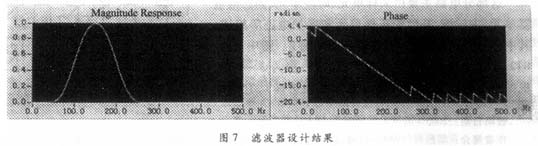

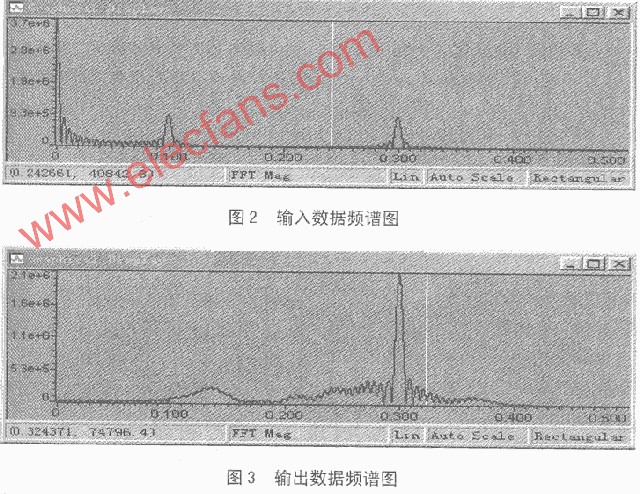

采用這兩種視窗不但可降低通帶紋波,而且還可提高濾波器的滾降和衰減性能。圖 3 是采用布萊克曼和海明視窗后截斷正弦函數的脈沖響應和頻率響應情況。如圖所示,兩種視窗均可顯著改善通帶紋波狀況。

濾波器的滾降不僅由視窗決定,而且還由濾波器的字長決定,即系數的數量,也就是常說的濾波器抽頭。

海明視窗:

w[i] = 0.42 – 0.52 cos (2PI*i/N)

布萊克曼視窗:

w[i] = 0.42 – 0.52 cos (2PI*i/N)

+ 0.08 cos(4PI*i/N)

方程式中 i 為 1 至 N 時,總數等于 N+1個點。

要將這些視窗應用于截斷脈沖響應,必須用視窗系數乘以截斷脈沖系數,得出所需的濾波器系數。

雖然視窗類型決定了滾降頻率,但經驗法則告訴我們,對于所需的跳變帶寬,需要的抽頭數量為:

N=4/BW

其中 BW 為跳變帶寬。

實現不同的濾波器拓撲

無論最終得到的濾波器類型是什么(是帶通、帶阻還是高通),所有這些都始于低通濾波器的初始設計。如果知道如何設計低通濾波器和高通濾波器,將兩者相結合就可得到帶阻及帶通濾波器。

首先看如何將低通濾波器轉化成高通濾波器。最簡單的方法叫做頻譜翻轉,即將阻帶轉換為通帶,將通帶轉換為阻帶。執行頻譜翻轉的方法是翻轉每一個樣本,同時給中心樣本添加一個樣本。第二種轉換高通濾波器的方法為頻譜倒轉,即鏡像頻譜響應,方法很簡單,就是倒轉每一個其它系數。

完成低通濾波器和高通濾波器的設計之后,就可通過組合便捷地生成帶通濾波器和帶阻濾波器。生成帶阻濾波器只需將高通濾波器和低通濾波器并行布置,然后將輸出加總。生成帶通濾波器則可通過將低通濾波器和高通濾波器串行布置來實現。

實際設計

上面的內容現已詳細說明了窗式正弦濾波器的情況、視窗應用的重要性以及如何生成不同拓撲的濾波器。不過在 FPGA 中實現濾波器之前,必須使用如 Octave、MATLAB? 或者 Excel等一種軟件工具生成一組濾波器系數。許多這些工具都可提供簡化的界面和選項,幫助用戶以最少的工作量完成濾波器設計,MATLAB 中的 FDA 工具就是最好的示例。

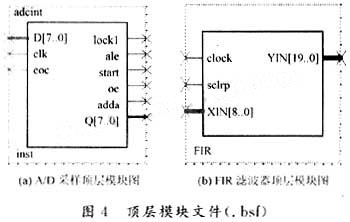

在為所需濾波器生成一組系數后,就可在 FPGA 中實現濾波器。無論決定采用的抽頭數量多寡,FIR 濾波器每一級的基本結構是不變的,總是由乘法器、存儲以及加法器構成。

現在在許多應用中都可看到數字濾波器的身影,而 FPGA 則可為使用它們的系統設計人員帶來顯著優勢。

大多數工程師青睞的、迄今為止最簡單的方法是使用賽靈思 COREGenerator? 工具的 FIR Compiler,其可為定制和生成高級濾波器提供多種選項。用戶可將生成的系數以 COE 文件形式導入 FIR Complier。該文件內含已經為基數賦值的各種濾波器系數。

Radix=10;

Coefdata =

-0.013987944,

-0.01735736,

-0.005971498,

0.012068368,

0.02190073,

將這些系數加載后,FIR Compiler將顯示與所提供系數相對應的該濾波器頻率響應,以及阻帶衰減與通帶紋波等基本性能特征。

在使用 FIR Compiler 工具完成濾波器定制后,只要用戶使用的是正確的仿真庫,CORE Generator 就可生成實現設計以及在實現之前的行為仿真過程中對其仿真所需的全部文件。

如果愿意,用戶還可以使用用戶自己生成的 HDL 實現該濾波器。這種方法一般只有在用戶最終實施目的是ASIC,只是將 FPGA 實施用作原型設計系統時使用。在這種情況下,第一步是量化濾波器系數,以便使用浮點結果的固定數字表示。由于濾波器系數可以為正,也可以為負,常見的做法是采用二的補碼格式表示這些系數。在完成系數的量化后,就可將其當作常數用于HDL 設計中。

現在在許多應用中都可看到數字濾波器的身影,而 FPGA 則可為需要使用它們的設計人員帶來顯著優勢。使用基本數學工具,結合 FPGA 內核生成工具或者直接使用 HDL,可便捷設計和實現窗式正弦濾波器。

電子發燒友App

電子發燒友App

評論