超高速雷達數字信號處理技術

綜述了超高速雷達數字信號處理技術的應用背景、研究內容、關鍵技術及解決方法.采用超高速數字信號處理技術實現了超高速數據采集、高速數字脈沖壓縮、超高速雷達回波模擬等系統.

關鍵詞:雷達;超高速;數字信號處理;數據采集;脈沖壓縮;信號產生;信號模擬

Ultra-High-Speed Radar Digital Signal Processing

LONG Teng,MAO Er-ke,YUE Yan-sheng,HUANG Ruo-jian

(Department of Electronic Engineering,Beijing Institute of Technology,Beijing 100081 China)

Abstract:The application background,research area,key technique problems and their resolution of ultra-high-speed radar digital signal processing were discussed.An ultra-high-speed data acquisition system,a high-speed digital pulse compression system,and an ultra-high-speed radar echo simulator were realized.

Key words:radar;ultra-high-speed;digital signal processing;data acquisition;pulse compression;signal generator;signal simulator

一、引 言

本文所討論的超高速數字信號處理,是指數百兆帶寬信號的數字采集、處理技術超高速數字信號處理技術具有很多獨特的問題,必須進行仔細的分析和研究.

本文的目的,就是綜述超高速雷達數字信號處理技術的應用背景、研究內容、關鍵技術及解決方案,并介紹作者已經實現的一些超高速雷達數字信號處理系統.

二、超高速數字信號處理在雷達中的應用

1.距離高分辨率雷達數字信號處理

距離高分辨率雷達具有多種優點[1].對于最為常用的線性調頻脈沖(CHIRP)信號,為實現0.1~1m的距離分辨率,要求信號帶寬可以達到150~1500MHz[2],因此是超高速數字信號處理技術的主要應用之一.

2.合成孔徑雷達數字信號處理

合成孔徑雷達是當前雷達偵察的主要方式之一[3],其分辨率已經從早期的10m量級發展到目前的1m~0.1m量級[4],因此同樣需要進行超高速數字信號采集與處理.

3.電子對抗與反對抗

在電子對抗和反對抗領域,數字射頻存儲器技術是近年研究的熱點[5].數字射頻存儲器的主要指標之一是瞬時帶寬,其中3-bit量化的數字射頻存儲器帶寬已經可以達到17GHz,8-bit量化的數字射頻存儲器帶寬也可以達到220MHz[6].因此,數字射頻存儲器的基礎也是超高速數字信號采集與處理技術.

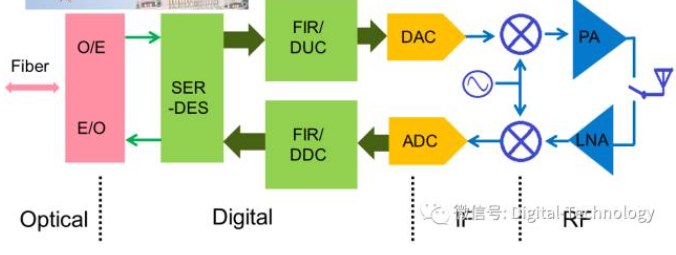

4.雷達數字接收機

當前雷達系統研究中已經提出了雷達數字接收機的概念,并在頻率較低的米波雷達中首先獲得了應用[7].雷達數字接收機的關鍵技術是對微波信號的采集和處理[7],因此同樣需要采用超高速數字信號處理技術.

5.多功能雷達信號產生與處理

雷達系統具有多種發射波形可以匹配不同的應用環境、通過多波形的組合使用取得最優的效果[8].直接數字合成(DDS)技術是數字波形形成的主要方法之一.當前DDS器件的水平已經可以達到400MHz[9],因此也是超高速數字信號處理技術的應用背景.

6.雷達信號/干擾模擬器

在雷達系統的研制中,為了在天線和微波前端不具備的條件下對雷達數字信號處理機進行調試,需要雷達視頻信號/干擾模擬器[10].對于距離高分辨率雷達、合成孔徑雷達,雷達信號/干擾模擬器也要能夠模擬寬帶視頻信號,因此也是超高速數字信號處理技術的應用領域之一.

三、超高速數字信號處理的主要內容與特殊問題

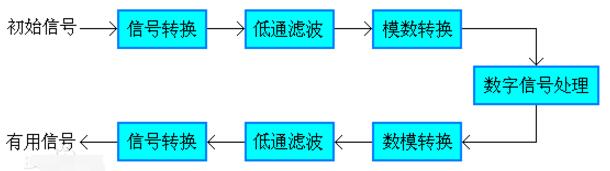

1.超高速數字信號處理的主要研究內容

超高速數字信號處理主要包括以下研究內容[11]:

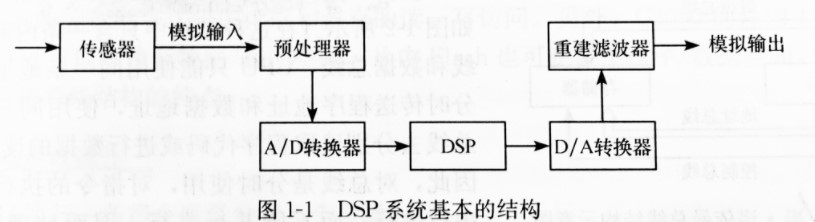

(1)超高速數據采集 超高速數據采集是整個超高速數字信號處理的最前端,包括超高速AD變換和超高速數據存儲.其中超高速AD變換的特殊問題是其中的超高速模擬電路,即AD變換的精度.它是整個超高速數字信號處理性能的基礎.

(2)高速實時數字信號處理 高速實時數字信號處理要完成對采集的超高速數據進行信號檢測、截獲、跟蹤等處理,并具備不斷修改、完善的潛力;因此其主要特點是實時性、多功能、可編程,故多采用高速實時數字信號處理芯片(DSP芯片)構成.當前先進DSP芯片的主要代表是TMS320C8x、TMS320C6x和ADSP2106x芯片等等.

(3)超高速信號生成與信號模擬 這里的超高速信號生成指的是通過直接數字合成(DDS)方法產生各種雷達信號,因此其中核心的問題是超高速DA轉換.這里的超高速信號模擬指的是通過數字仿真的方法模擬寬帶雷達視頻回波信號,因此核心的問題也是超高速DA轉換.

2.超高速數字信號處理的特殊問題

超高速數字信號處理的特殊問題主要表現在以下幾個方面[11,12]:

(1)元器件選型 芯片選型的問題主要在于兩個方面:一方面,傳統的TTL芯片不能滿足超高速數字信號處理的速度要求,必須采用更高速的芯片類型.另一方面,AD變換器、DSP芯片、專用芯片(如FFT、數字相關)、及DA變換器等芯片的選型應與系統的要求進行最佳匹配.

(2)體系結構 系統的體系結構必須在信號帶寬、數據存儲量、數字信號處理速度等多項要求之間進行最優的折中.由于系統速度要求很可能超過單片采集或處理芯片的速度極限,因此必須考慮采用多路并行的體系結構.

(3)數字電路的硬件實現 在硬件電路的實現中,由于信號之間的連線存在電阻、電容和電感,因此會造成信號的延遲、反射、串擾和噪聲.這些現象在中低速系統中通常可以忽略,但是在超高速系統中則會變得非常嚴重.例如,印制板上的線每英尺會造成約2ns的延遲量,這一延遲在中低速系統中可以不考慮,而在超高速系統中它已等同甚至超過一級門延遲.所以,超高速數據采集系統中的信號連線必須進行特殊的處理,才能保證系統的正常工作.

(4)模擬電路的抗干擾 在超高速數據采集、超高速信號生成/信號模擬等應用場合,除了數字電路之外,還有運算放大器、A/D變換器、D/A變換器等模擬器件.這些模擬器件很容易受到各種干擾,必須采取各種抗干擾措施來保證它們的精度.

(5)系統功耗與散熱 超高速系統的電流一般都遠大于中、低速系統,因為超高速系統實際上是以大電流來換取高速度的.系統功耗引起的溫升會使芯片的性能下降,嚴重時甚至會造成芯片的損壞.因此必須在系統設計時進行熱性能分析,并仔細研究系統散熱的方法.

(6)超高速數字信號處理的軟件算法 典型的雷達數字信號處理算法可分為底層算法和高層算法.底層算法主要是提高信噪比、抑制雜波等算法,包括脈沖壓縮、濾波、恒虛警率處理、信號檢測等.高層算法主要是雷達成像、目標識別等算法.此外,在電子對抗、信號生成、信號模擬等方面,也有其特殊的算法需要研究.

超高速信號處理算法中一個比較獨特的問題是需要研究信號處理算法的并行性、算法與硬件結構的最佳匹配問題.這是因為信號采集速度極高,要求信號的快速處理.在單片信號處理芯片性能不足的情況下,必須研究并行處理的處理機結構和與之相應的算法.

四、超高速數字信號處理關鍵技術的解決方案

1.元器件的選型[13]

對于超高速數字信號處理系統,傳統的TTL芯片已無法工作.目前常用的超高速標準芯片系列是ECL芯片;其不同系列的最高工作頻率可以達到250M、500M、甚至1600MHz(表1).對于更高速的系統;則需要采用砷化鎵器件構成.

表1 常用芯片的最高觸發器翻轉頻率(單位:MHz)

| TTL | TTL | TTL | TTL | CMOS | CMOS | ECL | ECL | ECL | ECL |

| 74LS | 74ALS | 74S | 74AS | 74HCT | 74ACT | 10K | 10KH | 100K | 100E |

| 33 | 50 | 95 | 125 | 50 | 125 | 150 | 250 | 375 | 1600 |

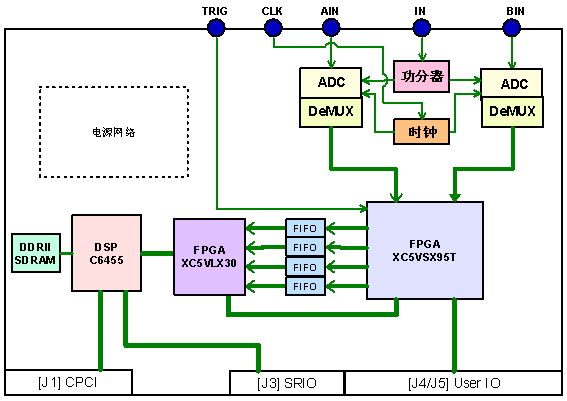

| 2.數字電路的實現[14] 在數字電路的實現中,主要需要解決信號的延遲、反射、串擾、噪聲問題.解決這些問題的方法,就是采用微波傳輸線作為信號之間的連線.微波傳輸線在端接電阻匹配的條件下可以消除反射,并精確控制信號的延遲.由于ECL芯片本身具有驅動50Ω端接傳輸線的能力,這就為微波傳輸線的實現奠定了基礎. 3.模擬電路抗干擾[15] 模擬電路的干擾源主要包括空間電磁輻射的干擾、信號線之間的串擾、地線和電源線的共模干擾等因素.可以采用屏蔽、大面積接地、元器件的合理布局、電源濾波等多種手段解決這一問題.例如,可以采用鐵氧體磁芯加電容濾波的方法來取得最好的濾波效果,并采用星形接地的方法來減小地線上的共模干擾. 4.體系結構的選擇 體系結構的設計可以分為多個層次:最頂層的設計是整個數字信號處理系統的體系結構;進一步細化的層次是AD、存儲器、DSP、DA等模塊的體系結構.超高速系統體系結構最重要的特點就是各種層次上的并行性;而具體系統的體系結構設計則要根據不同的應用條件而定. 5.系統功耗與散熱[11] 由于超高速系統的功耗很大,因此在系統設計時就必須把熱設計作為必需的組成部分;在設計階段就要仔細分析各個芯片的功耗、熱阻、溫度范圍及推薦的散熱方法.對于必須進行強制制冷的系統,可以在風冷、液冷等方案之間進行選擇;一般來說,只要選擇合適的風冷方法就可以使系統正常工作. 6.采用先進的分析手段[16] 電子設計自動化(EDA)技術可以對超高速系統的設計提供極大的幫助.先進的EDA工具可以分析PCB上傳輸線的延遲、反射和串擾,并對系統功耗和溫度進行分析;采用先進的EDA工具還可以在嚴格定義的布線條件下完成系統的自動布線,因此可以大大提高超高速系統的設計成功率. 五、超高速數據采集系統的實現 |

|

圖1 超高速數據采集系統的體系結構 (2)系統性能測試 數據采集系統的性能測試主要包括靜態測試和動態測試,其中動態測試更能夠全面地反應系統的性能.在動態測試中最為關心的指標是動態有效位(ENOB).本系統在250MS/s采樣速率、125MHz輸入信號時測試了系統的動態有效位,可以證明,系統的動態有效位在7-bit以上. 六、高速數字脈沖壓縮系統的實現 Y(ω)=H(ω).S(ω) (1) 這里,只要匹配濾波器的沖擊響應/傳遞函數與發射信號滿足匹配濾波關系,就可以獲得脈沖壓縮的輸出結果. |

|

圖2 時域法實現數字脈壓 (2)頻域法實現數字脈壓 頻域法實現數字脈壓的基礎是式(1),其基本結構示于圖3.這里,采集的原始信號首先通過FFT變換到頻域,與預先存儲的參考碼相乘后,再通過逆FFT變換回時域,就構成脈壓后的數字結果;同樣可以采用DA變換將其變為模擬信號顯示.由于FFT算法相當于快速卷積,因此頻域法的運算速度一般要快于時域法,尤其在壓縮比較大的情況下. |

|

圖3 頻域法實現數字脈壓 3.一種高速實時多功能數字脈沖壓縮系統的實現 七、超高速雷達信號發生器/回波模擬器的實現 |

|

圖4 DDS技術的原理框圖 2.超高速雷達回波模擬器的實現 |

|

圖5 雷達回波模擬器的原理框圖 (3)超高速雷達回波模擬器的實現 采用圖6介紹的方法實現了一個超高速雷達回波模擬器.模擬器的時鐘頻率為250MHz,因此模擬器的輸出頻率最高可達125MHz(圖6). |

|

圖6 超高速雷達回波模擬器的實現框圖 3.采用超高速雷達回波模擬器產生多種雷達發射信號 |

電子發燒友App

電子發燒友App

評論