摘 要: 設計了一種基于源級耦合結構的正交二分頻電路,由兩個完全相同的源級耦合D觸發器級聯構成,交替工作于觸發和鎖存模式。對傳統的源級耦合結構做了適當改進,采用動態負載,通過對PMOS管的開關控制很好地解決了電路工作速度和輸出擺幅間的矛盾;且時鐘開關PMOS和NMOS采用不同直流偏置,便于低電源電壓下直流工作點的選取。采用TSMC 0.18 μm RF CMOS工藝進行仿真驗證。實驗結果表明,分頻器在1.92 GHz輸入時鐘頻率下能正常實現正交二分頻,有較寬的鎖定范圍,且在3 V電源電壓下功耗僅為1.15 mW。

隨著便攜式手持無線設備的不斷發展,低功耗全集成收發機在無線通信領域受到越來越多的關注。在現代通信系統中,多模分頻器是工作在最高頻率的模塊之一,其設計具有很大的挑戰性。多模分頻器最重要的兩個指標是工作速度和功耗。而無論是采用脈沖吞咽方式實現的多模分頻器[1],還是串聯多個雙模預分頻器來實現的多模分頻器[2],高速分頻器都是其最關鍵的模塊之一。此外,在許多預分頻器設計中,為了降低整體功耗,通常選用相位切換結構,比同步雙模預分頻器具有更高的工作速度和更低的功耗[3-4]。在這種結構中,一般采用兩個動態觸發器級聯來完成二分頻正交信號輸出,并將此作為相位切換的輸入。但由于該分頻器工作在VCO的輸出頻率,功耗較大,如采用上述動態觸發器實現,則要求有一個全擺幅的時鐘信號,因此需要在VCO輸出端加一個耗能的緩沖器以增加VCO的輸出擺幅[5],這將會加劇高速分頻器的功耗問題。

然而與傳統的全功能D觸發器構成的分頻器相比,源耦合邏輯(SCL)分頻器因其輸入/輸出擺幅小、動態功耗低、轉換速度快,成為高速分頻器的首選[6]。本文在傳統的SCL分頻器基礎上加以改進,使用動態負載代替原來的電阻負載或有源固定負載,在電路工作速度和差分輸出擺幅之間得到了很好的折衷;并且時鐘開關管PMOS和NMOS采用不同的直流偏置,解決了低電壓下直流工作點較難設置的問題。

1 源級耦合(SCL)分頻器

1.1 基本結構及工作原理

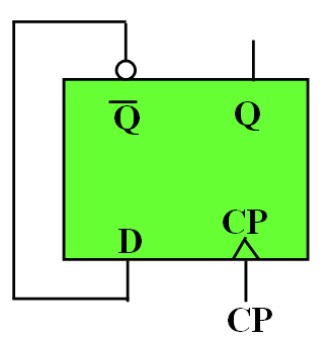

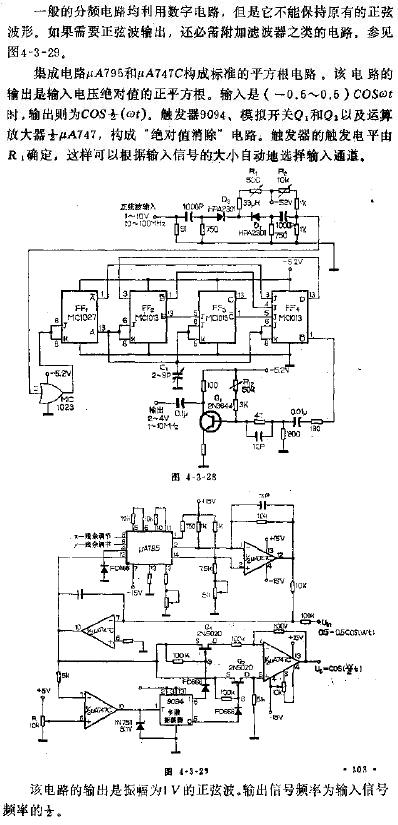

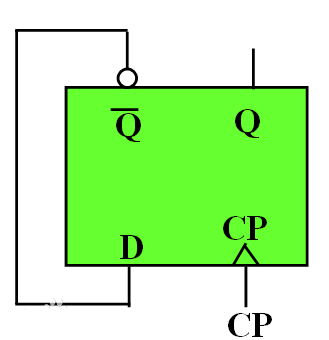

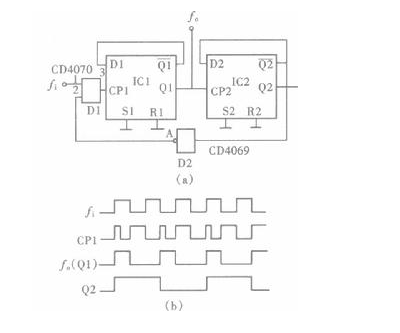

SCL型分頻器通常被認為是工作速度最快的分頻器結構,它可由兩個完全相同的D觸發器或者鎖存器級聯而成,具體電路如圖1所示,其單元電路如圖2所示。

SCL型D觸發器的單元電路包含兩個部分[7]:將輸入信號輸送到輸出的觸發部分(MS)和存儲輸出邏輯電平的鎖存部分(ML)。其中觸發部分由差分對來實現;鎖存部分由一個交叉耦合對(ML)來實現,該結構表現出負阻-2/gm,并通過正反饋大大提高電路工作速度。兩個部分由一個相位互補的時鐘信號驅動,分別用來控制觸發電路和鎖存電路。其具體電路工作過程如下:在輸入時鐘的正半周,圖1中第一級D觸發器處于觸發模式,即輸出跟隨輸入變化;第二級D觸發器處于鎖存模式,保持與前一個時鐘相同的狀態,其輸出經過反相后送入第一級D觸發器。在輸入時鐘的負半周,第一級D觸發器處于鎖存模式;第二級D觸發器轉變為觸發模式,它輸出的狀態將被鎖存到第一級D觸發器中。因此,D觸發器的輸出隨著時鐘狀態的改變而改變,且在每兩個時鐘周期輸出信號完成一個周期的變化,從而輸出的頻率剛好是輸入頻率的一半,實現二分頻功能。

圖2電路中的尾電流源是為了保證電路比較穩定的直流偏置,減小了因輸入時鐘信號的直流電平變化對電路的影響。為了提高工作速度,可以忽略尾電流源,這樣大約能提高20%的工作速度[8],但是同時電路對工藝和溫度的依賴性增加。此外,考慮到電阻阻值的不準確,以及版圖面積大等不利因素,所以在很多設計中用有源負載代替電阻負載,但這樣增大了寄生電容,進而限制了最高工作頻率。

1.2 SCL電路動態特性

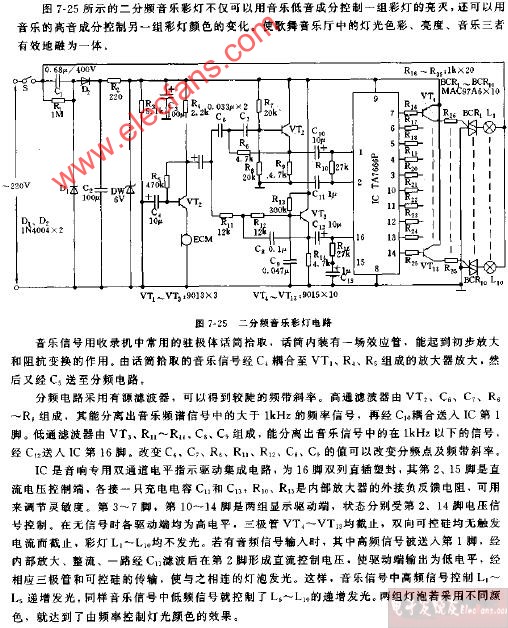

SCL型二分頻器的動態特性如圖3所示,其中fo是沒有外加激勵時電路的自激振蕩頻率,Vclk_min是電路停止自振蕩所需外加的最小時鐘信號的幅度。根據電路工作頻率和外加的時鐘激勵幅度的變化,電路工作于4種不同的狀態[9]:

(1)自振蕩區:如圖1所示,兩級D觸發器級聯并形成閉環環路,當環路滿足巴克豪森振蕩條件時,環路就會發生自激振蕩;但是當輸入時鐘的幅度比較大時,電路會由自振蕩轉入受迫振蕩狀態,振蕩頻率也會向正常工作頻率靠攏,實現二分頻。

(2)正常工作區:能完成二分頻功能。

(3)壓擺率限制區:當輸入時鐘有比較大的上升和下降時間時,會在時鐘過零點時有足夠的時間使電路發生自振蕩,從而影響輸出頻譜的純度。

(4)響應限制區:當輸入時鐘頻率很高時,由于寄生電容的影響,D觸發器充放電不完全,它將無法振蕩到該頻率,導致電路工作失常。

由圖3可以看出,輸入時鐘信號Vclk幅值越小,則電路正常工作的頻率范圍越小。因此,要達到大的工作頻率,Vclk幅值必須較大。一般VCO輸出擺幅都比較大,對于跟在VCO后面的第一級二分頻器,其輸入時鐘的幅度往往不成問題。

2 改進的分頻器電路設計及仿真

2.1 SCL二分頻電路設計

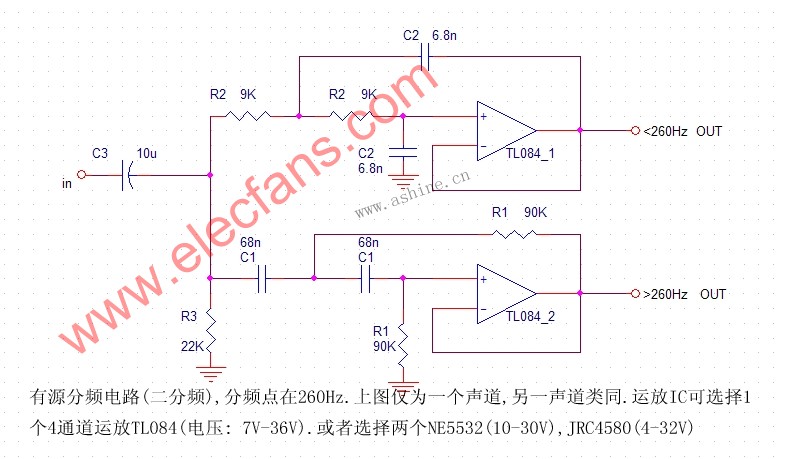

本文主要對SCL電路的負載進行了改進,采用Wang的動態負載結構[10](即讓觸發器的負載隨著輸入信號的變化而變化),使電路的速度得以進一步提高;并且對開關管和負載管采用不同的直流偏置,便于直流工作點的選取,尤其是在低電源電壓的情況下。本文設計的SCL單元電路如圖4所示。

從圖4可以看出, PMOS管起動態電阻的作用。當該D觸發器處于觸發狀態時,PMOS等效為一個很小的負載電阻,這就可以在輸出節點產生比較小的RC時間常數,提高觸發器的工作頻率;當觸發器處于鎖存狀態時,PMOS管等效為一個很大的負載電阻,增大輸出擺幅。這種動態負載的結構比普通電阻負載結構的工作頻率更高,但要同時給NMOS和PMOS管提供合理的偏置會帶來比較大的設計難度。因此,在本文提出的結構中,NMOS和PMOS采用不同的直流偏置,通過合理設計電阻、電容的值,以及外加偏置電壓VBP,就可以控制PMOS管的時鐘信號偏置在需要的直流點;同樣也可以選取NMOS的直流偏置VBN,這樣有利于降低設計的復雜性,特別在低電源電壓下,一個折衷的直流偏置點很難選取。圖4中還有一個尾電流管M1用來保證電路比較穩定的直流偏置。由于本文設計的高速二分頻電路應用于短距離無線接收發機中,與其直接相連的VCO輸出最高頻率為1.92 GHz,并不需要特別高的工作頻率,因此不需要通過去除尾電流源來使電路工作在更高的頻率段。另外,去除尾電流源會使電路輸出擺幅不確定,受工藝和溫度的影響較大;并且會導致SCL分頻器的襯底波動比較大,該波動通過襯底耦合,會加大分頻器的噪聲,或影響到其他電路模塊, 所以本文保留了尾電流源的使用。

2.2 電路仿真結果

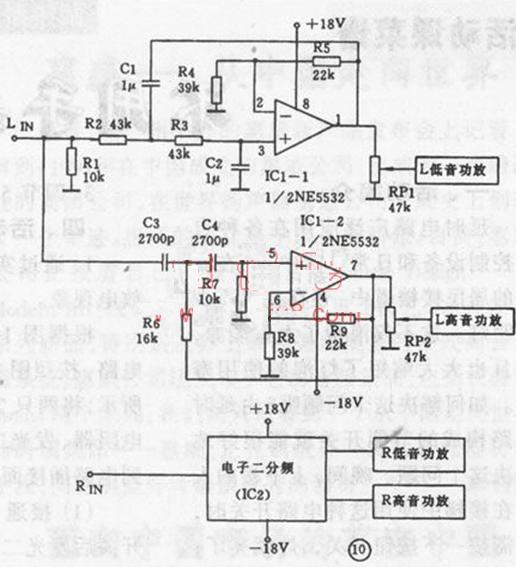

電路采用TSMC 0.18 μm RF CMOS工藝設計實現,并對整體電路進行了仿真、驗證。圖5給出了當輸入時鐘信號頻率為1.92 GHz、幅度為800 mV時的SCL分頻器瞬態仿真結果。從仿真結果可以看到,分頻器輸出波形周期為1.04 ns,很好地實現了二分頻功能;且輸出擺幅較大,在800 mV左右。圖6給出了二分頻器的4個不同相位的瞬態輸出,其每個象限相差90°,以便用于后面的基于相位選擇技術的雙模預分頻電路。

由之前分析可知,SCL二分頻器的正常工作頻率有一定的范圍,且與輸入時鐘信號的幅度有關,因此分頻器有一個最大頻率鎖定范圍。圖7給出了當輸入時鐘幅度從200 mV~1 V變化時,其頻率鎖定范圍的變化情況。從圖中可以看出,隨著輸入時鐘幅度變大,分頻器的鎖定范圍也變大,當幅度為800 mV時,頻率鎖定范圍為200 MHz~2.8 GHz,有較寬的頻率鎖定范圍,滿足VCO輸出頻率范圍的完全覆蓋(所應用的VCO調頻范圍為1.608 GHz~1.92 GHz);本設計的分頻器電路在3 V電源電壓下、工作頻率在1.92 GHz時的功耗為1.15 mW。

本文設計了一種基于源極耦合邏輯技術的高速正交二分頻器電路。電路沿用了傳統的SCL二分頻器結構并對其適當改進,采用動態負載代替電阻負載,使負載阻值隨著輸入信號變化而變化,有利于工作頻率的提高和輸出擺幅的增大。電路PMOS和NMOS管采用不同的直流偏置,大大減小了直流工作點選取的復雜度。采用TSMC 0.18 μm RF CMOS工藝進行了設計驗證,在1.92 GHz輸入時鐘頻率下能正常實現正交二分頻,有較寬的鎖定范圍,且在3 V電源電壓下的電路功耗僅為1.15 mW。

電子發燒友App

電子發燒友App

評論