摘要:本文介紹了Dallas Semiconductor對傳統8051微控制器的改進技術,創造了引腳兼容的高性能替代產品,能夠達到33 MIP的速度。除此之外,還包括多數據指針、擴展存儲器尋址(達16MB)和閃存,大大提高的器件的速度和有效性。

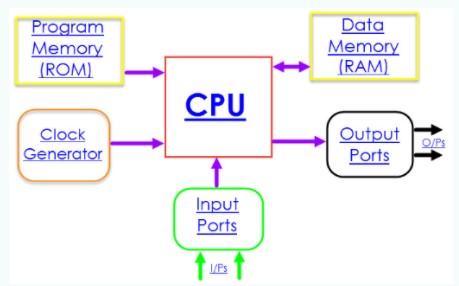

系統設計者都知道,微控制器是所有嵌入式系統的心臟—各種系統活動的策源地。過去18年來,Dallas Semiconductor (Maxim Integrated Products的全資子公司)對無處不在的8051微控制器進行了重新定義。也許,過去十年來對于微控制器的最大改進,表現在其執行指令的速度方面。我們的單周期處理器達到了振奮人心的性能目標—每機器周期一個時鐘,目前為33百萬指令每秒(MIPS)。基于這個內核,我們的安全型、網絡型、和混合信號8051微控制器家族在功能集成和創新性方面始終為業界典范。

為什么將創新的微控制器家族建立在古老的8051指令集之上?道理很簡單,因為它是世界范圍內最為流行的8位微控制器架構之一。這種指令集簡單易懂,深受嵌入式系統設計者的喜愛。許多指令可直接訪問I/O引腳,便于迅速操作(位操作)外圍設備。種類繁多的片內外設具有幾乎無限種組合方式。此外,用于8051微控制器家族的開發工具隨處可見,這樣,你可以非常容易地,而且不需要花費很高成本,就可以著手一個應用的開發。

由于采用非易失SRAM技術,數據和程序存儲器都可重新在系統編程,允許逐字節、運行中編程。而在一個標準的微控制器系統中,要重新編程就必須將程序存儲器從系統中拿下來(EPROM),或者進行塊擦除,擦除過程中要禁止存儲器訪問(flash)。基于非易失SRAM的微控制器的編程非常容易并且迅速,可利用PC或一個專用編程器通過串口對其進行編程。駐留于ROM的自舉裝載器直接將程序或數據下載到微控制器,實現快速調試或現場升級。

非易失SRAM獨具特色的優點為系統固件的安全性提供了新的手段。由于自舉裝載器完全控制著向非易失SRAM的程序裝載,我們采用一個40位或80位的加密密鑰對地址和數據總線進行加密。任何裝載到微控制器內的程序或數據在存入SRAM之前都自動進行了加密。這種加密手段可以防止黑客竊取微控制器中的程序或數據。指令運行期間,微控制器取出經過加密的操作碼,在一個機器周期內完成解密并執行。由于采用了非易失SRAM,允許全速進行讀/寫訪問,指令解密不會引起任何延遲。

這些安全特性在DS5250中達到了極致,這是一種安全型8051微控制器,廣泛用于世界各地的金融終端和支付系統。這種抗攻擊微控制器整合了一個4時鐘機器周期內核,以及用于程序存儲器加密的增強型三DES加密邏輯。另外,還增加了侵入探測和片內篡改檢測器,一旦檢測到有篡改發生便自動擦除存儲器。一個內部的微探針屏蔽層可防止對晶片進行篡改。還有,非易失SRAM對于要求高度安全的應用來講可謂是最佳選擇。由于可以高速寫入,微控制器能夠迅速擦除機密信息和敏感數據,這一點勝出了任何其他類型的存儲器。

DS5250是唯一一款既提供最高水準的安全性,又能全速運行每條指令的微控制器。

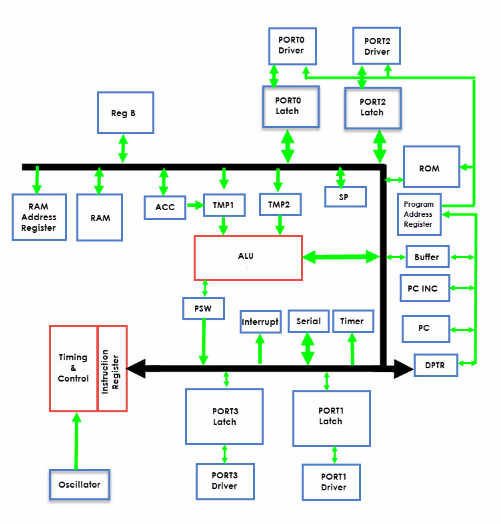

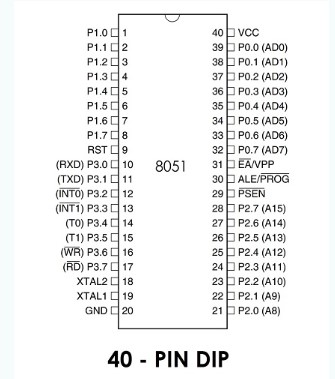

性能的瓶頸在于過時的、誕生于上個世紀七十年代的8051微控制器處理內核。盡管外部晶振的速度已接近40MHz,傳統的8051仍然要求12個時鐘才能運行一個機器周期。每條指令需要1到4個機器周期,這意味著執行一條指令就需要少則12多則48個時鐘周期。這樣,吞吐率被限制于僅3MIPS,即便是運行一串象NOP這樣的單周期指令(圖1)。

圖1. 由于每機器周期所需時鐘數的降低,相同指令集的性能提高了3倍以上(對比12時鐘、4時鐘和1時鐘每機器周期)。

1991年,我們開始著手重新設計8051微控制器,以期獲得性能上的突破。設計小組首先對傳統8051的設計進行了分析。我們發現,原先的12時鐘每機器周期架構中存在著巨大的浪費:多數指令被強制去執行啞周期。工程師們徹底重構了CPU,每個機器周期只需4個時鐘而非12個。第二條內部數據總線消除了阻礙性能發揮的結構性瓶頸。高功率I/O驅動器提升了訪問外部存儲器時口線的轉換速度。所有內置的外圍設備,例如定時器和串行口,都運行于更高的時鐘頻率。不過,在此變革之路上的每一步,都有一條絕對不變的準則―指令集必須保持和8051指令集操作碼的兼容性。

最終,一種全新的基于8051的微控制器誕生了,相比原來的8051核效率提升了三倍,相同的頻率下,大多數指令的運行速度提高了三倍。除了內核效率提升以外,大多數器件的最高外部振蕩頻率也提高到了33MHz或40MHz。飽受古老、低速的8051困擾的系統設計者現在無需修改軟件,就可輕易地將他們的系統升級到最高10MIPS的速度。

除了速度方面的改進以外,重新設計的內核也帶來了另外一個好處:更低的功率消耗。基本物理法則告訴我們,數字電路的功率消耗正比于有開關動作的晶體管數量以及開關的速率(頻率)。由于新的內核每機器周期使用更少的振蕩周期,執行每條指令所需的能量比傳統8051顯著降低了。

另外,特殊的功率管理模式通過軟件可配置的內部時鐘分頻器,可以臨時性地降低微控制器的功耗。通過將機器周期速率由4時鐘每機器周期降低到64或256時鐘每機器周期,可進一步降低功耗。回切功能使器件在接收到一個外部中斷或檢測到一個串行口起始位后立即返回到除4模式。這個特性允許器件在工作較少時保持低功耗守候狀態,必要時又可迅速恢復全速工作狀態。圖2顯示了不同模式中的相對功率消耗。

圖2. 在工作量降低期間,我們的功率管理模式消耗的電流比閑置模式還低,而且CPU仍處于活動狀態。

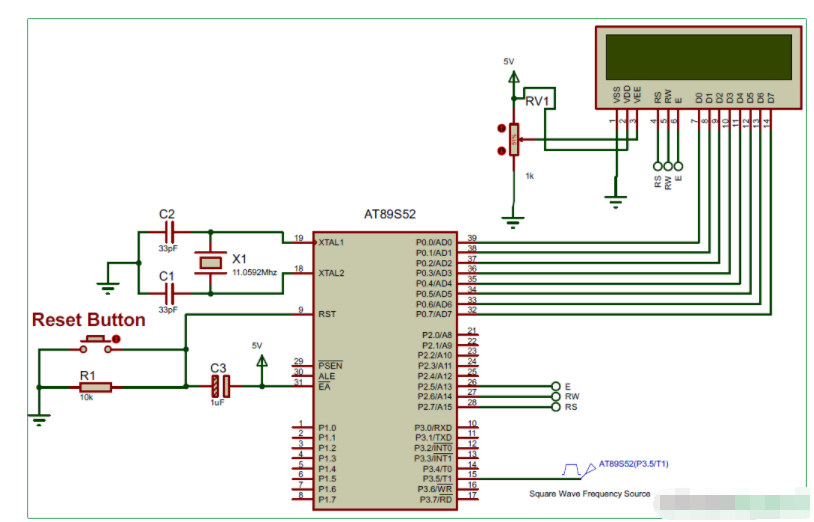

最終,我們推出了全新的DS89C430/DS89C450—―超高性能、每機器周期一個時鐘的微控制器,運行速率高達33MIPS (圖3)。這些器件突破了原有的性能障礙,以8位微控制器的價格,提供16位的性能。這些微控制器提供多種不同的總線尋址模式,允許用戶按照特定應用要求,對處理器的工作進行優化。最為重要的是,它們保持了與8051指令集100%的兼容性,同時,又能夠以更高的速度運行現有的8051應用,速度高出任何一種其它基于8051的微控制器。

圖3. DS89C430 33MIPS的性能遠超競爭對手。

除了閃電般快速的內核,DS89C430/DS89C450還整合了多達64kB可在系統編程的閃速存儲器。駐留于ROM的自舉裝載器允許用戶在任意時間對微控制器代碼進行調整,使設計非常靈活。不同于其它使用專有或非標接口的微控制器,DS89C430的自舉裝載器可由標準PC,使用任何終端仿真軟件,通過串行口進行操作。

有些設計者采用分區切換的辦法來擴展尋址空間。I/O線被充作地址線使用,以犧牲部分I/O資源為代價換取更多存儲空間。但這種做法有兩個重要缺陷。首先,代碼必須以64kB或更小的單位分段,這是一件很費時的工作,因為每次調整代碼后都必須重新進行分段。第二,每一次代碼跨段時都必須通過專門的軟件流程去切換I/O線。由于這方面的軟件開銷,會使系統的總體性能有所下降。

更好的解決方案應該是給器件配備更寬的地址總線。DS80C400便是如此,它具有24位地址總線,可直接尋址16MB的程序存儲器和16MB的數據存儲器。而新功能的實現,并沒有依靠8051指令集之外的新增操作碼。提供兩種總線模式,第一種頁尋址模式采用了先進的自動分區切換技術,極大地加速了擴展存儲器的訪問,同時又保持了與傳統8051編譯器二進制碼的兼容性。第二種連續模式可透明尋址整個16MB存儲空間,但要求編譯器能夠產生24位地址所需的額外的操作數。更大的地址空間允許更大的程序以更高的速度運作,為微控制器開拓了更廣的應用空間,例如大型的數學函數庫、檢索表、甚至是Java?虛擬機,后者已得到網絡型微控制器DS80C390和DS80C400的支持,并成為微型因特網接口(TINI?)運行環境的一部分。

前進道路上的每一步都有一個必須遵循的條件―指令集必須保持與8051指令集操作碼的兼容性。

DS89C430保持了與8051指令集100%的兼容性,因此它可直接運行原來的8051應用,而速度仍快于任何其他基于8051的微控制器。

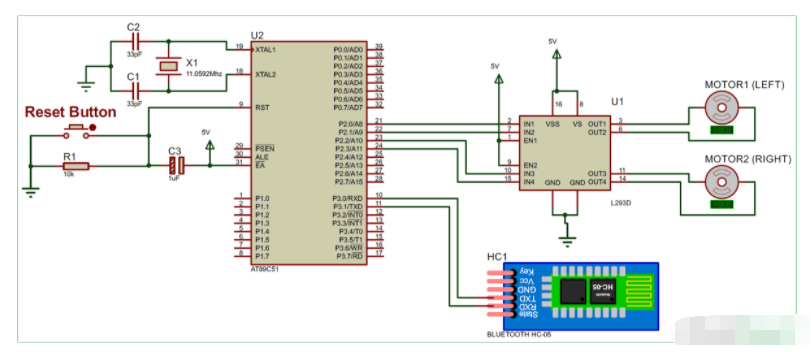

這種操作的低效率在執行塊拷貝操作時尤為突出,這種操作需要將數據從MOVX存儲器中的某個位置轉移到另一位置。在塊拷貝操作中,單一數據指針必須兼作源地址和目的地址指針。在傳統8051微控制器中,這種操作是一個復雜、多步驟的過程:

也許你已經注意到了,上述過程中幾乎有一半的步驟,用來將單個數據指針在目標和源地址之間換來換去,這會妨礙整體性能的發揮。解決方案是增加第二個數據指針,為源和目標指針分配專門的寄存器。有了第二個數據指針,很多數據操作可由硬件完成,降低了軟件開銷。雙數據指針可獨立訪問,通過專門的數據指針選擇位可以選擇執行MOVX指令時,當前活動的數據指針。采用雙數據指針,同樣的塊拷貝操作所需的步驟要少很多:

只需一次初始化:

圖4. 雙數據指針提高了塊拷貝操作的速度。

但是,有競真力的設計不僅僅要求速度。更復雜的應用需要更大的程序空間,因此,我們正在將直接替換原8051的微控制器系列擴充為64kB閃存。我們的新產品流水線正在將更多的外設設計進來,以便提升嵌入式系統的能力,同時降低板上空間需求。網絡型微控制器具有一些更先進的功能,包括CAN,以太網,及1-Wire?等多層次組網能力。安全微控制器具有硬件實現的數學加速器,用于公鑰加密系統,并在檢測到有篡改發生時,迅速刪除密鑰。混合信號微控制器能夠處理來自真實世界的信號,用來實現更好的終端設備。

我們對于微控制器性能的追求超越了8051內核。我們的一個新的系列,MAXQ? 16位RISC微控制器達到了更高的性能-功耗比。引領我們到達此目標的途徑是單周期指令。單周期指令增加了指令帶寬,從而可提供更高的性能,而且,有可能通過降低時鐘頻率來降低功耗。除了長跳轉/長調用和某些擴展寄存器的訪問外,所有MAXQ指令都在單個時鐘周期內執行。雖然許多RISC微控制器聲稱支持單周期指令,但事實通常是只有一部分指令或尋址模式是單周期的。在MAXQ中,絕大部分是單周期指令。

另外,MAXQ架構提高了時鐘周期的利用率,因為其單周期操作并未依賴指令流水線(常見于許多RISC微控制器)。MAXQ指令的譯碼和執行硬件是如此之簡單(且快速),以致它們可以和取指在同一個時鐘周期內完成,且對最高工作頻率的影響很小。為了說明取消指令流水線的優點,我們來考察一個流水線結構的普通RISC CPU。當遇到程序分支時,CPU需要一個或更多時鐘周期(因流水線深度而異)來將程序轉向目標分支地址,拋棄已取得的指令。顯然,將時鐘周期用在拋棄指令(而非執行指令)上面是一種浪費且令人不快的做法,因為它降低了性能且增加了功耗。盡管這種操作令人不快,CPU竊取時鐘來重裝流水線仍然是這種架構不可避免的一個瑕疵。MAXQ架構區別于其他8位和16位RISC微控制器的一個顯著特點就是,單周期指令的執行不依賴于指令流水線(也就避免了它所帶來的時鐘周期浪費問題)。

有關如何以最低的功耗獲取最高的性能方面的更多信息,參見白皮書“Teaching Old Dogs New Tricks: Improving the Power Efficiency of 8051-Based Designs” (English only)。

系統設計者都知道,微控制器是所有嵌入式系統的心臟—各種系統活動的策源地。過去18年來,Dallas Semiconductor (Maxim Integrated Products的全資子公司)對無處不在的8051微控制器進行了重新定義。也許,過去十年來對于微控制器的最大改進,表現在其執行指令的速度方面。我們的單周期處理器達到了振奮人心的性能目標—每機器周期一個時鐘,目前為33百萬指令每秒(MIPS)。基于這個內核,我們的安全型、網絡型、和混合信號8051微控制器家族在功能集成和創新性方面始終為業界典范。

為什么將創新的微控制器家族建立在古老的8051指令集之上?道理很簡單,因為它是世界范圍內最為流行的8位微控制器架構之一。這種指令集簡單易懂,深受嵌入式系統設計者的喜愛。許多指令可直接訪問I/O引腳,便于迅速操作(位操作)外圍設備。種類繁多的片內外設具有幾乎無限種組合方式。此外,用于8051微控制器家族的開發工具隨處可見,這樣,你可以非常容易地,而且不需要花費很高成本,就可以著手一個應用的開發。

安全及保密

1987年,Dallas Semiconductor/Maxim推出了DS5000T,一款獨立開發的,基于8051指令集和功能集的新型微控制器。為了提供新的性能和優勢,工程師們將設計建立在非易失SRAM技術之上,而非傳統的EPROM。仰賴其居于領導地位的低功耗技術,存儲器分區和電池備份電路被直接集成到微控制器晶片上。這種系統的主要優勢在于其速度。其他類型的非易失存儲器的寫操作通常很慢,但是非易失SRAM能夠在很高的速度下,在單個周期內讀出和寫入。這對于高速、非易失數據采集應用來講非常理想,這些應用常常要求捕捉實時數據。配合一個外部SRAM和電池,就構成完整的微控制器系統,具有多達64kB的非易失程序和數據存儲空間。由于采用非易失SRAM技術,數據和程序存儲器都可重新在系統編程,允許逐字節、運行中編程。而在一個標準的微控制器系統中,要重新編程就必須將程序存儲器從系統中拿下來(EPROM),或者進行塊擦除,擦除過程中要禁止存儲器訪問(flash)。基于非易失SRAM的微控制器的編程非常容易并且迅速,可利用PC或一個專用編程器通過串口對其進行編程。駐留于ROM的自舉裝載器直接將程序或數據下載到微控制器,實現快速調試或現場升級。

非易失SRAM獨具特色的優點為系統固件的安全性提供了新的手段。由于自舉裝載器完全控制著向非易失SRAM的程序裝載,我們采用一個40位或80位的加密密鑰對地址和數據總線進行加密。任何裝載到微控制器內的程序或數據在存入SRAM之前都自動進行了加密。這種加密手段可以防止黑客竊取微控制器中的程序或數據。指令運行期間,微控制器取出經過加密的操作碼,在一個機器周期內完成解密并執行。由于采用了非易失SRAM,允許全速進行讀/寫訪問,指令解密不會引起任何延遲。

這些安全特性在DS5250中達到了極致,這是一種安全型8051微控制器,廣泛用于世界各地的金融終端和支付系統。這種抗攻擊微控制器整合了一個4時鐘機器周期內核,以及用于程序存儲器加密的增強型三DES加密邏輯。另外,還增加了侵入探測和片內篡改檢測器,一旦檢測到有篡改發生便自動擦除存儲器。一個內部的微探針屏蔽層可防止對晶片進行篡改。還有,非易失SRAM對于要求高度安全的應用來講可謂是最佳選擇。由于可以高速寫入,微控制器能夠迅速擦除機密信息和敏感數據,這一點勝出了任何其他類型的存儲器。

DS5250是唯一一款既提供最高水準的安全性,又能全速運行每條指令的微控制器。

高速度,低功耗

8051處理器核自從誕生之日起(二十世紀七十年代末到八十年代)就基本停滯不前,而嵌入式系統卻并非如此。通過增加新的軟件特性和外圍設備,系統設計者不斷地對其基于8051的應用進行了改進和升級。這種“功能蔓延”將現有的8051性能推向了極限。不幸的是,對于8051內核的改進卻沒有跟得上,看起來,系統設計者似乎不得不轉向其他的處理器,并花費昂貴的代價去重新設計和更新他們的系統。性能的瓶頸在于過時的、誕生于上個世紀七十年代的8051微控制器處理內核。盡管外部晶振的速度已接近40MHz,傳統的8051仍然要求12個時鐘才能運行一個機器周期。每條指令需要1到4個機器周期,這意味著執行一條指令就需要少則12多則48個時鐘周期。這樣,吞吐率被限制于僅3MIPS,即便是運行一串象NOP這樣的單周期指令(圖1)。

圖1. 由于每機器周期所需時鐘數的降低,相同指令集的性能提高了3倍以上(對比12時鐘、4時鐘和1時鐘每機器周期)。

1991年,我們開始著手重新設計8051微控制器,以期獲得性能上的突破。設計小組首先對傳統8051的設計進行了分析。我們發現,原先的12時鐘每機器周期架構中存在著巨大的浪費:多數指令被強制去執行啞周期。工程師們徹底重構了CPU,每個機器周期只需4個時鐘而非12個。第二條內部數據總線消除了阻礙性能發揮的結構性瓶頸。高功率I/O驅動器提升了訪問外部存儲器時口線的轉換速度。所有內置的外圍設備,例如定時器和串行口,都運行于更高的時鐘頻率。不過,在此變革之路上的每一步,都有一條絕對不變的準則―指令集必須保持和8051指令集操作碼的兼容性。

最終,一種全新的基于8051的微控制器誕生了,相比原來的8051核效率提升了三倍,相同的頻率下,大多數指令的運行速度提高了三倍。除了內核效率提升以外,大多數器件的最高外部振蕩頻率也提高到了33MHz或40MHz。飽受古老、低速的8051困擾的系統設計者現在無需修改軟件,就可輕易地將他們的系統升級到最高10MIPS的速度。

除了速度方面的改進以外,重新設計的內核也帶來了另外一個好處:更低的功率消耗。基本物理法則告訴我們,數字電路的功率消耗正比于有開關動作的晶體管數量以及開關的速率(頻率)。由于新的內核每機器周期使用更少的振蕩周期,執行每條指令所需的能量比傳統8051顯著降低了。

另外,特殊的功率管理模式通過軟件可配置的內部時鐘分頻器,可以臨時性地降低微控制器的功耗。通過將機器周期速率由4時鐘每機器周期降低到64或256時鐘每機器周期,可進一步降低功耗。回切功能使器件在接收到一個外部中斷或檢測到一個串行口起始位后立即返回到除4模式。這個特性允許器件在工作較少時保持低功耗守候狀態,必要時又可迅速恢復全速工作狀態。圖2顯示了不同模式中的相對功率消耗。

圖2. 在工作量降低期間,我們的功率管理模式消耗的電流比閑置模式還低,而且CPU仍處于活動狀態。

超越33MIPS

Dallas Semiconductor/Maxim于1997年開始設計一個新的內核,以獲得更高的性能。基于8051的應用在不斷發展,用戶在呼喚更高的性能。設計團隊將他們的目標鎖定在性能的頂峰:運行8051指令集,但是每機器周期僅一個時鐘的全新微控制器。采用高度并行架構和新的制造工藝,一種引腳對引腳兼容,直接替換原有8051的設計問世了。最終,我們推出了全新的DS89C430/DS89C450—―超高性能、每機器周期一個時鐘的微控制器,運行速率高達33MIPS (圖3)。這些器件突破了原有的性能障礙,以8位微控制器的價格,提供16位的性能。這些微控制器提供多種不同的總線尋址模式,允許用戶按照特定應用要求,對處理器的工作進行優化。最為重要的是,它們保持了與8051指令集100%的兼容性,同時,又能夠以更高的速度運行現有的8051應用,速度高出任何一種其它基于8051的微控制器。

圖3. DS89C430 33MIPS的性能遠超競爭對手。

除了閃電般快速的內核,DS89C430/DS89C450還整合了多達64kB可在系統編程的閃速存儲器。駐留于ROM的自舉裝載器允許用戶在任意時間對微控制器代碼進行調整,使設計非常靈活。不同于其它使用專有或非標接口的微控制器,DS89C430的自舉裝載器可由標準PC,使用任何終端仿真軟件,通過串行口進行操作。

韓信用兵,多多益善

如果程序員沒有足夠的存儲器地址空間可以支配的話,速度方面的優勢將無從施展。傳統8051采用16位存儲器總線,使存儲器空間限制在64kB以內。對于有些應用,這樣有限的存儲空間已經足夠了。但是隨著應用的升級,代碼的復雜性和規模迅速膨脹,我們意識到,這類應用需要一個解決方案,同時還要盡可能保持與8051的兼容性。有些設計者采用分區切換的辦法來擴展尋址空間。I/O線被充作地址線使用,以犧牲部分I/O資源為代價換取更多存儲空間。但這種做法有兩個重要缺陷。首先,代碼必須以64kB或更小的單位分段,這是一件很費時的工作,因為每次調整代碼后都必須重新進行分段。第二,每一次代碼跨段時都必須通過專門的軟件流程去切換I/O線。由于這方面的軟件開銷,會使系統的總體性能有所下降。

更好的解決方案應該是給器件配備更寬的地址總線。DS80C400便是如此,它具有24位地址總線,可直接尋址16MB的程序存儲器和16MB的數據存儲器。而新功能的實現,并沒有依靠8051指令集之外的新增操作碼。提供兩種總線模式,第一種頁尋址模式采用了先進的自動分區切換技術,極大地加速了擴展存儲器的訪問,同時又保持了與傳統8051編譯器二進制碼的兼容性。第二種連續模式可透明尋址整個16MB存儲空間,但要求編譯器能夠產生24位地址所需的額外的操作數。更大的地址空間允許更大的程序以更高的速度運作,為微控制器開拓了更廣的應用空間,例如大型的數學函數庫、檢索表、甚至是Java?虛擬機,后者已得到網絡型微控制器DS80C390和DS80C400的支持,并成為微型因特網接口(TINI?)運行環境的一部分。

前進道路上的每一步都有一個必須遵循的條件―指令集必須保持與8051指令集操作碼的兼容性。

成倍提升性能的數據指針設計

為了避免產生新的性能瓶頸,有必要對芯片的各個方面都進行長遠的改進。其中最為重要的改進之一是針對MOVX數據存儲器訪問的改進。數據存儲器的操作對于原8051來講是一件很麻煩的事情。要訪問MOVX存儲器中的單個字節,首先需要花費數個周期裝載一個16位數據指針,然后才能對目標地址進行讀寫操作。DS89C430保持了與8051指令集100%的兼容性,因此它可直接運行原來的8051應用,而速度仍快于任何其他基于8051的微控制器。

這種操作的低效率在執行塊拷貝操作時尤為突出,這種操作需要將數據從MOVX存儲器中的某個位置轉移到另一位置。在塊拷貝操作中,單一數據指針必須兼作源地址和目的地址指針。在傳統8051微控制器中,這種操作是一個復雜、多步驟的過程:

- 裝載源地址到數據指針。

- 遞增或調整數據指針指向下一單元。

- 從MOVX存儲器取數據到累加器。

- 保存源地址到寄存器。

- 裝載目標地址到數據指針。

- 遞增或調整數據指針指向下一單元。

- 數據由累加器寫入MOVX存儲器。

- 保存目標地址到寄存器。

也許你已經注意到了,上述過程中幾乎有一半的步驟,用來將單個數據指針在目標和源地址之間換來換去,這會妨礙整體性能的發揮。解決方案是增加第二個數據指針,為源和目標指針分配專門的寄存器。有了第二個數據指針,很多數據操作可由硬件完成,降低了軟件開銷。雙數據指針可獨立訪問,通過專門的數據指針選擇位可以選擇執行MOVX指令時,當前活動的數據指針。采用雙數據指針,同樣的塊拷貝操作所需的步驟要少很多:

只需一次初始化:

- 第一數據指針初始化為源地址。

- 第二數據指針初始化為目標地址。

- 取數據到累加器。

- 遞增或調整第一數據指針指向下一單元。

- 選擇第二數據指針。

- 數據由累加器寫入MOVX存儲器。

- 遞增或調整數據指針指向下一單元。

圖4. 雙數據指針提高了塊拷貝操作的速度。

前景展望

隨著應用越來越高的速度要求,Maxim正在努力工作以超越一個又一個性能極限。無論是其更快的堆棧訪問速度、擴展的尋址空間,抑或是基本處理速度,我們的微控制器設計終能滿足嵌入式系統設計者的各種要求。但是,有競真力的設計不僅僅要求速度。更復雜的應用需要更大的程序空間,因此,我們正在將直接替換原8051的微控制器系列擴充為64kB閃存。我們的新產品流水線正在將更多的外設設計進來,以便提升嵌入式系統的能力,同時降低板上空間需求。網絡型微控制器具有一些更先進的功能,包括CAN,以太網,及1-Wire?等多層次組網能力。安全微控制器具有硬件實現的數學加速器,用于公鑰加密系統,并在檢測到有篡改發生時,迅速刪除密鑰。混合信號微控制器能夠處理來自真實世界的信號,用來實現更好的終端設備。

我們對于微控制器性能的追求超越了8051內核。我們的一個新的系列,MAXQ? 16位RISC微控制器達到了更高的性能-功耗比。引領我們到達此目標的途徑是單周期指令。單周期指令增加了指令帶寬,從而可提供更高的性能,而且,有可能通過降低時鐘頻率來降低功耗。除了長跳轉/長調用和某些擴展寄存器的訪問外,所有MAXQ指令都在單個時鐘周期內執行。雖然許多RISC微控制器聲稱支持單周期指令,但事實通常是只有一部分指令或尋址模式是單周期的。在MAXQ中,絕大部分是單周期指令。

另外,MAXQ架構提高了時鐘周期的利用率,因為其單周期操作并未依賴指令流水線(常見于許多RISC微控制器)。MAXQ指令的譯碼和執行硬件是如此之簡單(且快速),以致它們可以和取指在同一個時鐘周期內完成,且對最高工作頻率的影響很小。為了說明取消指令流水線的優點,我們來考察一個流水線結構的普通RISC CPU。當遇到程序分支時,CPU需要一個或更多時鐘周期(因流水線深度而異)來將程序轉向目標分支地址,拋棄已取得的指令。顯然,將時鐘周期用在拋棄指令(而非執行指令)上面是一種浪費且令人不快的做法,因為它降低了性能且增加了功耗。盡管這種操作令人不快,CPU竊取時鐘來重裝流水線仍然是這種架構不可避免的一個瑕疵。MAXQ架構區別于其他8位和16位RISC微控制器的一個顯著特點就是,單周期指令的執行不依賴于指令流水線(也就避免了它所帶來的時鐘周期浪費問題)。

有關如何以最低的功耗獲取最高的性能方面的更多信息,參見白皮書“Teaching Old Dogs New Tricks: Improving the Power Efficiency of 8051-Based Designs” (English only)。

電子發燒友App

電子發燒友App

評論