資料介紹

1 引言

隨著同防工業(yè)對(duì)精確制導(dǎo)武器要求的不斷提高,武器系統(tǒng)總體設(shè)計(jì)方案的日趨復(fù)雜,以及電子元器件水平的飛速發(fā)展。導(dǎo)引頭信號(hào)處理器的功能越來(lái)越復(fù)雜,硬件規(guī)模越來(lái)越大.處理速度也越來(lái)越高.而且產(chǎn)品的更新速度加快,生命周期縮短。實(shí)現(xiàn)功能強(qiáng)、性能指標(biāo)高、抗干擾能力強(qiáng)、工作穩(wěn)定可靠、體積小、功耗低、結(jié)構(gòu)緊湊合理符合彈載要求的導(dǎo)引頭信號(hào)處理器已經(jīng)勢(shì)在必行。過去單一采用DSP處理器搭建信號(hào)處理器已經(jīng)不能滿足要求.FPGA+DSP的導(dǎo)引頭信號(hào)處理結(jié)構(gòu)成為當(dāng)前以及未來(lái)一段時(shí)間的主流。

FPGA和DSP處理器具有截然不同的架構(gòu),在一種器件上非常有效的算法.在另一種器件上可能效率會(huì)非常低。如果目標(biāo)要求大量的并行處理或者最大的多通道流量,那么單純基于DSP的硬件系統(tǒng)就可能需要更大的面積,成本或功耗。一個(gè)FPGA僅在一個(gè)器件上就能高提供多達(dá)550個(gè)并行乘法和累加運(yùn)算,從而以較少的器件和較低的功耗提供同樣的性能。但對(duì)于定期系數(shù)更新,決策控制任務(wù)或者高速串行處理任務(wù),F(xiàn)PGA的優(yōu)化程度遠(yuǎn)不如DSP。

FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),兼顧了速度和靈活性。本文以導(dǎo)引頭信號(hào)處理系統(tǒng)為例說明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)。

2 系統(tǒng)組成

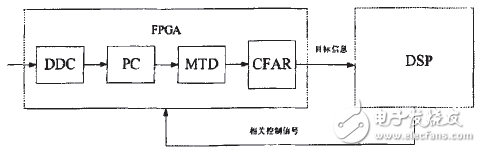

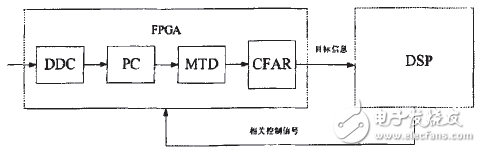

本系統(tǒng)南一片F(xiàn)PGA和一片DSP來(lái)組成,F(xiàn)PGA在實(shí)時(shí)并行計(jì)算實(shí)現(xiàn)標(biāo)準(zhǔn)數(shù)字信號(hào)處理算法的能力遠(yuǎn)強(qiáng)于DSP,因此數(shù)字接收系統(tǒng)信號(hào)處理要用到的FIR濾波、FFT、IFFT等算法,在FPGA中實(shí)現(xiàn)要遠(yuǎn)快于用DSP,且FPGA廠商提供了非常豐富易用的能實(shí)現(xiàn)數(shù)字信號(hào)處理的參數(shù)Core.可以大大簡(jiǎn)化開發(fā)過程。而且,F(xiàn)PGA支持丁程師設(shè)計(jì)高度并行的架構(gòu)以及有大量乘法器和存儲(chǔ)器資源,因此將數(shù)字下變頻(DDC),脈壓(PC),動(dòng)目標(biāo)檢測(cè)(MTD),恒虛警處理(CFAR)等也在FPGA中實(shí)現(xiàn),可有效提高實(shí)時(shí)性,集成度和穩(wěn)定性。而DSP用來(lái)進(jìn)行其他復(fù)雜信號(hào)處理,比如自動(dòng)目標(biāo)識(shí)別、抗干擾等。

FPGA和DSP的通信通過32位的數(shù)據(jù)總線聯(lián)通。FPGA通過此數(shù)據(jù)總線把柃測(cè)得到的目標(biāo)信息傳遞給DSP做后續(xù)處理,DSP則通過數(shù)據(jù)總線傳遞控制信息。

圖1 FPGA+DSP的系統(tǒng)組成框圖

3 FPGA設(shè)計(jì)中的關(guān)鍵技術(shù)

3.1 跨時(shí)鐘域的設(shè)計(jì)

3.1.1基礎(chǔ)

只有最初級(jí)的邏輯電路才使用單一的時(shí)鐘。大多數(shù)與數(shù)據(jù)傳輸相關(guān)的應(yīng)用都有與牛俱來(lái)的挑戰(zhàn),即跨越多個(gè)時(shí)鐘域的數(shù)據(jù)移動(dòng),例如磁盤控制器、CDROM/DVD控制器、調(diào)制解調(diào)器、網(wǎng)卡以及網(wǎng)絡(luò)處理器等。當(dāng)信號(hào)從一個(gè)時(shí)鐘域傳送到另一個(gè)時(shí)鐘域時(shí),出現(xiàn)在新時(shí)鐘域的信號(hào)是異步信號(hào)。

在現(xiàn)代IC、ASIC以及FPGA設(shè)計(jì)中,許多軟件程序可以幫助工程師建立幾百萬(wàn)門的電路。但這些程序都無(wú)法解決信號(hào)同步問題。設(shè)計(jì)者需要了解可靠的設(shè)計(jì)技巧,以減少電路在跨時(shí)鐘域通信時(shí)的故障風(fēng)險(xiǎn)。

從事多時(shí)鐘設(shè)計(jì)的第一步是要理解信號(hào)穩(wěn)定性問題。當(dāng)一個(gè)信號(hào)跨越某個(gè)時(shí)鐘域時(shí).對(duì)新時(shí)鐘域的電路來(lái)說它就是一個(gè)異步信號(hào)。接收該信號(hào)的電路需要對(duì)其進(jìn)行同步。同步可以防止第一級(jí)存儲(chǔ)單元(觸發(fā)器)的亞穩(wěn)態(tài)在新的時(shí)鐘域里傳播蔓延。

亞穩(wěn)態(tài)是指觸發(fā)器無(wú)法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)時(shí),既尤法預(yù)測(cè)該單元的輸}}{電平,也無(wú)法預(yù)測(cè)何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。在這個(gè)穩(wěn)定期問,觸發(fā)器輸出一些中間級(jí)電平,或者可能處于振蕩狀態(tài),并且這種尤用的輸出電平可以滑信號(hào)通道上的各個(gè)觸發(fā)器級(jí)聯(lián)式傳播下去。

由于數(shù)據(jù)率比較低,而FPGA的工作頻率可以很高,所以在雷達(dá)信號(hào)處理機(jī)的FPGA設(shè)計(jì)中,勢(shì)必要引入跨時(shí)鐘域的設(shè)計(jì),例如在某項(xiàng)口中,控制網(wǎng)絡(luò)為10M.脈沖壓縮工作時(shí)鐘為200M,MTD、CFAR為80M,是個(gè)典型的跨時(shí)鐘域設(shè)計(jì)。

隨著同防工業(yè)對(duì)精確制導(dǎo)武器要求的不斷提高,武器系統(tǒng)總體設(shè)計(jì)方案的日趨復(fù)雜,以及電子元器件水平的飛速發(fā)展。導(dǎo)引頭信號(hào)處理器的功能越來(lái)越復(fù)雜,硬件規(guī)模越來(lái)越大.處理速度也越來(lái)越高.而且產(chǎn)品的更新速度加快,生命周期縮短。實(shí)現(xiàn)功能強(qiáng)、性能指標(biāo)高、抗干擾能力強(qiáng)、工作穩(wěn)定可靠、體積小、功耗低、結(jié)構(gòu)緊湊合理符合彈載要求的導(dǎo)引頭信號(hào)處理器已經(jīng)勢(shì)在必行。過去單一采用DSP處理器搭建信號(hào)處理器已經(jīng)不能滿足要求.FPGA+DSP的導(dǎo)引頭信號(hào)處理結(jié)構(gòu)成為當(dāng)前以及未來(lái)一段時(shí)間的主流。

FPGA和DSP處理器具有截然不同的架構(gòu),在一種器件上非常有效的算法.在另一種器件上可能效率會(huì)非常低。如果目標(biāo)要求大量的并行處理或者最大的多通道流量,那么單純基于DSP的硬件系統(tǒng)就可能需要更大的面積,成本或功耗。一個(gè)FPGA僅在一個(gè)器件上就能高提供多達(dá)550個(gè)并行乘法和累加運(yùn)算,從而以較少的器件和較低的功耗提供同樣的性能。但對(duì)于定期系數(shù)更新,決策控制任務(wù)或者高速串行處理任務(wù),F(xiàn)PGA的優(yōu)化程度遠(yuǎn)不如DSP。

FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),兼顧了速度和靈活性。本文以導(dǎo)引頭信號(hào)處理系統(tǒng)為例說明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)。

2 系統(tǒng)組成

本系統(tǒng)南一片F(xiàn)PGA和一片DSP來(lái)組成,F(xiàn)PGA在實(shí)時(shí)并行計(jì)算實(shí)現(xiàn)標(biāo)準(zhǔn)數(shù)字信號(hào)處理算法的能力遠(yuǎn)強(qiáng)于DSP,因此數(shù)字接收系統(tǒng)信號(hào)處理要用到的FIR濾波、FFT、IFFT等算法,在FPGA中實(shí)現(xiàn)要遠(yuǎn)快于用DSP,且FPGA廠商提供了非常豐富易用的能實(shí)現(xiàn)數(shù)字信號(hào)處理的參數(shù)Core.可以大大簡(jiǎn)化開發(fā)過程。而且,F(xiàn)PGA支持丁程師設(shè)計(jì)高度并行的架構(gòu)以及有大量乘法器和存儲(chǔ)器資源,因此將數(shù)字下變頻(DDC),脈壓(PC),動(dòng)目標(biāo)檢測(cè)(MTD),恒虛警處理(CFAR)等也在FPGA中實(shí)現(xiàn),可有效提高實(shí)時(shí)性,集成度和穩(wěn)定性。而DSP用來(lái)進(jìn)行其他復(fù)雜信號(hào)處理,比如自動(dòng)目標(biāo)識(shí)別、抗干擾等。

FPGA和DSP的通信通過32位的數(shù)據(jù)總線聯(lián)通。FPGA通過此數(shù)據(jù)總線把柃測(cè)得到的目標(biāo)信息傳遞給DSP做后續(xù)處理,DSP則通過數(shù)據(jù)總線傳遞控制信息。

圖1 FPGA+DSP的系統(tǒng)組成框圖

3 FPGA設(shè)計(jì)中的關(guān)鍵技術(shù)

3.1 跨時(shí)鐘域的設(shè)計(jì)

3.1.1基礎(chǔ)

只有最初級(jí)的邏輯電路才使用單一的時(shí)鐘。大多數(shù)與數(shù)據(jù)傳輸相關(guān)的應(yīng)用都有與牛俱來(lái)的挑戰(zhàn),即跨越多個(gè)時(shí)鐘域的數(shù)據(jù)移動(dòng),例如磁盤控制器、CDROM/DVD控制器、調(diào)制解調(diào)器、網(wǎng)卡以及網(wǎng)絡(luò)處理器等。當(dāng)信號(hào)從一個(gè)時(shí)鐘域傳送到另一個(gè)時(shí)鐘域時(shí),出現(xiàn)在新時(shí)鐘域的信號(hào)是異步信號(hào)。

在現(xiàn)代IC、ASIC以及FPGA設(shè)計(jì)中,許多軟件程序可以幫助工程師建立幾百萬(wàn)門的電路。但這些程序都無(wú)法解決信號(hào)同步問題。設(shè)計(jì)者需要了解可靠的設(shè)計(jì)技巧,以減少電路在跨時(shí)鐘域通信時(shí)的故障風(fēng)險(xiǎn)。

從事多時(shí)鐘設(shè)計(jì)的第一步是要理解信號(hào)穩(wěn)定性問題。當(dāng)一個(gè)信號(hào)跨越某個(gè)時(shí)鐘域時(shí).對(duì)新時(shí)鐘域的電路來(lái)說它就是一個(gè)異步信號(hào)。接收該信號(hào)的電路需要對(duì)其進(jìn)行同步。同步可以防止第一級(jí)存儲(chǔ)單元(觸發(fā)器)的亞穩(wěn)態(tài)在新的時(shí)鐘域里傳播蔓延。

亞穩(wěn)態(tài)是指觸發(fā)器無(wú)法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)時(shí),既尤法預(yù)測(cè)該單元的輸}}{電平,也無(wú)法預(yù)測(cè)何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。在這個(gè)穩(wěn)定期問,觸發(fā)器輸出一些中間級(jí)電平,或者可能處于振蕩狀態(tài),并且這種尤用的輸出電平可以滑信號(hào)通道上的各個(gè)觸發(fā)器級(jí)聯(lián)式傳播下去。

由于數(shù)據(jù)率比較低,而FPGA的工作頻率可以很高,所以在雷達(dá)信號(hào)處理機(jī)的FPGA設(shè)計(jì)中,勢(shì)必要引入跨時(shí)鐘域的設(shè)計(jì),例如在某項(xiàng)口中,控制網(wǎng)絡(luò)為10M.脈沖壓縮工作時(shí)鐘為200M,MTD、CFAR為80M,是個(gè)典型的跨時(shí)鐘域設(shè)計(jì)。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 《抑制開關(guān)磁阻電機(jī)振動(dòng)的結(jié)構(gòu)設(shè)計(jì)研究》pdf 3次下載

- 《捷聯(lián)導(dǎo)引頭穩(wěn)定與跟蹤技術(shù)》pdf 0次下載

- 基于FPGA+DSP彈載SAR信號(hào)處理系統(tǒng)設(shè)計(jì)

- DSP中MAC的微系統(tǒng)結(jié)構(gòu)設(shè)計(jì)

- 如何進(jìn)行相控陣?yán)走_(dá)導(dǎo)引頭收發(fā)系統(tǒng)的設(shè)計(jì) 21次下載

- 相控陣?yán)走_(dá)導(dǎo)引頭的介紹及其數(shù)字平臺(tái)設(shè)計(jì) 10次下載

- FPGA+DSP導(dǎo)引頭信號(hào)處理中FPGA設(shè)計(jì)的關(guān)鍵技術(shù)解析 1次下載

- 基于導(dǎo)引頭信號(hào)處理系統(tǒng)探究FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù) 1次下載

- 基于FPGA+DSP實(shí)時(shí)圖像采集處理系統(tǒng)設(shè)計(jì) 9次下載

- 脈沖多普勒雷達(dá)導(dǎo)引頭實(shí)時(shí)雜波模型 22次下載

- 相控陣?yán)走_(dá)導(dǎo)引頭捷聯(lián)去耦數(shù)字平臺(tái)設(shè)計(jì) 36次下載

- FPGA+DSP導(dǎo)引頭信號(hào)處理中FPGA設(shè)計(jì)的關(guān)鍵技術(shù)

- FPGA+DSP導(dǎo)引頭信號(hào)處理中FPGA設(shè)計(jì)的關(guān)鍵技術(shù)

- 嵌入式DSP處理器的體系結(jié)構(gòu)設(shè)計(jì)

- 基于DSP Builder的電視導(dǎo)引頭跟蹤控制系統(tǒng)設(shè)計(jì)

- 機(jī)械結(jié)構(gòu)設(shè)計(jì)解決方案 1530次閱讀

- 可編程導(dǎo)引頭模擬器怎么用 788次閱讀

- 基于ML的異構(gòu)金屬材料結(jié)構(gòu)設(shè)計(jì)及性能預(yù)測(cè) 1550次閱讀

- Tesla充電口結(jié)構(gòu)設(shè)計(jì)的變化 1072次閱讀

- 一種基于DSP+FPGA結(jié)構(gòu)的通用飛控計(jì)算機(jī)設(shè)計(jì)方法介紹 2449次閱讀

- 變頻電動(dòng)機(jī)結(jié)構(gòu)設(shè)計(jì)注意事項(xiàng) 4433次閱讀

- 微帶天線的功率容量能否滿足相控陣導(dǎo)引頭的要求? 8937次閱讀

- 淺析FPGA+DSP結(jié)構(gòu)中的配置方式 8358次閱讀

- 關(guān)于FPGA的幾點(diǎn)問題,你了解嗎? 2883次閱讀

- 關(guān)于一種小型、高效反輻射導(dǎo)引頭接收方案的設(shè)計(jì) 6431次閱讀

- 基于FPGA+DSP的視頻控制的智能交通燈設(shè)計(jì) 2182次閱讀

- 一文了解FPGA與DSP的區(qū)別、特點(diǎn)及用途 2.9w次閱讀

- 基于FPGA+DSP架構(gòu)視頻處理系統(tǒng)設(shè)計(jì) 1321次閱讀

- ADSS光纜結(jié)構(gòu)設(shè)計(jì)與施工問題的探討 2655次閱讀

- FPGA+DSP的高速通信接口設(shè)計(jì)與實(shí)現(xiàn) 7762次閱讀

下載排行

本周

- 1DC電源插座圖紙

- 0.67 MB | 2次下載 | 免費(fèi)

- 2AN158 GD32VW553 Wi-Fi開發(fā)指南

- 1.51MB | 2次下載 | 免費(fèi)

- 3AN148 GD32VW553射頻硬件開發(fā)指南

- 2.07MB | 1次下載 | 免費(fèi)

- 4AN111-LTC3219用戶指南

- 84.32KB | 次下載 | 免費(fèi)

- 5AN153-用于電源系統(tǒng)管理的Linduino

- 1.38MB | 次下載 | 免費(fèi)

- 6AN-283: Σ-Δ型ADC和DAC[中文版]

- 677.86KB | 次下載 | 免費(fèi)

- 7SM2018E 支持可控硅調(diào)光線性恒流控制芯片

- 402.24 KB | 次下載 | 免費(fèi)

- 8AN-1308: 電流檢測(cè)放大器共模階躍響應(yīng)

- 545.42KB | 次下載 | 免費(fèi)

本月

- 1ADI高性能電源管理解決方案

- 2.43 MB | 450次下載 | 免費(fèi)

- 2免費(fèi)開源CC3D飛控資料(電路圖&PCB源文件、BOM、

- 5.67 MB | 138次下載 | 1 積分

- 3基于STM32單片機(jī)智能手環(huán)心率計(jì)步器體溫顯示設(shè)計(jì)

- 0.10 MB | 130次下載 | 免費(fèi)

- 4使用單片機(jī)實(shí)現(xiàn)七人表決器的程序和仿真資料免費(fèi)下載

- 2.96 MB | 44次下載 | 免費(fèi)

- 53314A函數(shù)發(fā)生器維修手冊(cè)

- 16.30 MB | 31次下載 | 免費(fèi)

- 6美的電磁爐維修手冊(cè)大全

- 1.56 MB | 24次下載 | 5 積分

- 7如何正確測(cè)試電源的紋波

- 0.36 MB | 17次下載 | 免費(fèi)

- 8感應(yīng)筆電路圖

- 0.06 MB | 10次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935121次下載 | 10 積分

- 2開源硬件-PMP21529.1-4 開關(guān)降壓/升壓雙向直流/直流轉(zhuǎn)換器 PCB layout 設(shè)計(jì)

- 1.48MB | 420062次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233088次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191367次下載 | 10 積分

- 5十天學(xué)會(huì)AVR單片機(jī)與C語(yǔ)言視頻教程 下載

- 158M | 183335次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81581次下載 | 10 積分

- 7Keil工具M(jìn)DK-Arm免費(fèi)下載

- 0.02 MB | 73810次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65988次下載 | 10 積分

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論