資料介紹

當前,許多領(lǐng)域越來越多地要求具有高精度A/D轉(zhuǎn)換和實時處理功能。同時,市場對支持更復雜的顯示和通信接口的要求也在提高,如環(huán)境監(jiān)測、電表、醫(yī)療設(shè)備、便攜式數(shù)據(jù)采集以及工業(yè)傳感器和工業(yè)控制等。傳統(tǒng)設(shè)計方法是應(yīng)用MCU或DSP通過軟件控制數(shù)據(jù)采集的A/D轉(zhuǎn)換,這樣必將頻繁中斷系統(tǒng)的運行,從而減弱系統(tǒng)的數(shù)據(jù)運算能力,數(shù)據(jù)采集的速度也將受到限制。本文采用DSP+FPGA的方案,由硬件控制A/D轉(zhuǎn)換和數(shù)據(jù)存儲,最大限度地提高系統(tǒng)的信號采集和處理能力。

系統(tǒng)結(jié)構(gòu)

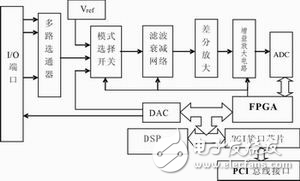

整個采集卡包括信號調(diào)理、數(shù)據(jù)采集、數(shù)據(jù)處理和總線接口設(shè)計。系統(tǒng)結(jié)構(gòu)如圖1所示。

圖1 系統(tǒng)結(jié)構(gòu)框圖

本文設(shè)計了具有信號衰減、增益放大和濾波等功能的信號調(diào)理電路,采用16位精度、最高采樣率為500KSPS的A/D轉(zhuǎn)換器AD7676;數(shù)字系統(tǒng)設(shè)計利用FPGA極其靈活、可編程的特點,選用Altera公司FPGA芯片EP2C8Q208,完成精度校正和邏輯時序控制;DSP采用TI公司的TMS320VC5416,使A/D轉(zhuǎn)換后的數(shù)據(jù)在傳輸?shù)?a target='_blank' class='arckwlink_none'>上位機之前,進行數(shù)據(jù)整理、標記、打包以及數(shù)據(jù)預處理。數(shù)據(jù)采集卡可同時進行8通道數(shù)據(jù)采集,通道可進行衰減倍數(shù)、采樣速度以及放大增益設(shè)置。同時提供模擬輸出通道,用于實現(xiàn)波形產(chǎn)生和模擬驅(qū)動功能。能夠進行自動校準,保證數(shù)據(jù)采集的準確性。PCI總線接口電路采用PLX Technology公司的PCI總線接口芯片PCI9030,完成數(shù)據(jù)采集和狀態(tài)、控制信號的傳輸。

系統(tǒng)硬件電路設(shè)計

數(shù)據(jù)采集模塊設(shè)計

從傳感器送來的8路模擬輸入信號通過多路模擬開關(guān)ADG507選擇進入模擬通道,如果多通道同時采集,則采用時分復用方式,由FPGA依次控制各通道的通斷。模式選擇開關(guān)ADG509為四選一模擬開關(guān),可分別選擇被測模擬信號、標準參考電壓值或用于通道校準的、經(jīng)過DAC轉(zhuǎn)換后的信號進入后級濾波衰減網(wǎng)絡(luò)電路。送入ADC的信號要先經(jīng)過低通濾波,以濾除高頻噪聲。濾波電路設(shè)計為二階阻容低通濾波器,對頻率高于50KHz的信號濾波。衰減電路設(shè)計為有源衰減,選用Linear公司的差分放大器LTC1992,可完成輸入信號極性轉(zhuǎn)換,實現(xiàn)單端信號轉(zhuǎn)差分信號,同時通過由FPGA控制繼電器選通不同的電阻網(wǎng)絡(luò)調(diào)整衰減倍數(shù),可實現(xiàn)對不同電壓輸入范圍信號的調(diào)整,以滿足AD7676的輸入電壓范圍。信號增益可編程放大器LTC6911可通過編程設(shè)置以1、2、5步進變化的1 V/V“100 V/V增益倍數(shù) ,數(shù)據(jù)采集過程中通過FPGA內(nèi)部的比較電路自動調(diào)整增益放大器增益倍數(shù),極大提高了對微弱信號的分辨能力。AD7676為差分信號輸入, MAX6325基準源提供基準為2.5V的參考電壓,采樣時鐘由晶振提供10MHz時鐘信號經(jīng)FPGA內(nèi)部分頻電路得到,單通道最高采樣率為500KSPS。

FPGA電路設(shè)計

FPGA芯片也是一種特殊的ASIC芯片,屬于可編程邏輯器件,它是在PAL、GAL等邏輯器件的基礎(chǔ)上發(fā)展起來的。同以往的PAL、GAL等相比,F(xiàn)PGA規(guī)模比較大,適合于時序、組合等邏輯電路應(yīng)用。本文選用Altera公司的FPGA芯片EP2C8Q208,完成數(shù)據(jù)采集卡的時序和地址譯碼電路設(shè)計。由于EP2C8Q208有36個M4K RAM,在FPGA內(nèi)部設(shè)計一個16位寬度、4KB深度的FIFO,使用FIFO提高數(shù)據(jù)采集卡對多通道信號的采集存儲能力。FIFO有半滿、全滿、空標志位,當DSP檢測到半滿標志位時,F(xiàn)IFO同時讀寫;全滿時只讀不寫;空時只寫不讀。A/D采樣控制信號由DSP通過FPGA控制;DSP對采集后的數(shù)據(jù)進行進一步處理,以提高精度,也具有傳統(tǒng)CPU或MCU的功能,對時序、觸發(fā)、DMA中斷請求作出相應(yīng)處理。

DSP電路設(shè)計

DSP采用 TMS320VC5416,它是16位定點DSP,具有高度的操作靈活性和很高的運行速度,采用改善的哈佛結(jié)構(gòu)(1組程序存儲器總線,3組數(shù)據(jù)存儲器總線,4組地址總線),具有專用硬件邏輯的CPU、片內(nèi)128KB的存儲器、片內(nèi)外設(shè),以及一個效率很高的指令集。

DSP 在系統(tǒng)中的作用主要是將A/D轉(zhuǎn)換后的數(shù)據(jù)在傳輸?shù)缴衔粰C之前,進行數(shù)據(jù)整理、標記、打包以及數(shù)據(jù)預處理。數(shù)據(jù)采集系統(tǒng)所有控制信號都由DSP控制FPGA邏輯電路產(chǎn)生。DSP外掛Flash存放DSP程序及其它配置數(shù)據(jù),在上電時,DSP采用并行方式調(diào)入DSP內(nèi)部執(zhí)行。

校準電路設(shè)計

校準電路是本設(shè)計的重要環(huán)節(jié),數(shù)據(jù)采集卡的高精度性能不僅取決于高分辨率的ADC,在更大程度上要依靠該數(shù)據(jù)采集卡優(yōu)良的自校準和抗噪聲能力來實現(xiàn)。

校準時,DSP發(fā)出標準值,經(jīng)D/A和A/D轉(zhuǎn)換后,所采集的數(shù)據(jù)值與原標準值相比較,取其偏差系數(shù)組成去噪方程,以實現(xiàn)數(shù)據(jù)采集卡的自校準。

PCI總線接口電路設(shè)計

PCI總線規(guī)范十分復雜,其接口的實現(xiàn)比較困難。數(shù)據(jù)采集卡采用PCI9030作為用戶接口,為PCI總線接口的開發(fā)提供了一種簡捷的方法,只需設(shè)計簡單的局部總線接口控制電路即可實現(xiàn)PCI總線的高速數(shù)據(jù)傳輸。使用Altera 公司的Quartus II,使得硬件實現(xiàn)軟件化設(shè)計,更新了傳統(tǒng)的電路設(shè)計和調(diào)試方式,大大縮短了開發(fā)周期,特別是其設(shè)計仿真和定時分析使得設(shè)計更加可靠,確保了系統(tǒng)的正確性。

系統(tǒng)軟件設(shè)計

驅(qū)動程序設(shè)計

在Windows98/ 2000/ XP 環(huán)境下,處于Windows 用戶態(tài)的應(yīng)用程序不能直接對硬件設(shè)備進行操作,要實現(xiàn)對數(shù)據(jù)采集卡的硬件資源(如內(nèi)存、中斷等)的訪問,必須編寫運行在核心態(tài)的設(shè)備驅(qū)動程序。目前,使用較多的開發(fā)工具是GUNGO公司的驅(qū)動程序開發(fā)組件WinDriver。利用WinDriver開發(fā)驅(qū)動程序,不需熟悉操作系統(tǒng)的內(nèi)核知識。整個驅(qū)動程序中的所有函數(shù)都是工作在用戶態(tài)的,通過與WinDriver的.VXD和.SYS文件交互來達到驅(qū)動硬件的目的。因為 WinDriver 開發(fā)環(huán)境提供了針對 PLX 公司芯片的存儲器范圍、寄存器和中斷處理等模塊,所以本文采用了GUNGO公司的 WinDriver5.3開發(fā)工具,它支持PLX公司的PCI接口芯片,用戶無需具有DDK和核心態(tài)程序開發(fā)經(jīng)驗,調(diào)試時可結(jié)合 PLX 公司的 PLXmon 工具。

系統(tǒng)結(jié)構(gòu)

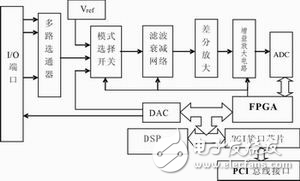

整個采集卡包括信號調(diào)理、數(shù)據(jù)采集、數(shù)據(jù)處理和總線接口設(shè)計。系統(tǒng)結(jié)構(gòu)如圖1所示。

圖1 系統(tǒng)結(jié)構(gòu)框圖

本文設(shè)計了具有信號衰減、增益放大和濾波等功能的信號調(diào)理電路,采用16位精度、最高采樣率為500KSPS的A/D轉(zhuǎn)換器AD7676;數(shù)字系統(tǒng)設(shè)計利用FPGA極其靈活、可編程的特點,選用Altera公司FPGA芯片EP2C8Q208,完成精度校正和邏輯時序控制;DSP采用TI公司的TMS320VC5416,使A/D轉(zhuǎn)換后的數(shù)據(jù)在傳輸?shù)?a target='_blank' class='arckwlink_none'>上位機之前,進行數(shù)據(jù)整理、標記、打包以及數(shù)據(jù)預處理。數(shù)據(jù)采集卡可同時進行8通道數(shù)據(jù)采集,通道可進行衰減倍數(shù)、采樣速度以及放大增益設(shè)置。同時提供模擬輸出通道,用于實現(xiàn)波形產(chǎn)生和模擬驅(qū)動功能。能夠進行自動校準,保證數(shù)據(jù)采集的準確性。PCI總線接口電路采用PLX Technology公司的PCI總線接口芯片PCI9030,完成數(shù)據(jù)采集和狀態(tài)、控制信號的傳輸。

系統(tǒng)硬件電路設(shè)計

數(shù)據(jù)采集模塊設(shè)計

從傳感器送來的8路模擬輸入信號通過多路模擬開關(guān)ADG507選擇進入模擬通道,如果多通道同時采集,則采用時分復用方式,由FPGA依次控制各通道的通斷。模式選擇開關(guān)ADG509為四選一模擬開關(guān),可分別選擇被測模擬信號、標準參考電壓值或用于通道校準的、經(jīng)過DAC轉(zhuǎn)換后的信號進入后級濾波衰減網(wǎng)絡(luò)電路。送入ADC的信號要先經(jīng)過低通濾波,以濾除高頻噪聲。濾波電路設(shè)計為二階阻容低通濾波器,對頻率高于50KHz的信號濾波。衰減電路設(shè)計為有源衰減,選用Linear公司的差分放大器LTC1992,可完成輸入信號極性轉(zhuǎn)換,實現(xiàn)單端信號轉(zhuǎn)差分信號,同時通過由FPGA控制繼電器選通不同的電阻網(wǎng)絡(luò)調(diào)整衰減倍數(shù),可實現(xiàn)對不同電壓輸入范圍信號的調(diào)整,以滿足AD7676的輸入電壓范圍。信號增益可編程放大器LTC6911可通過編程設(shè)置以1、2、5步進變化的1 V/V“100 V/V增益倍數(shù) ,數(shù)據(jù)采集過程中通過FPGA內(nèi)部的比較電路自動調(diào)整增益放大器增益倍數(shù),極大提高了對微弱信號的分辨能力。AD7676為差分信號輸入, MAX6325基準源提供基準為2.5V的參考電壓,采樣時鐘由晶振提供10MHz時鐘信號經(jīng)FPGA內(nèi)部分頻電路得到,單通道最高采樣率為500KSPS。

FPGA電路設(shè)計

FPGA芯片也是一種特殊的ASIC芯片,屬于可編程邏輯器件,它是在PAL、GAL等邏輯器件的基礎(chǔ)上發(fā)展起來的。同以往的PAL、GAL等相比,F(xiàn)PGA規(guī)模比較大,適合于時序、組合等邏輯電路應(yīng)用。本文選用Altera公司的FPGA芯片EP2C8Q208,完成數(shù)據(jù)采集卡的時序和地址譯碼電路設(shè)計。由于EP2C8Q208有36個M4K RAM,在FPGA內(nèi)部設(shè)計一個16位寬度、4KB深度的FIFO,使用FIFO提高數(shù)據(jù)采集卡對多通道信號的采集存儲能力。FIFO有半滿、全滿、空標志位,當DSP檢測到半滿標志位時,F(xiàn)IFO同時讀寫;全滿時只讀不寫;空時只寫不讀。A/D采樣控制信號由DSP通過FPGA控制;DSP對采集后的數(shù)據(jù)進行進一步處理,以提高精度,也具有傳統(tǒng)CPU或MCU的功能,對時序、觸發(fā)、DMA中斷請求作出相應(yīng)處理。

DSP電路設(shè)計

DSP采用 TMS320VC5416,它是16位定點DSP,具有高度的操作靈活性和很高的運行速度,采用改善的哈佛結(jié)構(gòu)(1組程序存儲器總線,3組數(shù)據(jù)存儲器總線,4組地址總線),具有專用硬件邏輯的CPU、片內(nèi)128KB的存儲器、片內(nèi)外設(shè),以及一個效率很高的指令集。

DSP 在系統(tǒng)中的作用主要是將A/D轉(zhuǎn)換后的數(shù)據(jù)在傳輸?shù)缴衔粰C之前,進行數(shù)據(jù)整理、標記、打包以及數(shù)據(jù)預處理。數(shù)據(jù)采集系統(tǒng)所有控制信號都由DSP控制FPGA邏輯電路產(chǎn)生。DSP外掛Flash存放DSP程序及其它配置數(shù)據(jù),在上電時,DSP采用并行方式調(diào)入DSP內(nèi)部執(zhí)行。

校準電路設(shè)計

校準電路是本設(shè)計的重要環(huán)節(jié),數(shù)據(jù)采集卡的高精度性能不僅取決于高分辨率的ADC,在更大程度上要依靠該數(shù)據(jù)采集卡優(yōu)良的自校準和抗噪聲能力來實現(xiàn)。

校準時,DSP發(fā)出標準值,經(jīng)D/A和A/D轉(zhuǎn)換后,所采集的數(shù)據(jù)值與原標準值相比較,取其偏差系數(shù)組成去噪方程,以實現(xiàn)數(shù)據(jù)采集卡的自校準。

PCI總線接口電路設(shè)計

PCI總線規(guī)范十分復雜,其接口的實現(xiàn)比較困難。數(shù)據(jù)采集卡采用PCI9030作為用戶接口,為PCI總線接口的開發(fā)提供了一種簡捷的方法,只需設(shè)計簡單的局部總線接口控制電路即可實現(xiàn)PCI總線的高速數(shù)據(jù)傳輸。使用Altera 公司的Quartus II,使得硬件實現(xiàn)軟件化設(shè)計,更新了傳統(tǒng)的電路設(shè)計和調(diào)試方式,大大縮短了開發(fā)周期,特別是其設(shè)計仿真和定時分析使得設(shè)計更加可靠,確保了系統(tǒng)的正確性。

系統(tǒng)軟件設(shè)計

驅(qū)動程序設(shè)計

在Windows98/ 2000/ XP 環(huán)境下,處于Windows 用戶態(tài)的應(yīng)用程序不能直接對硬件設(shè)備進行操作,要實現(xiàn)對數(shù)據(jù)采集卡的硬件資源(如內(nèi)存、中斷等)的訪問,必須編寫運行在核心態(tài)的設(shè)備驅(qū)動程序。目前,使用較多的開發(fā)工具是GUNGO公司的驅(qū)動程序開發(fā)組件WinDriver。利用WinDriver開發(fā)驅(qū)動程序,不需熟悉操作系統(tǒng)的內(nèi)核知識。整個驅(qū)動程序中的所有函數(shù)都是工作在用戶態(tài)的,通過與WinDriver的.VXD和.SYS文件交互來達到驅(qū)動硬件的目的。因為 WinDriver 開發(fā)環(huán)境提供了針對 PLX 公司芯片的存儲器范圍、寄存器和中斷處理等模塊,所以本文采用了GUNGO公司的 WinDriver5.3開發(fā)工具,它支持PLX公司的PCI接口芯片,用戶無需具有DDK和核心態(tài)程序開發(fā)經(jīng)驗,調(diào)試時可結(jié)合 PLX 公司的 PLXmon 工具。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計

- 基于FPGA+DSP的高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計

- AD522:高精度數(shù)據(jù)采集儀表放大器數(shù)據(jù)表

- 如何使用DSP和FPGA進行高精度數(shù)據(jù)采集卡的設(shè)計資料說明 14次下載

- 如何使用FPGA和DSP進行高精度數(shù)字電源數(shù)據(jù)采集系統(tǒng)設(shè)計的資料概述 20次下載

- 基于DSP和LTC1859的16位高精度數(shù)據(jù)采集系統(tǒng) 2次下載

- 一種高精度數(shù)據(jù)采集無線傳輸系統(tǒng)硬件設(shè)計 16次下載

- 基于FPGA和USB2.0的高精度數(shù)據(jù)采集系統(tǒng)設(shè)計 25次下載

- 基于USB2.0的高速高精度數(shù)據(jù)采集系統(tǒng)模擬電路設(shè)計 25次下載

- DSP+FPGA實現(xiàn)測井數(shù)據(jù)采集系統(tǒng) 71次下載

- ADS1278在高精度數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

- 基于DSP和FPGA的高精度數(shù)據(jù)采集卡設(shè)計

- 一種高精度數(shù)據(jù)采集無線傳輸系統(tǒng)硬件設(shè)計

- 具有PCI和并行接口的數(shù)據(jù)采集系統(tǒng)設(shè)計

- 基于FPGA的高精度數(shù)據(jù)采集濾波系統(tǒng)設(shè)計

- 旋轉(zhuǎn)環(huán)境下基于FPGA的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計 1163次閱讀

- TI ADC幫助實現(xiàn)高精度數(shù)據(jù)采集,同時降低65%的功耗 918次閱讀

- 高精度數(shù)據(jù)采集系統(tǒng)設(shè)計方案 2737次閱讀

- 基于AD4020的高精度數(shù)據(jù)采集系統(tǒng) 2446次閱讀

- 基于高精度數(shù)據(jù)采集板在LabVIEW平臺實現(xiàn)VTE-MED海水淡化系統(tǒng)的設(shè)計 1131次閱讀

- 24通道數(shù)據(jù)采集模塊設(shè)計及FPGA實現(xiàn)技術(shù)分析 2485次閱讀

- 一種基于ARM+FPGA的高精度數(shù)據(jù)采集系統(tǒng)設(shè)計 7569次閱讀

- 利用AD574A設(shè)計基于FPGA的高速數(shù)據(jù)采集系統(tǒng) 8376次閱讀

- 基于FPGA的FIR濾波器數(shù)據(jù)采集系統(tǒng) 3868次閱讀

- 高速高精度的數(shù)據(jù)采集系統(tǒng)的設(shè)計與實現(xiàn) 4570次閱讀

- 基于FPGA的振動信號采集系統(tǒng)設(shè)計及實現(xiàn) 7282次閱讀

- 一種高速圖像數(shù)據(jù)采集板的設(shè)計方案 2195次閱讀

- 高精度18位 5 MSPS 低功耗數(shù)據(jù)采集信號鏈 3527次閱讀

- 基于單片機的高精度海量數(shù)據(jù)采集與存儲系統(tǒng) 3157次閱讀

- 基于SOPC的數(shù)據(jù)采集與處理系統(tǒng)設(shè)計 1481次閱讀

下載排行

本周

- 1DC電源插座圖紙

- 0.67 MB | 2次下載 | 免費

- 2AN158 GD32VW553 Wi-Fi開發(fā)指南

- 1.51MB | 2次下載 | 免費

- 3AN148 GD32VW553射頻硬件開發(fā)指南

- 2.07MB | 1次下載 | 免費

- 4AN111-LTC3219用戶指南

- 84.32KB | 次下載 | 免費

- 5AN153-用于電源系統(tǒng)管理的Linduino

- 1.38MB | 次下載 | 免費

- 6AN-283: Σ-Δ型ADC和DAC[中文版]

- 677.86KB | 次下載 | 免費

- 7SM2018E 支持可控硅調(diào)光線性恒流控制芯片

- 402.24 KB | 次下載 | 免費

- 8AN-1308: 電流檢測放大器共模階躍響應(yīng)

- 545.42KB | 次下載 | 免費

本月

- 1ADI高性能電源管理解決方案

- 2.43 MB | 450次下載 | 免費

- 2免費開源CC3D飛控資料(電路圖&PCB源文件、BOM、

- 5.67 MB | 138次下載 | 1 積分

- 3基于STM32單片機智能手環(huán)心率計步器體溫顯示設(shè)計

- 0.10 MB | 130次下載 | 免費

- 4使用單片機實現(xiàn)七人表決器的程序和仿真資料免費下載

- 2.96 MB | 44次下載 | 免費

- 53314A函數(shù)發(fā)生器維修手冊

- 16.30 MB | 31次下載 | 免費

- 6美的電磁爐維修手冊大全

- 1.56 MB | 24次下載 | 5 積分

- 7如何正確測試電源的紋波

- 0.36 MB | 17次下載 | 免費

- 8感應(yīng)筆電路圖

- 0.06 MB | 10次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935121次下載 | 10 積分

- 2開源硬件-PMP21529.1-4 開關(guān)降壓/升壓雙向直流/直流轉(zhuǎn)換器 PCB layout 設(shè)計

- 1.48MB | 420062次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233088次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費下載

- 340992 | 191367次下載 | 10 積分

- 5十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183335次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81581次下載 | 10 積分

- 7Keil工具MDK-Arm免費下載

- 0.02 MB | 73810次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65988次下載 | 10 積分

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論