LTC1594L,4/8通道,3V微功耗采樣,12位串行I / O A / D轉(zhuǎn)換器的典型應(yīng)用。它們通常在轉(zhuǎn)換時僅消耗160uA的電源電流,并在轉(zhuǎn)換之間自動關(guān)斷至1nA的典型電源電流

2020-06-16 16:47:35

本帖最后由 eehome 于 2013-1-5 10:11 編輯

24C02串行E2PROM的讀寫

2012-08-10 14:07:14

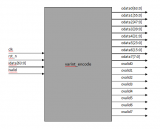

LTC1598L的典型應(yīng)用 -4通道和8通道,3V微功耗采樣12位串行I / O A / D轉(zhuǎn)換器

2019-06-10 09:31:59

什么是串行通信?80C51串行口的工作方式有哪幾種?串口如何使用?

2021-10-21 09:03:06

80C51串行口的結(jié)構(gòu)有兩個物理上獨立的接收,發(fā)送緩沖器SBUF,他們占用同一地址,99H,接收器是雙緩沖結(jié)構(gòu)發(fā)送緩沖器,因為發(fā)送是CPU是主動的,不會產(chǎn)生重疊錯誤。串口的控制寄存器

2021-12-08 06:34:02

串行接口常用于芯片至芯片和電路板至電路板之間的數(shù)據(jù)傳輸。隨著系統(tǒng)帶寬不斷增加至多吉比特范圍,并行接口已經(jīng)被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2019-10-23 07:16:35

各位大神是否能用400個以上I/O口的FPGA芯片,實現(xiàn)串并轉(zhuǎn)換,一個串行RS232輸入,將輸入的50個字節(jié)的數(shù)據(jù)轉(zhuǎn)換控制 50個8位并行輸出。具體大概應(yīng)該怎么做

2015-07-08 17:19:33

1、FPGA內(nèi)部AD多通道采樣實驗設(shè)計與實現(xiàn)編寫程序,使用Anlogic 自帶的ADC進行四通道數(shù)據(jù)輪詢采集,同時介紹TD軟件IP核的用法。本實驗設(shè)計使用FPGA自帶的12位串行AD芯片工作,將直流

2022-07-15 18:18:37

,數(shù)據(jù)的緩沖區(qū)可以開得很大,對于數(shù)量比較小的設(shè)計可以采用寄存器完成串并轉(zhuǎn)換。如無特殊需求,應(yīng)該用同步時序設(shè)計完成串并之間的轉(zhuǎn)換。比如數(shù)據(jù)從串行到 并行,數(shù)據(jù)排列順序是高位在前,可以用下面的編碼實現(xiàn):prl_temp

2012-02-10 11:40:52

各位學(xué)者好,我一直不懂串行和并行通信的應(yīng)用,以及傳輸時間和頻率的問題例如我要用15MHz采樣頻率的外部AD采集正弦模擬信號,選的AD芯片采用8位串行通信,那么我聽說串行通信時要占用DSP的頻率為15M×8=120MHz這個是為什么?希望解釋一下,如果能形象地講解串并聯(lián)通信就更好了,謝謝各位學(xué)者!

2016-07-15 11:40:58

作者:Michael Peffers 歡迎閱讀《獲得連接》系列博客!在上篇《獲得連接》博客《解密串行解串器》一文中,我們探討了如何通過串行解串器器件實現(xiàn)并行數(shù)據(jù)的串行解串。本文我們將探討串行解串器

2018-09-13 10:01:00

AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-13 09:57:27

AT24C02串行E2PROM的工作原理與讀寫

2012-07-31 21:47:47

AT25128A是ATMELCorporation公司生產(chǎn)的一款144位串行電可擦除可編程只讀存儲器。它提供131,072/262,144位串行電可擦出可編程的只讀存儲器(EEPROM),換算成

2021-04-23 08:03:09

AT89C51串行口工作方式是什么?AT89C51單片機在無線數(shù)據(jù)傳輸中的應(yīng)用是什么?

2021-06-07 06:21:32

GM8827C 實現(xiàn)27位RGB信號和3位控制信號 HS、VS、DE 的并串轉(zhuǎn)化功能24 位 LVDS 發(fā)送器1 、產(chǎn)品概述本產(chǎn)品為一款多通道 LVDS 串行發(fā)送器,實現(xiàn)將 27 位 CMOS

2022-01-25 06:02:31

LTC1598的典型應(yīng)用 -8通道,微功耗采樣12位串行I / O A / D轉(zhuǎn)換器

2020-06-16 14:19:18

M95256串行(SPI)EEPROM數(shù)據(jù)存取驅(qū)動仿真1、M95256介紹M95256 器件是組織為 32768 x 8 位的電可擦除可編程存儲器 (EEPROM),可通過 SPI 總線訪問

2022-02-15 06:45:40

10bits 并串/串并轉(zhuǎn)換芯片,用于 LVDS 差分底板上傳輸和接收 10MHz 至 80MHz 的并行字速率的串行數(shù)據(jù)。加載起始停止位后,轉(zhuǎn)換為一個串行數(shù)據(jù)速率在120Mbps 至 960Mbps 負(fù)載編碼

2021-12-07 09:52:07

1、MSP430串行通信概述串口是系統(tǒng)與外界聯(lián)系的重要手段,在嵌入式系統(tǒng)開發(fā)和應(yīng)用中,經(jīng)常需要使用上位機實現(xiàn)系統(tǒng)調(diào)試及現(xiàn)場數(shù)據(jù)的采集和控制。一般是通過上位機本身配置的串行口,通過串行通信技術(shù)

2022-02-15 06:52:31

?8位串行發(fā)送器的可選擇時鐘可達(dá)48 MHz,產(chǎn)生最大的6 Mbit數(shù)據(jù)速率 ?數(shù)據(jù)成幀包括起始位、可選奇偶校驗位和停止位?RS-232串行數(shù)據(jù)格式兼容偶校驗、奇校驗或無奇偶校驗 ?在發(fā)送緩沖區(qū)為空時可選擇觸發(fā)中斷

2012-11-20 15:44:18

的邏輯1或邏輯0有多個位沒有變化時,信號的轉(zhuǎn)換就會因為電壓位階的關(guān)系而造成信號錯誤。直流平衡的最大好處便是可以克服以上問題。8B/10B編碼是目前許多高速串行總線采用的一種編碼機制,如1394b

2018-12-11 11:04:22

STM32407外接AD76026串行模式,有無大佬有參考代碼參考一下啊

2021-01-08 16:33:15

處理器與外部設(shè)備通信的兩種方式:并行通信傳輸原理:數(shù)據(jù)各個位同時傳輸。優(yōu)點:速度快缺點:占用引腳資源多串行通信傳輸原理:數(shù)據(jù)按位順序傳輸。優(yōu)點:占用引腳資源少缺點:速度相對較慢串行通信:按照

2022-01-14 06:36:55

在我們使用STM32串行通訊時,可能用到多個USART串口,而此時printf只能向一個串口打印,見上篇,此時我們需要按照如下編輯個新的函數(shù),實現(xiàn)向其它串口打印數(shù)據(jù)。1.添加文件2.函數(shù)定義及編輯 按照上述操作編輯相應(yīng)函數(shù)之后,再進行正常的USART串口配置,即可進行正常的串行通訊串口發(fā)送。...

2022-02-23 06:56:59

TLC2543串行A/D轉(zhuǎn)換程序即pretous仿真電壓表測量

2012-11-27 20:16:59

TLC2543串行模數(shù)轉(zhuǎn)換器參數(shù)資料下載內(nèi)容主要介紹了:TLC2543外觀圖TLC2543特點TLC2543引腳功能TLC2543內(nèi)部方框圖

2021-05-21 07:44:43

這是TLC549串行模數(shù)轉(zhuǎn)換程序:CSBITP1.7DATBITP1.6CLKBITP3.0AD_DATADATA30HORG0000HAJMPMAINORG0100HMAIN:MOVSP

2015-01-04 14:26:15

W25Q64串行FLASH基礎(chǔ)知識大小:8M(Byte)(128塊(Block),每塊64K字節(jié),每塊16個扇區(qū)(Sector),每個扇區(qū)4K字 節(jié),每個扇區(qū)16頁,每頁256個字節(jié))特點

2021-07-22 09:32:51

模式。XCF08P版本包括32兆位,16 - Mbit的,和8兆位串行PROM,支持主,從串行SelectMAP和SelectMAP FPGA配置模式。

2010-04-07 13:37:44

`《微機原理與匯編語言》89C51串行口及串行通信技術(shù)[hide][/hide]`

2017-04-05 12:51:12

本帖最后由 eehome 于 2013-1-5 09:44 編輯

串行接口(RS-232) 連接到PC與FPGA的串信接口是一種簡單的連接方式。本節(jié)課程將向大家展示了如何在一個FPGA上創(chuàng)建

2012-03-20 14:05:46

長等優(yōu)點,本文將著熏介紹串口通信的連接方式以及利用C語言編程實現(xiàn)串口通訊,最后以實際的工程項目應(yīng)用,驗證了該通訊方式的可靠性。 1 RS232串行接口 1.1 RS232接口簡介 RS232串行

2019-06-17 05:00:08

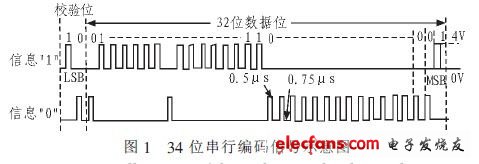

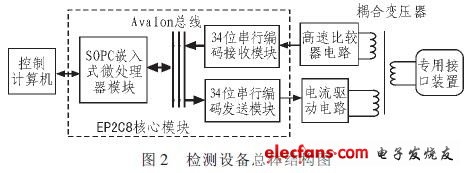

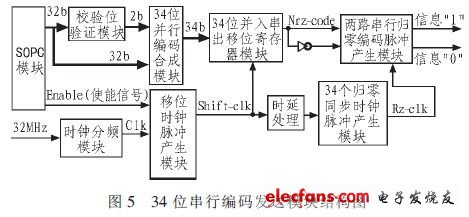

、RS485以及ARINC429等都是電子設(shè)備中常用的串行數(shù)據(jù)傳輸標(biāo)準(zhǔn)。某專用接口裝置采用一種點對點的34位串行編碼數(shù)據(jù)傳輸標(biāo)準(zhǔn),34位串行編碼經(jīng)耦合變壓器調(diào)制后進行信息傳輸,能夠在惡劣的電磁環(huán)境下

2019-09-20 07:52:56

模數(shù)轉(zhuǎn)換原理是什么?它的過程是怎樣的?八位串行A/D轉(zhuǎn)換器ADC0832具有什么特點?工作原理是什么?

2021-09-29 06:50:05

關(guān)于MAX9247/MAX9218串行器/解串器芯片組的性能測試詳細(xì)解析

2021-04-12 06:11:46

給TLC2355寫一個驅(qū)動,由EPM570控制它采樣,TLC2355為14位串行AD,采樣率達(dá)3.5M(串行時鐘可達(dá)63M,63M/18=3.5M),其實只要弄懂這個串行AD的操作時序,寫起代碼

2011-09-02 14:00:52

現(xiàn)有一串行信號,需延時2ms,用芯片如何實現(xiàn),不用單片機。

2015-04-27 20:35:39

四通道12位串行輸入數(shù)據(jù)轉(zhuǎn)換器AD5735資料下載內(nèi)容包括:AD5735引腳功能AD5735內(nèi)部方框圖

2021-03-30 07:37:08

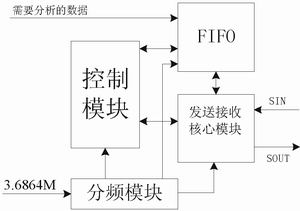

數(shù)據(jù),并發(fā)送給從機;(2) 接收來自從機的串行數(shù)據(jù),將其轉(zhuǎn)換為并行數(shù)據(jù),通過并行端口輸出;(3) 輸出從機所需要的輸入信號、時鐘信號SCK 和片選信號CS。在數(shù)據(jù)串并轉(zhuǎn)換的過程中, 必須用到寄存器來存放臨時

2015-01-28 14:09:51

基于Keil C的AT24C02串行E2PROM的編程AT24C02是美國Atmel公司的低功耗CMOS型E2PROM,內(nèi)含256×8位存儲空間,具有工作電壓寬(2.5~5.5

2009-08-18 17:13:25

存儲器中讀取16字節(jié)數(shù)據(jù),經(jīng)并串轉(zhuǎn)換輸出16路的串行數(shù)據(jù)。從波形圖分析,功能正確,且各輸出端口信號均符合時序要求。 5結(jié)語 FPGA是在線可編程芯片,可以根據(jù)不同的用戶要求進行不同的編程,縮短

2011-08-19 08:48:06

本帖最后由 tcvsdonnnie 于 2013-7-8 20:04 編輯

cc1101無線收發(fā)程序,已調(diào)試成功了,其中,發(fā)送端采用的是g2553的launchpad,接收端是采用的是f149控制的,且用了12864串行顯示,

2013-07-03 21:37:00

如何去實現(xiàn)FPGA中的各個模塊?如何去實現(xiàn)FPGA與PC的串行通信?

2021-05-26 07:25:13

請問一下有沒有采用EEPROM對大容量FPGA芯片數(shù)據(jù)實現(xiàn)串行加載的實際方案?

2021-04-08 06:01:39

LTC1096的典型應(yīng)用 - 微功耗采樣8位串行I / O A / D轉(zhuǎn)換器

2019-06-03 08:49:16

本文介紹的基于可編程門陣列( FPGA) 實現(xiàn)的沖擊信號處理芯片,能在飛行器飛行過程中,實時完成對三路沖擊信號的分析和處理,將沖擊信號的處理結(jié)果代替沖擊波的原始測量數(shù)據(jù)傳到地面,利用沖擊信號

2021-05-26 06:28:43

,因為一切都不能隨機出現(xiàn),必須在給定的時間內(nèi)發(fā)生。系統(tǒng)時鐘可分配給包括串行解串器在內(nèi)的所有組件,以幫助實現(xiàn)同步工作。網(wǎng)絡(luò)處理單元 (NPU) 或 FPGA 等終端器件不僅可在所需的系統(tǒng)頻率下實現(xiàn)并行

2018-09-13 09:54:18

無限采樣保持使用與LTC1658串行14位DAC接口的LTC1417串行14位ADC

2020-04-02 10:00:45

您好Xilinx社區(qū),我喜歡在時鐘ADC和FPGA Spartan 6的通用時鐘之間以90°的方式提供相位信號。之前,我的信號使用not功能進行180°定相。我的時鐘信號只編碼一位。請問你能幫幫我

2019-03-06 12:13:51

最新51串行編程器的全部制作資料及軟件

2012-08-06 22:25:19

如何用EEPROM對大容量FPGA芯片數(shù)據(jù)實現(xiàn)串行加載?如何設(shè)計并-串轉(zhuǎn)換時序?

2021-04-29 07:13:12

有誰寫過AD9851串行傳送的程序嗎?

2013-08-02 22:35:46

求大佬分享一種RS-232串行通信消除干擾噪聲的設(shè)計方法

2021-06-02 07:13:35

GM7122是由成都國騰電子技術(shù)提供的一款視頻編碼芯片,視頻編碼電路主要實現(xiàn)接收 8 位 CCIR656 格式的 YUV 數(shù)據(jù),(例如 MPEG 解碼數(shù)據(jù)),并編碼成 CVBS 信號,經(jīng)過 D/A

2021-07-05 15:24:14

GM7122是由成都國騰電子技術(shù)提供的一款視頻編碼芯片,視頻編碼電路主要實現(xiàn)接收 8 位 CCIR656 格式的 YUV 數(shù)據(jù),(例如 MPEG 解碼數(shù)據(jù)),并編碼成 CVBS 信號,經(jīng)過 D/A

2022-04-26 10:45:25

GM7122是由成都國騰電子技術(shù)提供的一款視頻編碼芯片,視頻編碼電路主要實現(xiàn)接收 8 位 CCIR656 格式的 YUV 數(shù)據(jù),(例如 MPEG 解碼數(shù)據(jù)),并編碼成 CVBS 信號,經(jīng)過 D/A

2022-10-13 18:52:41

請問AD2S1210串行通訊的最大波特率是多少?

2018-09-10 10:34:13

請問AD2S1210串行通訊的最大波特率是多少?

2023-12-18 08:10:54

IJF編碼是什么原理?如何實現(xiàn)IJF編碼?采用FPGA和集成器件來實現(xiàn)IJF編碼

2021-04-13 06:56:04

怎樣去設(shè)計一種RS485串行通信接口電路?RS485串行通信接口電路的應(yīng)用有哪些?

2021-06-02 06:35:15

誰介紹一款FPGA出串行高速2711串行接口芯片

2015-05-25 10:41:52

,不宜實現(xiàn)小型化。增量式光電編碼器不具有計數(shù)和接口電路,一般輸出A、B、Z脈沖信號,價格較低,在實際工程中比較常用。文中設(shè)計了一個基于FPGA的簡單且精度高的接口電路,其結(jié)構(gòu)簡單、性能可靠。具有濾波

2019-06-10 05:00:08

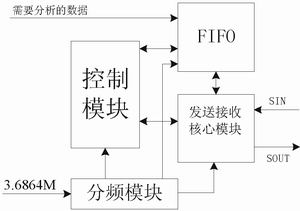

為了使計算機能夠通過串口控制FPGA 的輸出信號,筆者根據(jù)異步串行通信的原理,設(shè)計了簡便易行的FPGA 串行通信接口系統(tǒng),并應(yīng)用VHDL 語言在FPGA 內(nèi)部集成了串行接收模塊,具有較強

2009-09-24 15:52:56 18

18 基于單片機的CPLD/FPGA被動串行下載配置的實現(xiàn):介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現(xiàn)CPLD/FPGA器件的被動串行模式的下載配置,闡述了其原理及軟硬件設(shè)計。 &nb

2009-10-29 21:57:22 19

19 AD7849是一款14/16位串行輸入乘法DAC。該DAC架構(gòu)可確保擁有出色的微分線性性能;在額定溫度范圍內(nèi),A級產(chǎn)品可保證14位單調(diào)性,所有其它等級產(chǎn)品可保證16位單調(diào)性。在上電與關(guān)斷期間(當(dāng)電源

2023-03-06 14:05:11

基于FPGA的各種雷達(dá)信號產(chǎn)生方法,介紹了在FPGA中實現(xiàn)直接數(shù)字頻率合成器(DDS)以及提高輸出信號質(zhì)量的方法,編程實現(xiàn)了頻率捷變、線性調(diào)頻以及相位編碼等雷達(dá)信號的產(chǎn)生。仿真

2010-11-29 18:02:49 31

31 摘 要:本文主要介紹了基于FPGA技術(shù)實現(xiàn)與PC串行通信的過程,給出了各個模塊的具體實現(xiàn)方法,分析了實現(xiàn)結(jié)果,驗證了串行通信的正確性。引言串行通信即

2006-03-24 13:31:51 4661

4661

摘要: 在簡單介紹算術(shù)編碼和自適應(yīng)算術(shù)編碼的基礎(chǔ)上,介紹了利用FPGA器件并通過VHDL語言描述實現(xiàn)自適應(yīng)算術(shù)編碼的過程。整個編碼系統(tǒng)在LTERA公司的MAX+plus Ⅱ軟

2009-06-20 13:40:24 1026

1026

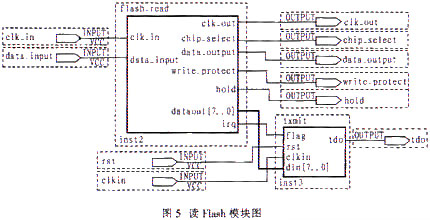

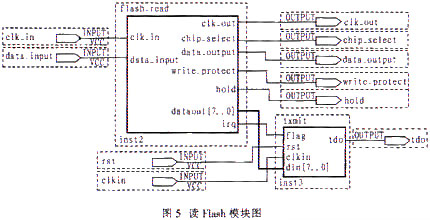

基于FPGA的串行Flash擴展實現(xiàn)

FPGA憑借其方便靈活、可重復(fù)編程等優(yōu)點而日益被廣泛應(yīng)用;閃速存儲器(Flash Memory)以其集成度高、成本低、使用方便等優(yōu)點,在眾多領(lǐng)域中

2010-01-12 10:39:55 1363

1363

研究了能夠同時對多路 光電編碼器 脈沖信號進行細(xì)分、計數(shù)以及傳輸?shù)臄?shù)據(jù)采集處理系統(tǒng)。提出了以高度集成的FPGA芯片為核心的設(shè)計方式,實現(xiàn)6路光電編碼器信號的同步實時處理。坐

2011-08-18 16:33:15 90

90 本文提出了一種用FPGA實現(xiàn)糾錯編碼的設(shè)計思想,并以Altera MAX+PluslI為硬件開發(fā)平臺。利用FPGA編程的特點,用軟件編程方法,很好的解決了糾錯編碼中存在的碼速變換和實時性問題,實現(xiàn)

2011-11-10 17:10:59 61

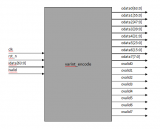

61 為實現(xiàn)某專用接口裝置的接口功能檢測,文中詳細(xì)地介紹了一種34位串行碼的編碼方式,并基于FPGA芯片設(shè)計了該類型編碼的接收、發(fā)送電路。重點分析了電路各模塊的設(shè)計思路。電路采

2012-06-18 12:37:09 41

41 800Mbps準(zhǔn)循環(huán)LDPC碼編碼器的FPGA實現(xiàn)

2016-05-09 10:59:26 37

37 本文介紹了基于DSP和FPGA的編碼器信號測量及處理的通用模塊,對海德漢編碼器進行了概述等。

2017-10-13 18:17:29 19

19 介紹了單片機與FPGA 異步串行通信的實現(xiàn)方法,給出了系統(tǒng)結(jié)構(gòu)原理框圖及其部分VHDL 程序,并定義了發(fā)送器和接收器的端口信號。

2020-09-29 16:20:00 8

8 介紹了單片機與FPGA 異步串行通信的實現(xiàn)方法,給出了系統(tǒng)結(jié)構(gòu)原理框圖及其部分VHDL 程序,并定義了發(fā)送器和接收器的端口信號。

2021-03-02 13:52:00 15

15 串行信號接收芯片AU5561可以解碼Ts5647、Ts5648、Ts5667、Ts5668、Ts5669等型號的編碼器,可以提供40到iiO位串并信號的轉(zhuǎn)換,并且可以和1s/32位CPU或DsP總線

2021-03-29 10:15:55 7

7 今天是畫師第二次和各位大俠見面,執(zhí)筆繪畫FPGA江湖,本人最近項目經(jīng)驗,寫了篇基于FPGA的Varint編碼(壓縮算法)實現(xiàn),這里分享給大家,僅供參考。如有轉(zhuǎn)載,請在文章底部留言,請勿隨意轉(zhuǎn)載,否則

2021-04-02 16:29:16 1580

1580

傳輸系統(tǒng)的組成結(jié)構(gòu)如圖1所示,主要由兩塊ATCA板和一塊ATCA機箱背板組成。兩塊ATCA板上各放置一片FPGA作為串行鏈路的兩個端點,兩片 FPGA之間用兩對差分線進行連接,形成

2021-05-05 16:49:00 4740

4740

現(xiàn)場可編程邏輯陣列(FPGA)資源豐富,結(jié)構(gòu)靈活,近年來發(fā)展迅猛。針對其特點,本文設(shè)計了基于FPGA的增量式光電編碼器的接口電路,實現(xiàn)了對增量式編碼器脈沖信號的倍頻、鑒相及計數(shù)等功能。

2021-04-27 13:57:50 3886

3886

電子發(fā)燒友App

電子發(fā)燒友App

評論