138譯碼器的設置目的是為了實現IO復用,單片機上IO資源緊張,掛載的外設較多,為了解決這一矛盾,引入了138譯碼器單個138譯碼器能夠利用3個IO實現8路選擇(在邏輯上相當于擴展了5個IO),比賽

2022-01-12 07:25:11

看完74hl138譯碼器的技術文檔,就編了這個。很好用的芯片。{:soso_e130:}

2012-08-19 00:54:06

3 -8譯碼器 不知怎么仿真波形弄不出來,主要是輸出引腳的波形有問題,希望大家能給以指導,感謝大家!!!

2014-06-12 21:41:50

74LS138譯碼器是什么?74LS138譯碼器的擴展方法是什么?

2022-01-19 07:14:36

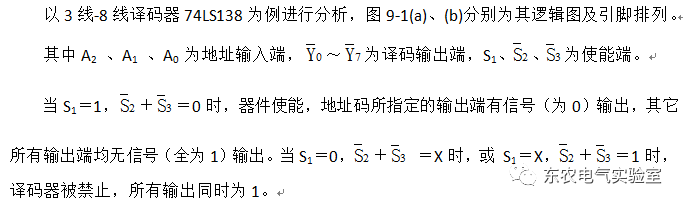

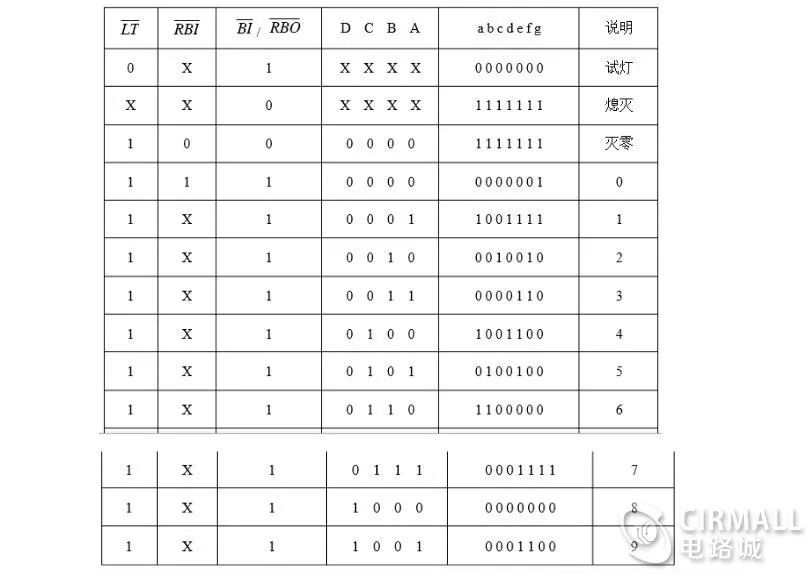

實驗三 7段數碼顯示譯碼器設計(1)實驗目的:學習7段數碼顯示譯碼器的設計;學習VHDL的CASE語句應用。(2)實驗原理:7段數碼顯示譯碼器是純組合電路,通常的小規模專用IC,如74或4000系列

2009-10-11 09:22:08

誰可以用Verilog HDL寫一個關于彩燈控制器的代碼,要求如下:1、設計一個彩燈控制器,使彩燈(LED管)能連續發出四種以上不同的顯示形式;2、隨著彩燈顯示圖案的變化,發出不同的音響聲。教學提示

2016-03-10 17:08:14

本帖最后由 lee_st 于 2017-10-31 08:46 編輯

Verilog HDL代碼書寫規范

2017-10-21 20:53:14

Verilog HDL代碼書寫規范

2017-09-30 08:55:28

:① 邏輯功能正確,②可快速仿真,③ 綜合結果最優(如果是hardware model),④可讀性較好。2. 范圍本規范涉及Verilog HDL編碼風格,編碼中應注意的問題, Testbench的編碼

2017-12-08 14:36:30

輕松成為設計高手Verilog HDL 實用精解 配套源代碼。

2023-10-09 06:28:14

第一次發帖,自己仿真的一個譯碼器,謝謝大家!

2016-03-22 13:34:35

譯碼器及其應用實驗

2017-03-21 13:36:44

那位大大能教一下bcd譯碼器和usp模塊的連接方式,需要什么過度嗎?

2012-07-15 01:06:12

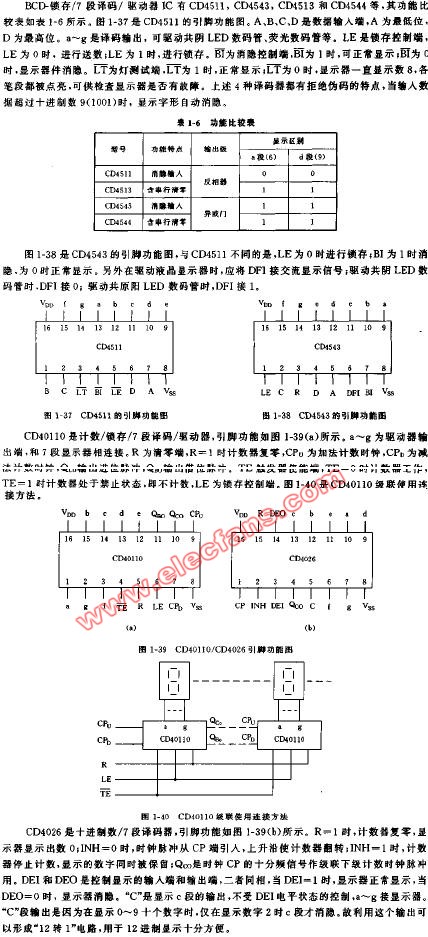

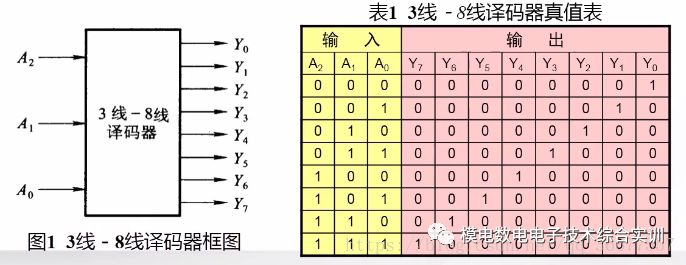

譯碼器1. 譯碼器定義譯碼器是一種用以檢測輸入位(碼)的特定組合是否存在,并以特定的輸出電平來指示這種特定碼的存在的數字電路。——《數字電子技術基礎系統方法》譯碼器的功能是將具有特定含義的二進制碼

2021-12-07 09:37:27

這是譯碼器的一些資料。

2014-07-13 11:59:08

7段數碼管譯碼器設計實驗實驗二 7段數碼管譯碼器設計與實現[實驗目的]熟悉VHDL語言的語法規范了解模塊之間的連接[重點和難點]VHDL語言中port map的使用模塊化設計方法[設備器材

2009-03-14 17:05:15

DCT實現Verilog HDL的數字圖像處理源代碼

2012-08-11 09:30:53

。TTL、CMOS又沒有現成譯碼器可用。故而用二極管搭建此特殊譯碼器,簡單、可靠低成本與現有系統親和度高。我的高一級的產品顯示部分用的是人機界面。

2016-11-17 09:40:39

MATLAB卷積編譯碼源代碼

2012-04-10 20:38:14

verilog HDL建模分三種方式:1、模塊建模2、門級建模3、開關建模這里用38譯碼器感受下1、2的區別:開發平臺:STEP-MXO2-C在官網,我找到了38譯碼器的模塊級建模代碼:module

2017-09-16 21:35:32

芯片,這種數字芯片由簡單的輸入邏輯來控制輸出邏輯,比如 74HC138這個三八譯碼器,圖 3-15 是 74HC138 在我們原理圖上的一個應用。從這個名字來分析,三八譯碼器,就是把 3 種輸入狀態...

2021-07-19 09:08:52

藍橋杯單片機硬件基礎74HC138——三八譯碼器(選通時輸出為低電平)4個或非門控制LED控制LED狀態由P0口控制,選通輸出由Y4C控制;因此,P2口需滿足P2 = 1000 0000

2022-01-21 07:28:20

什么是3-8譯碼器,急啊,速求

2013-03-26 16:52:38

將譯碼器的使能端看做輸入端、譯碼器的輸入端看做地址端,則全譯碼器可作什么使用

2015-05-18 11:41:06

關于138譯碼器位運算簡化代碼的思路分享

2022-02-25 07:43:15

利用開發板上的十六進制7段數碼顯示譯碼器設計一個標準數字時鐘,八個數碼管分別顯示小時、分鐘、秒,顯示格式為24小時進制格式;具備按鍵清零功能。用的是cycloneⅡ代碼有注釋的話最好

2017-06-08 00:08:23

譯碼器有哪些功能?Viterbi譯碼器是由哪幾部分組成的?

2021-05-07 07:28:33

【摘要】:Viterbi譯碼器在通信系統中應用非常普遍,針對采用DSP只能進行相對較低速率的Vit-erbi譯碼的問題,人們開始采用FPGA實現高速率Viterbi譯碼。本文首先簡單描述了

2010-04-26 16:08:39

在DIY的時候,有多元的選擇是最好的。不同品種,不同的廠家,可必免斷供,不同的型號可避免漲價打消制作的想法。在CPU或MCU中譯碼器器至關重要,多位譯碼器可使用74138多片聯級,4位譯碼器可選

2022-10-02 16:40:44

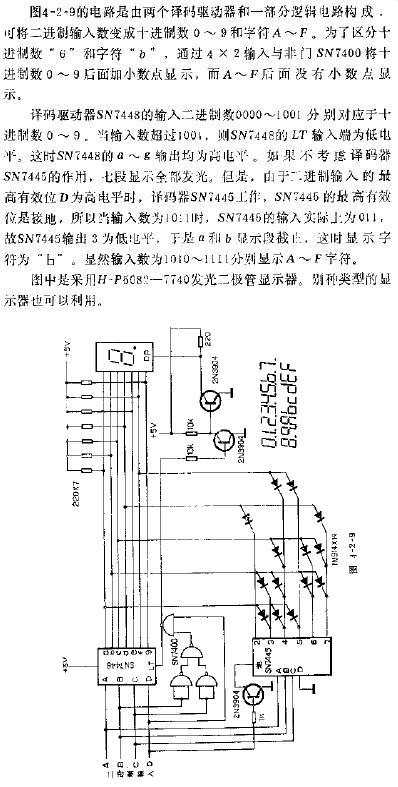

顯示譯碼器是什么?如何準確設計出符合功能要求的顯示譯碼器?

2021-06-01 06:58:12

集成電路編碼器和譯碼器的工作原理即邏輯功能是什么?如何利用邏輯門去實現一種集成電路編碼器呢?如何利用譯碼器進行組合邏輯電路的設計呢?

2021-11-03 06:55:24

本文研究了RS碼的實現方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS編譯碼器的設計,同時對其進行了仿真和在線調試,并給出了功能仿真圖和測試結果。時序仿真結果表明,該編譯碼器能實現預期功能。

2021-06-21 06:23:53

基于FPGA的Turbo碼編譯碼器各模塊實現的 VHDL或verilog HDL程序。急求啊謝謝大神啦!!

2015-06-08 22:45:24

求multisim數碼顯示譯碼器仿真!!!!譯碼器是CC4511。。。。。我的調不太通,希望看看大神做的成品,參考一下!!!!,很急!

2015-12-21 21:13:26

我先寫了一個2-4譯碼器 通過testbench確定2-4譯碼器寫的沒有錯誤 但是將2-4譯碼器連接成3-8譯碼器的時候出現錯誤Error (10663): Verilog HDL Port

2020-08-23 20:36:24

,輸出y=1111_1110;結果y=1111_1110卻跑到a=001的時候去了。。。。。 本人小白,剛學verilog hdl,寫一個3-8譯碼器就出錯了,還望各位大哥大姐多多指教!`

2014-08-10 21:57:17

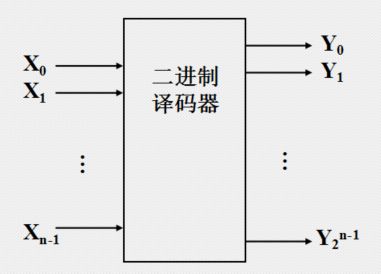

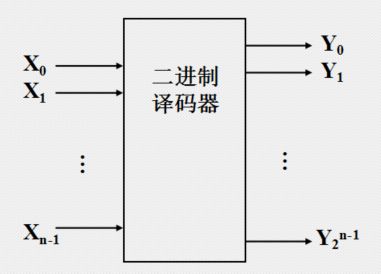

中無記憶元件,也無反饋線。與組合邏輯對應的就是時序邏輯,時序邏輯將在下一講詳細描述。譯碼器(Decoder)是一種多輸入多輸出的組合邏輯電路,負責將二進制代碼翻譯為特定的對象(如邏輯電平等),功能

2016-12-20 18:54:10

出的組合邏輯電路,負責將二進制代碼翻譯為特定的對象(如邏輯電平等),功能與編碼器相反。譯碼器一般分為通用譯碼器和數字顯示譯碼器兩大類。本節設計的是通用譯碼器,數字顯示譯碼器會在后面數碼管章節中涉及。以

2016-12-20 18:45:04

編碼器和譯碼器一、 實驗目的掌握用邏輯門實現編碼器的方法掌握中規模集成電路編碼器和譯碼器的工作原理即邏輯功能掌握 74LS138 用作數據分配器的方法熟悉編碼器和譯碼器的級聯方法能夠利用譯碼器進行

2021-07-30 07:41:16

設計一個虛擬3-8譯碼器,實現138譯碼器的功能

2012-05-15 15:16:39

設計一個虛擬3-8譯碼器,實現138譯碼器的功能!急急急{:soso_e183:}

2012-05-15 15:12:44

?

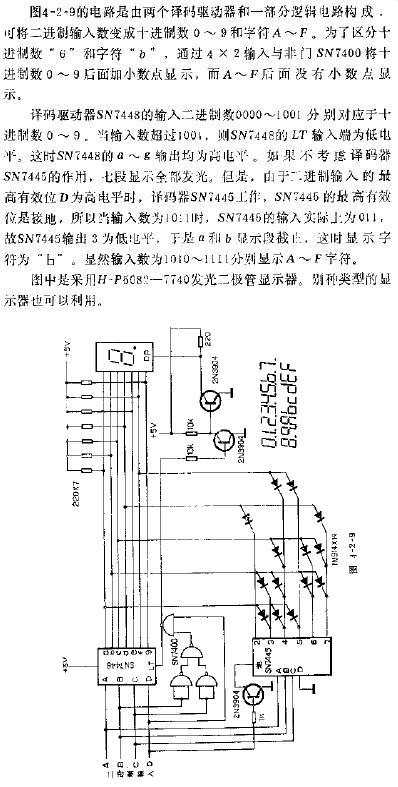

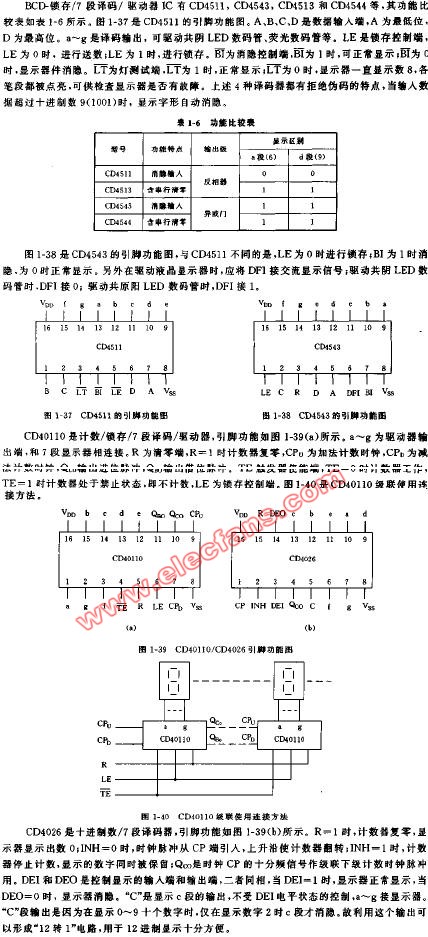

第4章

? 編碼器與譯碼器

2007-12-20 23:14:18 57

57 19.4 譯碼器譯碼器的分類 1. 譯碼器 —輸入為非十進制編碼, 輸出為十進制編碼;2. 編碼器 —輸入為十進制編碼, 輸

2008-09-27 13:04:23 0

0 Verilog-HDL實踐與應用系統設計本書從實用的角度介紹了硬件描述語言Verilog-HDL。通過動手實踐,體驗Verilog-HDL的語法結構、功能等內涵。在前五章,以簡單的實例列舉了Verilog-HDL的用法;

2009-11-14 22:57:40 146

146 譯碼器

譯碼是編碼的逆過程,即將某個二進制翻譯成電路的某種狀態。實現譯碼操作的電路稱為譯碼器。

2008-09-27 12:59:06 12538

12538

數碼譯碼器的應用:譯碼器課件ppt

2008-12-17 14:31:20 1056

1056

顯示譯碼器的應用:

2008-12-17 14:35:06 1260

1260

什么是Verilog HDL?

Verilog HDL是一種硬件描述語言,用于從算法級、門級到開關級的多種抽象設計層次的數字系統建模。被建模的數字系統

2009-01-18 14:53:26 3678

3678

第十七講 譯碼器

6.4.1 二進制譯碼器一、二進制譯碼器 二、譯碼器CT74LS1381.邏輯圖。2.真值表。3.邏輯功能:4.

2009-03-30 16:22:26 7525

7525

十六種字符譯碼器

2009-04-10 10:11:01 633

633

Verilog HDL語言簡介

1.什么是Verilog HDLVerilog HDL是硬件描述語言的一種,用于數

2010-02-09 08:59:33 3609

3609 譯碼器,譯碼器是什么意思

譯碼器是組合邏輯電路的一個重要的器件,其可以分為:變量譯碼和顯示譯碼兩類。 變量譯碼一

2010-03-08 16:32:18 5304

5304 《Verilog HDL 程序設計教程》對Verilog HDL程序設計作了系統全面的介紹,以可綜合的設計為重點,同時對仿真和模擬也作了深入的闡述。《Verilog HDL 程序設計教程》以Verilog-1995標準為基礎

2011-09-22 15:53:36 0

0 譯碼器的功能是將一種數碼變換成另一種數碼。譯碼器的輸出狀態是其輸入變量各種組合的結果。譯碼器的輸出既可以用于驅動或控制系統其他部分。

2011-11-16 14:32:38 6505

6505

本軟件內容為 電子工程師DIY:LED立方 中用到的74譯碼器的相關資料:74譯碼器數據表

2012-06-25 12:00:31 99

99 Verilog_HDL的基本語法詳解(夏宇聞版):Verilog HDL是一種用于數字邏輯電路設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型。Verilog HDL既是一種行為描述的語言也是一種結

2012-10-08 14:48:31 0

0 電子發燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中雙向管腳的功能實現源代碼。 Verilog HDL: Bidirectional Pin This example implements a clocked bidirectional pin in Verilog HDL.

2012-10-15 11:28:26 1525

1525 電子發燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中多路選擇器(MUX)的功能實現源代碼。注意:程序運行在不同軟件平臺可能要作一些修改,請注意閱讀程序

2012-10-15 11:40:32 21789

21789 電子發燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中二進制到BCD碼轉換的功能實現源代碼。注意:程序運行在不同軟件平臺可能要作一些修改,請注意閱讀程序

2012-10-15 11:48:05 6619

6619 電子發燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中二進制到格雷碼轉換的功能實現源代碼。注意:程序運行在不同軟件平臺可能要作一些修改,請注意閱讀程

2012-10-15 11:52:00 3612

3612 介紹了符合CCSDS標準的RS(255,223)碼譯碼器的硬件實現結構。譯碼器采用8位并行時域譯碼算法,主要包括了修正后的無逆BM迭代譯碼算法,錢搜索算法和Forney算法。采用了三級流水線結構實現

2013-01-25 16:43:46 68

68 Verilog HDL程序設計與實踐著重介紹了Verilog HDL語言

2015-10-29 14:45:47 21

21 動態顯示-譯碼器片選實現【C語言】動態顯示-譯碼器片選實現【C語言】動態顯示-譯碼器片選實現【C語言】動態顯示-譯碼器片選實現【C語言】

2015-12-29 15:51:36 0

0 8乘8乘法器verilog源代碼,有需要的下來看看

2016-05-23 18:21:16 24

24 cpu16_verilog源代碼分享,下來看看。

2016-05-24 09:45:40 26

26 本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL設計方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡單的設計代碼并能夠進行一些簡單設計的Verilog HDL建模。

2016-07-15 15:27:00 0

0 譯碼器及其應用實驗

2016-12-29 19:01:45 0

0 38譯碼器控制LED燈每次亮一個

2017-04-21 10:52:38 16

16 (;A平臺,利用Xilinx lSE軟件和Verilog硬件描述語言,對譯碼器中各個子模塊進行了設計和仿真。整個譯碼器設計過程采用流水線處理方式。時序仿真結果表明在保證錯誤符號不大于8個的情況下,經過295個固有延遲之后,每個時鐘周期均可連續輸出經校正的碼字,該RS譯碼器的糾錯能

2017-11-07 15:27:06 15

15 40 nm工藝,通過使用Synopsys Design Compiler對RTL代碼進行邏輯綜合,該譯碼器在時鐘頻率為166 MHz情況下,最終得到面積為0.2 mrTi2,功耗為18 mW,吞吐量達到82 Mbps。

2017-11-11 17:56:15 6

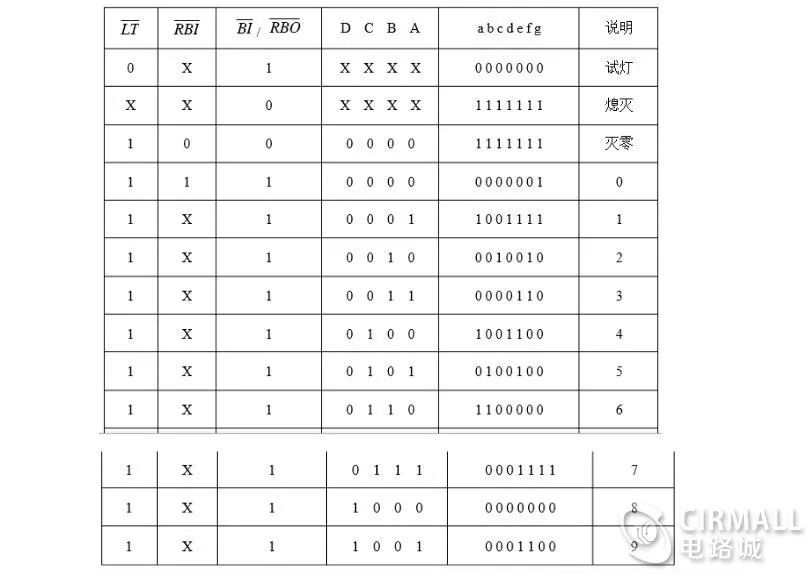

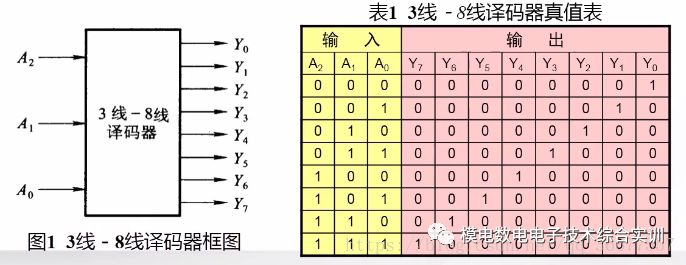

6 通過正確配置譯碼器的使能輸入端,可以將譯碼器的位數進行擴展。例如,實驗室現在只有3線- 8線譯碼器(如74138),要求我{ ]實現一個4線-16線的譯碼器。該如何設計呢?圖1是其中的一種解決方案

2017-11-23 08:44:53 33058

33058

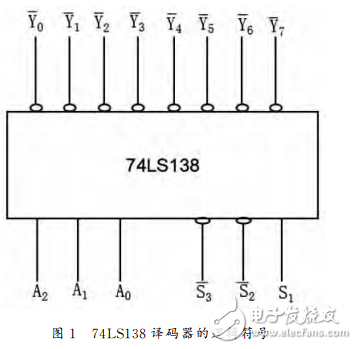

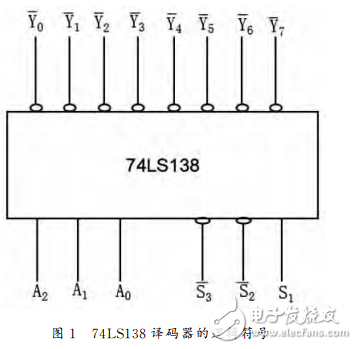

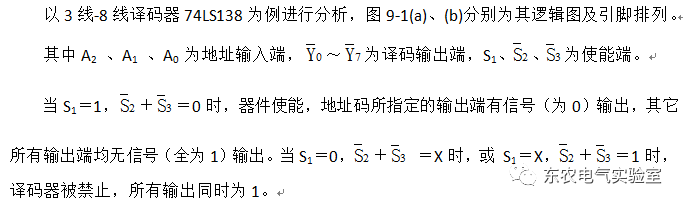

74LS138是帶有擴展功能的集成3線—8線譯碼器,它有3個使能控制端,3個代碼輸入端,8個信號輸出端.控制端用來控制譯碼器的工作狀態,如果僅為了控制譯碼器,一個使能端就夠了,該器件之所以設置三個使能端,除了控制譯碼器的工作外,還可以更靈活、更有效地擴大譯碼器的使用范圍.

2017-12-04 16:08:10 80211

80211

本文首先介紹了譯碼器的定義與譯碼器的分類,其次介紹了譯碼器的作用和譯碼器的工作原理,最后介紹了譯碼器的邏輯功能。

2018-02-08 14:04:06 107559

107559

本文主要介紹了譯碼器的分類和應用。譯碼器指的是具有譯碼功能的邏輯電路,譯碼是編碼的逆過程,它能將二進制代碼翻譯成代表某一特定含義的信號(即電路的某種狀態),以表示其原來的含義。譯碼器可以分為:變量

2018-04-04 11:51:12 37755

37755

本文檔的主要內容詳細介紹的是Verilog HDL入門教程之Verilog HDL數字系統設計教程。

2018-09-20 15:51:26 80

80 本文主要介紹了Verilog HDL 語言的一些基本知識,目的是使初學者能夠迅速掌握HDL 設計方法,初步了解并掌握Verilog HDL語言的基本要素,能夠讀懂簡單的設計代碼并能夠進行一些簡單設計的Verilog HDL建模。

2019-02-11 08:00:00 95

95 本文檔的主要內容詳細介紹的是輕松成為設計高手Verilog HDL實用精解的源代碼合集免費下載。

2019-11-29 17:13:00 202

202 本文檔的主要內容詳細介紹的是使用verilog語言編程的三八譯碼器的工程文件免費下載.

2020-09-22 17:43:15 13

13 電子發燒友網為你提供顯示譯碼器的功能和種類資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-28 08:45:28 7

7 通過Verilog在SRAM讀寫程序源代碼

2021-06-29 09:26:15 7

7 關于Actel 的FPGA的譯碼器的VHDL源代碼(通信電源技術期刊2020年第14期)-關于Actel 的FPGA的譯碼器的VHDL源代碼。適合感興趣的學習者學習,可以提高自己的能力,大家可以多交流哈

2021-09-16 15:18:01 10

10 Verilog HDL入門教程-Verilog HDL的基本語法

2022-01-07 09:23:42 159

159 譯碼器是一個多輸入、多輸出的組合邏輯電路。它的作用是把給定的代碼進行“翻譯”,變成相應的狀態,使輸出通道中相應的一路有信號輸出。譯碼器在數字系統中有廣泛的用途,不僅用于代碼的轉換、終端的數字顯示,還用于數據分配,存貯器尋址和組合控制信號等。不同的功能可選用不同種類的譯碼器。

2023-04-26 14:34:59 3077

3077

譯碼器的邏輯功能是將每個輸入的二進制代碼譯成對應的輸出的高、低電平信號。常用的譯碼器電路有二進制譯碼器、二--進制譯碼器和顯示譯 碼器。譯碼為編碼的逆過程。它將編碼時賦予代碼的含義“翻譯”過來。實現

2023-04-26 15:39:40 4080

4080

譯碼器定義

邏輯功能:將每個輸入的二進制代碼對應輸出為高、低電平信號。

譯碼是編碼的反操作。

2023-04-30 16:19:00 1241

1241

輸入:二進制代碼,有n個;

輸出:2^n 個特定信息。

1.譯碼器電路結構

以2線— 4線譯碼器為例說明

2線— 4線譯碼器的真值表為:

2023-04-30 16:29:00 2335

2335

電子發燒友App

電子發燒友App

評論