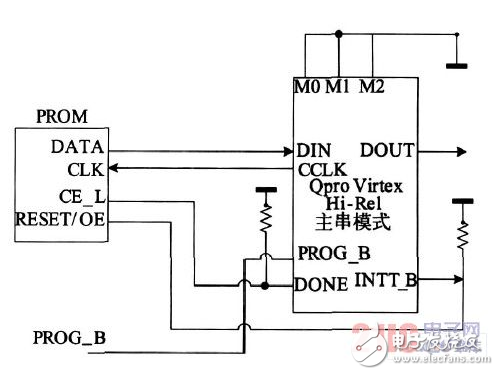

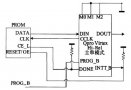

目前,大多數 FPGA 芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常

2022-12-26 18:10:00 1780

1780 上文XILINX FPGA IP之Clocking Wizard詳解說到時鐘IP的支持動態重配的,本節介紹通過DRP進行MMCM PLL的重新配置。

2023-06-12 18:24:03 5528

5528

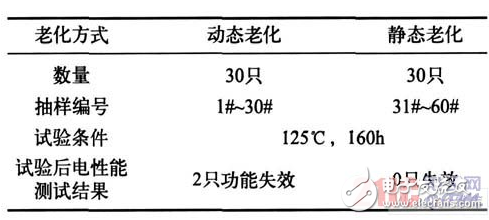

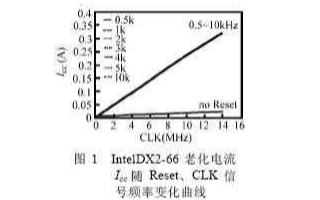

的可靠性,最好的方法是對電路進行篩選,其中老化試驗就是篩選過程中最為重要的環節之一。 考慮到FPGA 電路的工作模式比較復雜,外部需要存儲器或者FLASH 對其進行配置,FPGA 才能動態工作,因此

2011-09-13 09:22:08

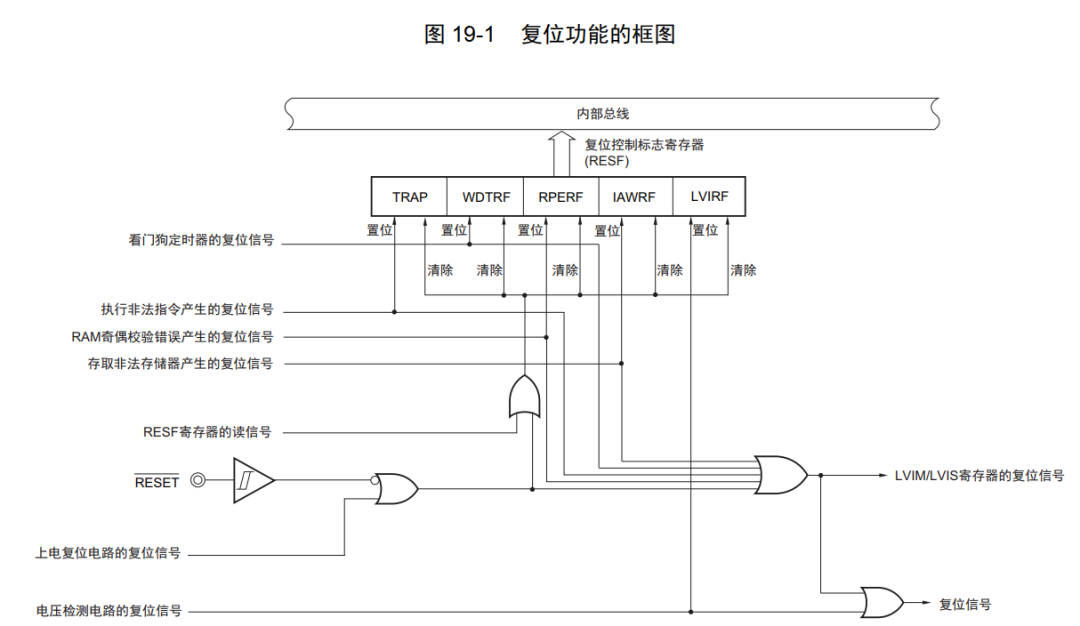

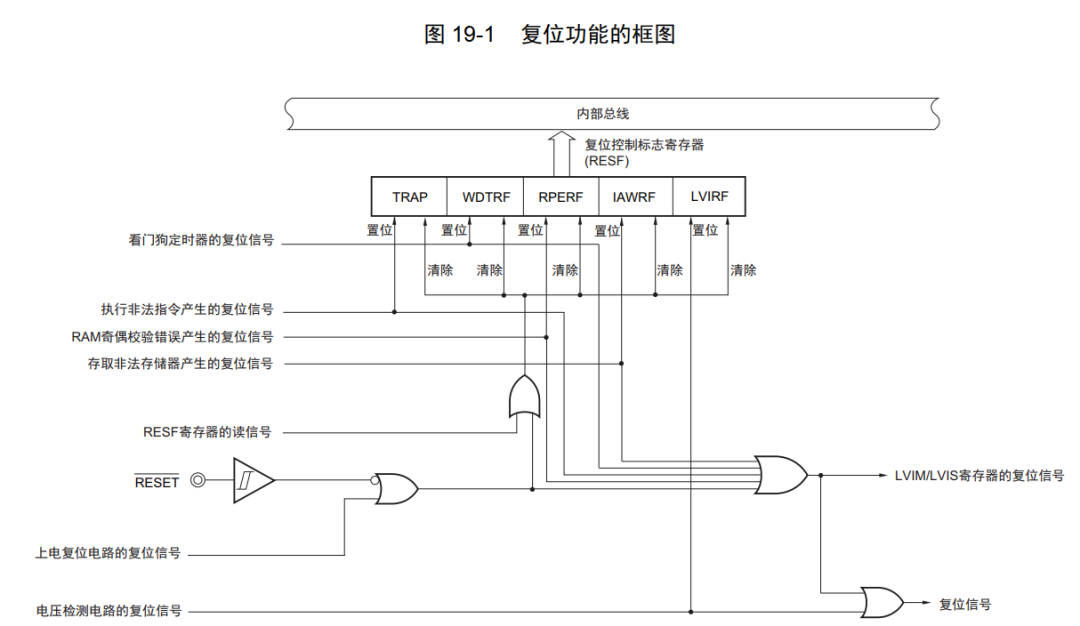

就沒有復位過程;當然了,如果上電復位延時過長,那么對系統性能甚至用戶體驗都會有不通程度的影響,因此,設計者在實際電路中必須對此做好考量,保證復位延時時間的長短恰到好處。關于FPGA器件的復位電路,我們也

2019-04-12 06:35:31

的數碼管的選通控制打開,該位就顯示出字形,沒有選通的數碼管就不會亮。通過分時輪流控制各個數碼管的的COM端,就使各個數碼管輪流受控顯示,這就是動態驅動。在輪流顯示過程中,每位數碼管的點亮時間為1~2ms

2019-04-29 06:35:29

根據重構的方法不同,FPGA的重構可分為靜態重構和動態重構兩種,前者是指在系統空閑期間進行在線編程,即斷開先前的電路功能后,重新下載存貯器中不同的目標數據來改變目標系統邏輯功能。常規SRAM

2011-05-27 10:22:59

FPGA入門門檻相對于其他技術來說比較高,很多同學學習了一段時間,光靠自己研究,覺得太難了,所以就放棄了,從入門到放棄僅需一段短短的時間。過來人建議:學習FPGA,最好可以加入一些學FPGA小組

2019-12-03 10:17:48

各位大佬們,我目前要設計一個老化測試板,主要是接一個20引腳的模塊,我目前不知道需要哪些引腳供電。有人知道嗎?

2018-04-27 09:04:14

BGA老化座中的BGA全稱是BallGridArray(球柵陣列結構的PCB),它是集成電路采用有機載板的一種封裝法。那么這種老化座有什么優勢呢?

?緊湊型設計,提高老化測試板容量

2023-08-22 13:32:03

BGA老化座中的BGA全稱是BallGridArray(球柵陣列結構的PCB),它是集成電路采用有機載板的一種封裝法。那么這種老化座有什么優勢呢? ?緊湊型設計,提高老化測試板容量

2017-06-21 15:48:38

關于css偽類,偽元素詳解總結

2020-05-11 08:44:28

關于手機用小型SAW雙工器的研究動態

2021-05-10 06:05:38

員必須權衡更高性能和更低功耗帶來的競爭優勢。解決此問題的一種途徑是借助一個稱為動態功耗調節(DPS)的過程。圖1. 基于SAR型ADC的數據采集子系統的框圖簡單而言,DPS就是一個在需要時啟用電子元件、在

2018-10-24 09:46:28

Linux電源管理研究筆記—動態電源管理 DPM

2021-12-29 06:35:02

長時間使用過的保險絲還沒有發生熔斷,我們就應該猜測他可能已經老化了,要精確的測量下,這個時候應該引起注意,然后進行更換。所以保險絲的作用在電路中是顯而易見的,但是同時也要注意使用壽命。最后,關于研究保險絲的溫升意義,相信大家都有了解了吧。這里是松美健電子有限公司為您解答。

2017-05-15 10:04:58

課程簡介:本課程基于STM32F103RC講解,通過從MCU上電開始啟動開始分析,詳解MCU的運行過程,講師“東方青”多年從事開發經驗而言,學習Cortex-M系列的MCU,我們不僅僅只是會使用固件

2021-11-03 07:58:18

本文將討論信號完整性網絡分析儀SPARQ動態范圍以及考慮一些關鍵指標的影響,并和競爭對手的兩種時域測試設備在動態范圍和關鍵指標進行了深入比較,提供了推導過程并通過實驗結果來驗證計算的準確性。動態范圍

2019-06-05 07:28:37

HiveSQL解析過程詳解

2019-06-04 16:27:33

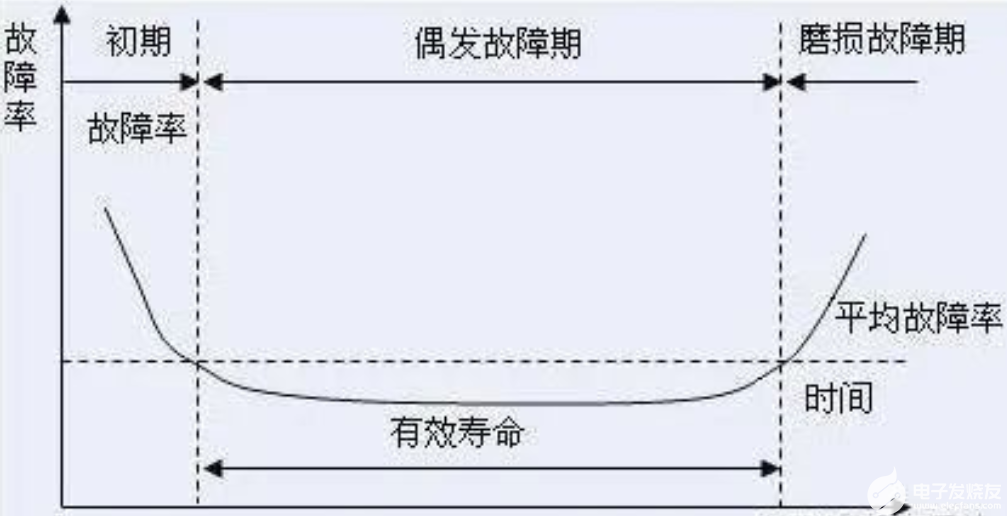

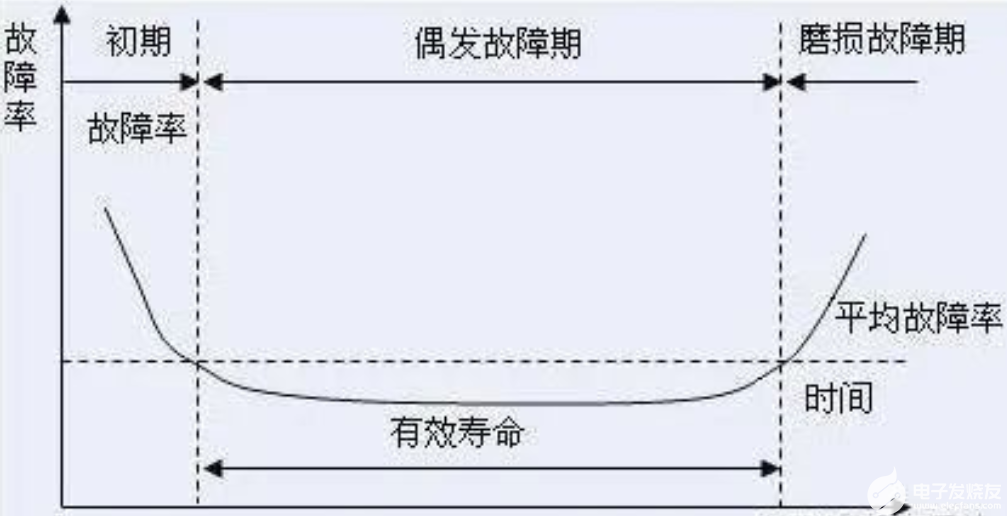

LED老化測試是根據產品的故障率曲線即浴盆曲線的特征而采取的對策,以此來進步產品的可靠性。有頻率的題目,就不是恒流了。交流或脈動電流源可以設計成有效值恒定不變,但這種電源無法稱做「恒流源」。 恒流

2013-02-28 17:11:10

本帖最后由 vktina1 于 2016-4-4 23:14 編輯

電子書:LabVIEW與Matlab的聯合仿真過程詳解

2016-04-03 01:24:28

PS2251-61量產詳解過程

2012-04-05 09:21:03

`Xilinx系列FPGA芯片IP核詳解(完整高清書簽版)`

2017-06-06 13:15:16

一階電路過渡過程的研究

2008-12-03 14:19:00

在labview中,調用動態庫詳解

2015-07-31 21:47:10

《LabVIEW與Matlab的聯合仿真過程詳解.pdf》有需要的xdjm就拿去吧。

2015-12-23 22:59:28

【PDF】LabVIEW與Matlab的聯合仿真過程詳解

2015-12-04 19:50:28

處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號

2019-07-05 06:21:42

請問大家,有什么仿真軟件可以做電路元器件的加速老化仿真實驗,PSpice可以嗎?

2018-06-07 09:52:58

基于FPGA的FFT算法研究

2012-08-24 01:09:50

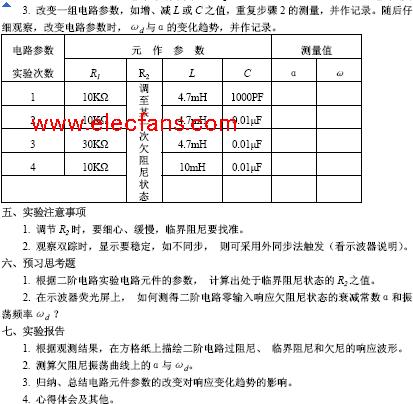

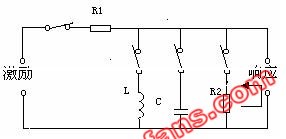

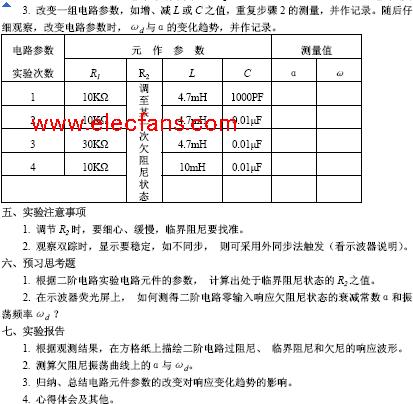

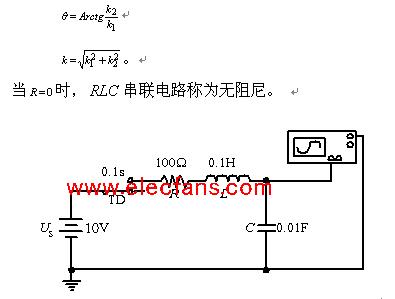

一.實驗目的1. 學習用實驗的方法來研究二階動態電路的響應,了解電路元件參數對響應的影響。2. 觀察、分析二階電路響應的三種狀態軌跡及其特點,以加深對二階電路響應的認識與理解。二.實驗設備序號名 稱

2021-06-04 06:43:14

結構,上層為配置存儲器,下層是硬件邏輯層。通過上層配置信息控制硬件層門電路的通斷,改變芯片內基本邏輯塊的布線,從而形成特定的功能。這種架構為動態重構技術實現提供了可能。一個FPGA大型數字系統總是由很多

2015-02-05 15:31:50

基于DDS和FPGA技術的高動態擴頻信號源的研究

2012-08-17 11:33:36

處理系統中最重要的部件之一。FPGA是當前數字電路研究開發的一種重要實現形式,它與全定制ASIC電路相比,具有開發周期短、成本低等優點。但多數FPGA不支持浮點運算,這使FPGA在數值計算、數據分析和信號

2019-08-15 08:00:45

FPGA配置原理簡介基于模塊化動態部分重構FPGA的設計方法如何去實現FPGA動態部分的重構?

2021-04-29 06:33:12

有沒有關于STM32固件庫詳解資料分享?

2021-10-13 09:04:51

電子DIY過程詳解.pdf

2011-08-05 11:58:57

最近,您可能聽說了這則新聞 — 智能手機制造商為了適應電池的老化而將舊型號的產品降速,以防止電池老化的手機意外關機。

2019-08-13 08:16:30

設計。電流鏡設計步驟詳解【全過程】[/hide]大致內容為: 1、邊界條件2、設計指標 3、確定電路拓撲結構4、設計變量初始估算5、HSPICE仿真驗證6、版圖設計7、討論&結論

2011-11-04 16:31:27

100度以上不等,在高溫通電老化過程中,分為靜態老化和動態老化二種,其一是在設置的高溫環境中,通電老化,使產品仿真在65度以上的環境工作,老化時間一般要求12小時,其二是動態高溫老化,是在高溫環境下

2016-09-26 23:17:18

劣化因表面氧化使活性碳結構部分被破壞,另一方面老化過程也造成了電極表面雜質沉積,導致大部分的孔被堵住。3、電解液分解電解液的不可逆分解是大大縮短超級電容的工作時長,是老化的另一個原因。電解液進行氧化

2022-08-15 17:11:43

研究了熱老化及老化過程對高分子PTC材料電阻值的影響,電老化對耐流、耐壓、耐雷擊等電性能的影響。結果表明,不同的熱老化條件可使高分子PTC材料電阻值發生不同程度的變化,電老化可有效改善其電性能。

2021-03-25 07:14:21

高速公路GPS車輛動態監控技術研究本文結合吉林省科技發展計劃項目“吉林省高速公路路網指揮調度系統數字平臺開發”,針對吉林省高速公路運營過程中存在的問題,通過對國內外車輛監控系統發展的研究,提出

2009-04-16 13:47:49

動態調動自動化系統的研究與開發——從典型事故過程看預防大停電:

2009-07-02 16:24:29 18

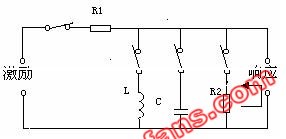

18 動態網絡響應的研究:1、學會用示波器研究電路中的時域響應的基本方法。2、觀察RC電路中的零輸入響應,階躍響應和矩形脈沖響應。3、研究時間常數τ的意義實驗原理

2009-07-03 01:10:14 10

10 字母檢索SMT術語詳解A Accelerate Aging ——加速老化,使用人工的方法,加速正常的老化過程。 Acceptance Quality Level (AQL) —— 一批產品中最大可以接

2008-08-03 11:37:55 1707

1707 二階動態電路響應的研究

一、實驗目的1. 測試二階動態電路的零狀態響應和零輸入響應, 了解電路元件參數對響應的影響。2.

2008-09-24 09:40:03 5285

5285

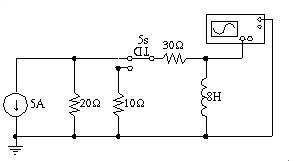

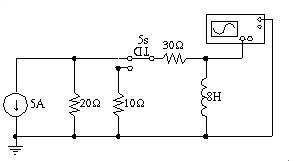

實驗七:一階動態電路的動態過程

一、實驗目的5. 觀察一階動態電路的動態過程。6. 確定電路的時間常數 。二、實

2008-09-25 15:32:24 9013

9013

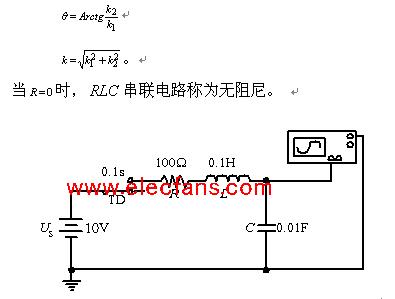

實驗八: 串聯電路的動態過程

一、實驗目的1. 研究 串聯電路的電路參數與電容電壓暫態過程的關系。2. 觀察 串聯

2008-09-25 15:33:53 2472

2472

實驗 二階動態電路響應的研究一. 實驗目的

1. 學習用實驗的方法來研究二階動態電路的

2008-11-02 22:42:02 12273

12273

高分子PTC過流保護性能的老化方法與技巧

摘要:研究了熱老化及老化過程對高分子PTC材料電阻值的影響,電老化對耐流、耐壓、耐雷擊等電性能的影響

2009-11-28 08:57:32 1095

1095 字母檢索SMT術語詳解A Accelerate Aging ——加速老化,使用人工的方法,加速正常的老化過程。 Acceptance Quality Level (AQL) —— 一批產品中最

2010-02-21 11:19:35 1270

1270 隨著FPGA 電路在軍工和航空航天領域的應用,其高可靠性尤為重要,為了提高電路的可靠性,最好的方法是對電路進行篩選,其中老化試驗就是篩選過程中最為重要的環節之一。

2011-02-22 11:18:36 2386

2386

利用LabVIEW軟件編程建立了接觸器閉合過程的動態數學模型,模型實現了對接觸器動態過程的仿真分析。在此基礎上仿真研究了不同合閘相角、線圈電壓對接觸器閉合過程及其對觸頭彈跳

2011-12-23 14:43:15 30

30 圖文詳解T60機器拆解過程.

2012-04-24 15:12:40 37

37 3 FPGA設計流程 完整的FPGA 設計流程包括邏輯電路設計輸入、功能仿真、綜合及時序分析、實現、加載配置、調試。FPGA 配置就是將特定的應用程序設計按FPGA設計流程轉化為數據位流加載

2013-01-16 11:52:22 16

16 基于FPGA的DDS信號源研究與設計_南楠.pdf 關于干擾的,不知道。

2016-05-16 17:15:25 4

4 基于FPGA的CMOS圖像感器IA_G3驅動電路的研究

2016-08-29 16:05:01 15

15 電路教程相關知識的資料,關于磁珠資料--詳解磁珠及其作用

2016-10-10 14:34:31 0

0 VB中關于MSComm控件使用詳解

2016-12-16 15:35:33 18

18 阻增量光伏動態模型研究_倪雨

2017-01-07 15:13:24 0

0 正弦激勵下的RL一階電路暫態過程實驗研究

2017-09-16 09:54:24 25

25 利用掃描電子顯微鏡和傅里葉變換衰減全反射紅外光譜儀對某型號光伏背板的結構和成分進行表征,研究了其耐濕熱老化性能。結果表明,該背板為三層結構,上下層分子結構分別為 PVF和 EVA,經過 2500h

2017-10-18 14:56:42 12

12 光纖陀螺信號處理電路中FPGA與DSP的接口方法研究

2017-10-20 08:40:25 2

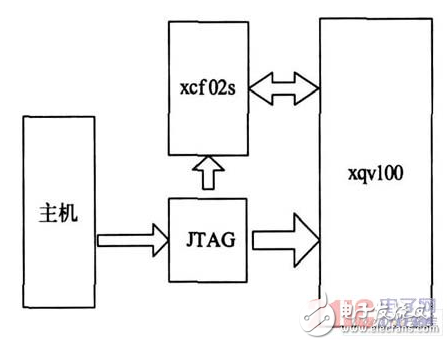

2 隨著FPGA的廣泛應用, 其實現的功能也越來越多, FPGA 的動態重構設計就顯得愈發重要。在分析Xilinx Vertex II Pro系列FPGA配置流程、時序要求的基礎上, 設計了基于CPLD

2017-11-22 07:55:01 937

937

FPGA 具有高速度、高集成度,可重復編程的特點,將其用于電路系統設計,可簡化電路設計,增強電路功能。而作為電路系統的“中樞控制神經”,FPGA 的故障會引起整個電路系統的癱瘓,而用一般的測試方法很難對其實施故障測試診斷。

2018-07-18 14:37:00 1088

1088

給出了一個基于CPLD/FPGA設計的軟件模塊化LED顯示電路 , 通過串行掃描方式驅動LED數碼管,可較少地占用可編程器件資源;并利用MAXPLUS II對動態掃描LED顯示電路進行仿真。最后

2017-11-30 14:41:30 16

16 已有研究表明,鍵合線老化脫落失效是影響絕緣柵雙極型晶體管( IGBT)可靠性的主要因素之一。以此為研究背景,首先根據IGBT模塊內部鍵合線的結構布局與物理特性,分析鍵合線等效電阻與關斷暫態波形的關系

2018-01-02 11:18:14 5

5 由于骨牌邏輯電路通常較互補式金氧半組件電路計具有較小的面積與更快的速度,所以已經被廣泛使用于設計高速電路如微處理器的設計中。雖然有許多關于動態電路的研究,然而大部份的研究卻忽略探討如何實現其研究

2018-01-24 15:10:13 0

0 本文檔內容介紹了基于xilinxFPGA選型詳解,供參考查閱

2018-03-15 15:58:01 4

4 FPGA(Field-Program mable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域

2018-07-28 11:08:32 2159

2159 老化是一種能夠將產品早期故障剔除的無損篩選試驗技術。集成電路的老化過程實質上就是通過對其施加應力,加速其內部潛在缺陷暴露的過程。經過老化,可以使有缺陷的集成電路在上機使用前失效,從而保證了集成電路

2019-10-15 08:05:00 2000

2000

FPGA 動態局部可重構技術通常將系統劃分為固定模塊和可重構模塊,可重構模塊與其他模塊之間的通信都是通過使用特殊的總線宏實現的。總線宏的正確設計是實現FPGA 動態局部可重構技術的關鍵。在研究

2018-12-14 14:27:35 3

3 動態拉伸型臭氧老化試驗箱,系屬臭氧氣候動態模擬設備之一,適用于考核硫化橡膠等制品在靜態拉伸變形下,暴露于含有一定臭氧濃度和溫度的空氣環境中,但無直射光照下的嚴酷條件的適應性試驗,可供各種科研機構及廠礦中心試驗室對產品試樣的可靠性進行老化試驗箱用。

2020-03-22 17:28:00 477

477 任何電子設備都避免不了老化的問題,用的久了內部的零部件都會老化,從而影響性能,路由器自然也不例外,那么每天晚上關閉路由器是否就會減緩它的老化呢?

2020-06-12 14:36:08 5510

5510 大蔥種子活力的方法首先需要從探明作物種子活力下降的原因入手,因此試驗中采用種子老化箱人工老化的方式,研究了作物種子在老化過程中所發生的活力變化,并將實驗記錄了下來。 種子老化箱的種子老化過程詳解 1.用扦樣器抽取

2020-07-30 14:42:22 1495

1495 如果你在采用FPGA的電路板設計方面的經驗很有限或根本沒有,那么在新的項目中使用FPGA的前景就十分堪憂——特別是如果FPGA是一個有1000個引腳的大塊頭。繼續閱讀本文將有助于你的FPGA選型和設計過程,并且有助于你規避許多難題。

2020-11-01 09:44:54 1826

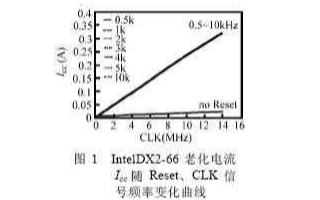

1826 針對不同工藝、不同設計的功能全兼容集成電路等效老化的需要,提取出了集成電路等效老化的特征參數—“歸一化老化電流”指標α,并討論了等效老化信號的確定方法。結合集成電路等效老化信號確定方法

2021-03-26 14:59:53 4400

4400

現代企業的飛速發展就意味著機械設備的負債運行,所以就要用并聯電容器進行無功補償。而實際的電容器在使用的時候,會因為過電壓、過熱等狀況,而呈現熱老化和電老化。接下來就講講關于產品在老化這一塊的詳解和解決方法。

2021-05-26 14:24:24 6221

6221 (網盤)關于SDRAM和錄音機等FPGA視頻(android嵌入式開發教程)-關于SDRAM和錄音機等FPGA視頻,一步一步的講解,真的很詳細,適合大家自學研究。

2021-08-04 12:21:50 15

15 FPGA-DCM使用詳解(通信電源技術期刊編輯部電話)-該文檔為FPGA-DCM使用詳解文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,

2021-09-28 11:22:17 6

6 修復水環真空泵軸承位磨損的過程詳解

2022-03-07 10:33:16 4

4 隨著半導體電子技術的進步,老化測試已成為保證產品質量的關鍵流程。除了半導體元件外,PCB、IC 和處理器部件也都需要在老化條件下進行測試。本篇文章納米軟件Namisoft小編將帶大家分享一下關于芯片

2023-01-13 10:50:51 2101

2101

電路板高溫老化房是對PCBA板進行長時間的通電測試,模擬用戶使用,保持其長時間工作并觀察其是否出現任何失效故障,檢測一些不易發現的缺陷,以及檢驗產品的使用壽命,可確保產品的穩定性,只有經過老化測試

2023-03-01 13:14:49 317

317

FPGA中關于SPI的使用

2023-04-12 10:13:16 531

531 認為,晶體的老化主要起因于晶片表面附著物的脫落、研磨過程對晶片造成的應力、上架和鍍膜過程形成的支架與晶片及電極膜與晶片間的應力變化、晶體表面吸附的氣體以及由于漏氣造

2022-04-22 10:29:15 843

843

晶振老化,是指晶體的振動頻率隨著時間的變化而產生的頻率漂移,其頻率漂移的速率可用規定時限的最大變化率來表示。在晶體使用前期,老化主要受元件內部應力釋放的影響,頻率逐漸升高。而后期受電極膜吸附

2022-04-22 10:27:12 1137

1137

壓敏電阻是目前應用范圍最廣泛的電子元件之一,在應用的過程中,壓敏電阻老化的問題是其最大的缺點,將會嚴重干擾系統的正常安全工作,本文將介紹壓敏電阻的防老化方法,能夠幫助工程師有效解決壓敏電阻的老化情況

2023-04-10 09:40:09 413

413

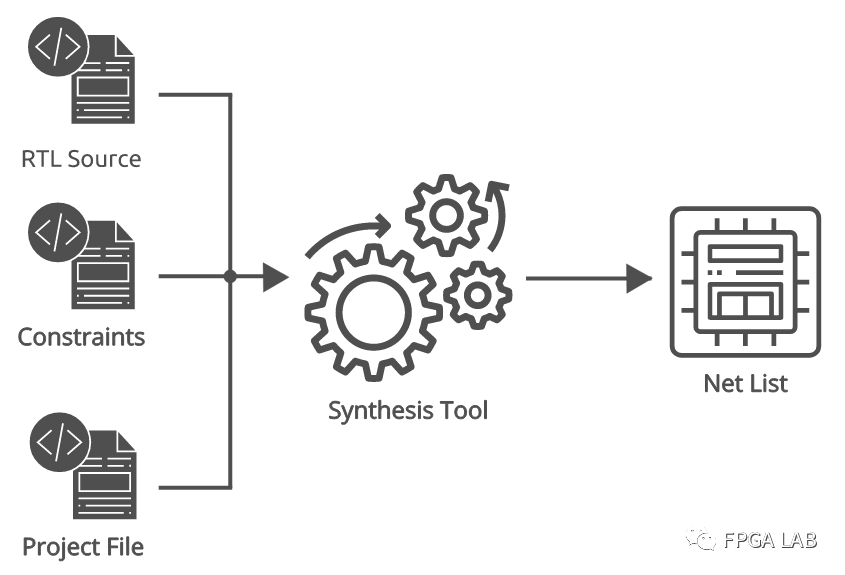

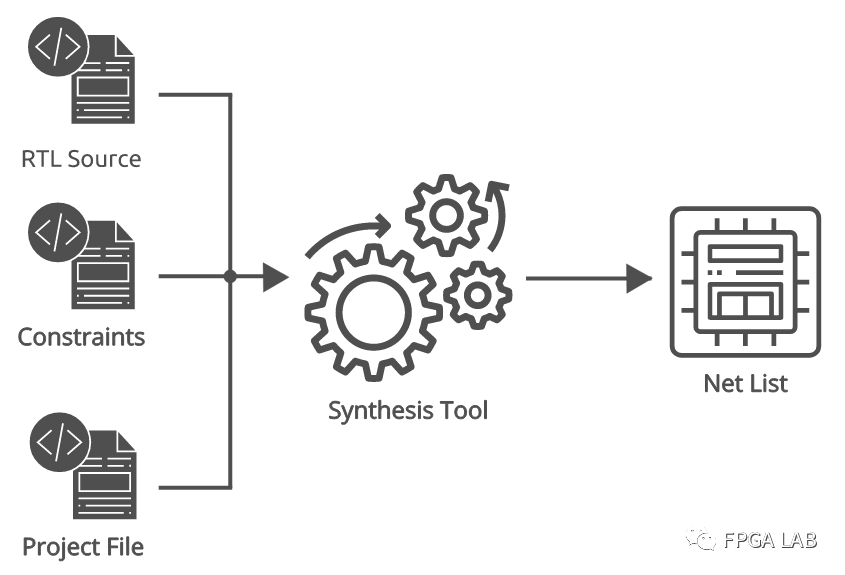

構建FPGA的第一階段稱為綜合。此過程將功能性RTL設計轉換為門級宏的陣列。這具有創建實現RTL設計的平面分層電路圖的效果。

2023-06-21 14:26:16 511

511

RL78啟動過程詳解

2023-09-28 16:39:32 744

744

電子發燒友網站提供《基于FPGA的DMD驅動控制電路的研究設計.pdf》資料免費下載

2023-11-17 15:44:26 3

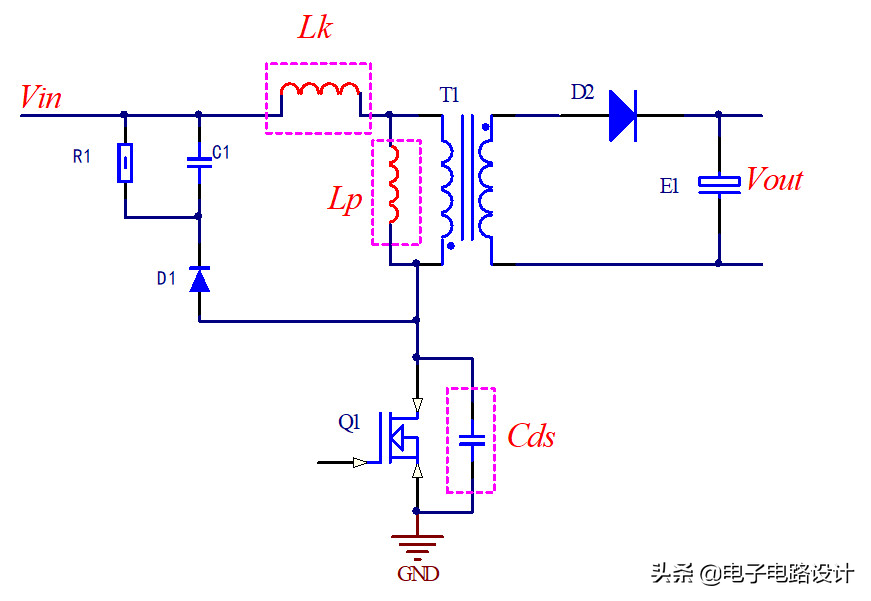

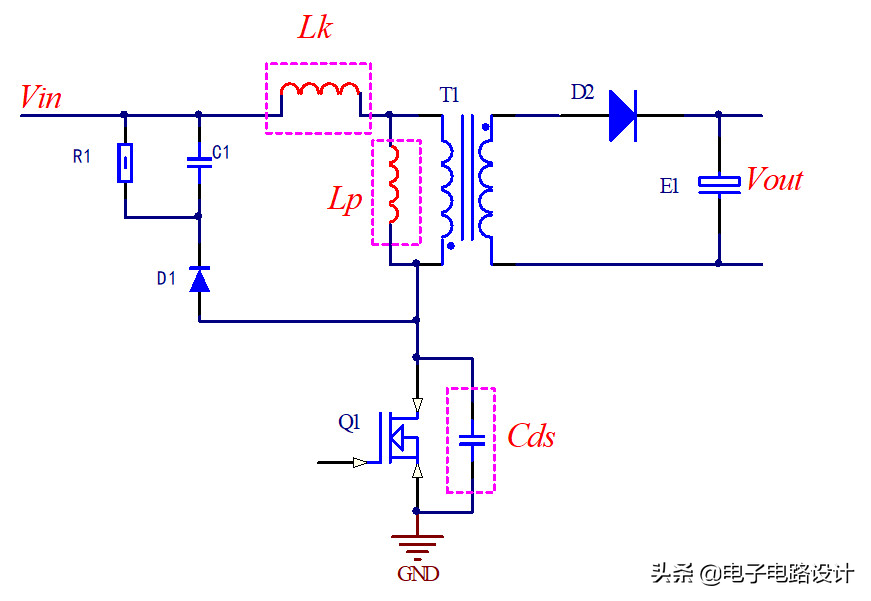

3 詳解開關電源RCD鉗位電路工作過程,為什么它能夠吸收能量?

2023-12-06 16:14:40 326

326

絕緣老化是指什么 老化原因 怎樣延緩絕緣老化? 絕緣老化是指絕緣材料在長期使用過程中逐漸失去其原有性能,最終導致絕緣性能下降,不能滿足電器設備的工作要求。絕緣老化是一個復雜的過程,其原因可分為內部

2023-12-29 11:03:22 518

518 晶振老化率影響及降低方法? 晶振老化率是指晶振在使用過程中逐漸失去性能或產生偏差的速率。晶振老化率的增加會導致頻率不準確、抖動增加、功耗增加等問題,對于一些對時鐘要求較高的應用來說是不可接受的。然而

2024-01-24 15:40:29 116

116 基于振弦采集儀的工程結構動態監測研究 基于振弦采集儀的工程結構動態監測研究,是指利用振弦采集儀對工程結構進行動態監測和分析的研究工作。 振弦采集儀是一種常用于結構健康監測的設備,它通過采集結構的振動

2024-01-25 10:50:48 137

137

電子發燒友App

電子發燒友App

評論