注意:本博文介紹了利用 POST_CRC 試錯的方法,但總體而言,賽靈思推薦在所有架構上使用 Soft Error Mitigation (SEM) IP。SEM IP 提供了一種可用于測試 SEU 檢測與糾正能力的機制并提供了更強大的調試能力。

本博文中討論的功能僅支持 7?系列器件。

| 功能 | 7系列FPGA | Kintex UltraScale 和 Virtex UltraScale | Kintex UltraScale+ 和 Virtex UltraScale+ |

| Readback CRC/POST_CRC | 是 | 否,使用 SEM IP 替代 | 否,使用 SEM IP 替代 |

?

賽靈思 FPGA 中循環冗余校驗?(CRC)?的不同類型:

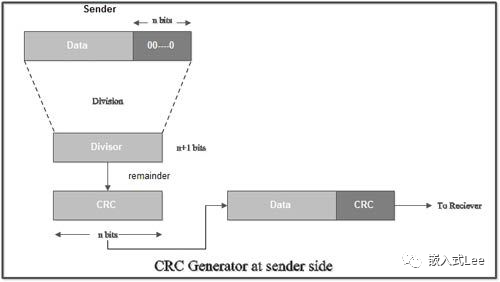

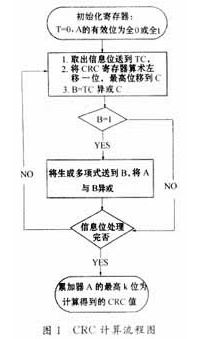

1)?一般?CRC?校驗

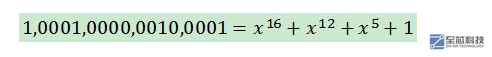

在一般比特流加載過程中,CRC 校驗利用 CRC 寄存器進行。該“CRC 寄存器”的描述詳見《7 系列 FPGA 配置用戶指南》(官網搜索?UG470)。

FPGA 在比特流被加載時計算 CRC 值,然后該值與在比特流加載結束時預期的 CRC 值進行比較。如果兩個值匹配,則FPGA 成功加載。

一般情況下默認啟用 CRC 校驗。比特流屬性為 BITSTREAM.GENERAL.CRC,其中有效選項包括“ENABLE”(啟用)或“DISABLE”(禁用)。

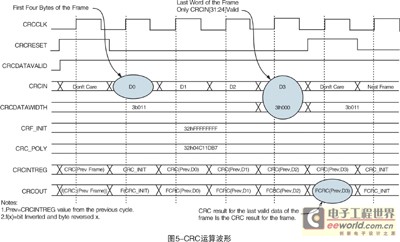

2)?回讀?CRC/POST CRC?校驗

POST_CRC 校驗在配置 FPGA 之后,設計運行過程進行。

一般情況下,比特流 CRC 校驗是一種獨立功能,具有其自己的 CRC 校驗寄存器。POST_ CRC 校驗具有用于存儲校驗值的不同以上比特流 CRC 的寄存器。

啟用?POST_CRC?校驗的目的

啟用 POST_CRC 校驗的目的是檢測單粒子翻轉?(SEU)。SEU 導致配置存儲器中的數位翻轉。POST_CRC 可與 FRAME_ECCE2 原語配合使用,以便提供針對此等錯誤的額外功能和更好的可見性。我們可利用 FRAME_ECCE2 的輸出監控錯誤檢查和糾正?(ECC)?和回讀 CRC 電路的狀態。

如需了解更多有關?FRAME_ECCE2?原語的詳細信息,請參閱《Vivado Design Suite 7?系列 FPGA?和 Zynq-7000 SoC?庫指南》(官網搜索?UG953)。

用戶通常想要測試這種崩潰發生時的實例,以便確保此等錯誤被成功檢測到。測試插入錯誤的一種方法是編輯 PRE_COMPUTED CRC 值。

測試插入錯誤的步驟

將以下設置放置在設計 XDC 中:

set_property POST_CRC ENABLE [current_design]

#Enables the Post CRC checking

set_property POST_CRC_SOURCE PRE_COMPUTED [current_design]

#Determines an expected CRC value from the bitstream

?

set_property POST_CRC_ACTION CONTINUE [current_design]

#Even if a CRC error is detected, continue CRC checking.

#Other options include HALT, CORRECT_AND_CONTINUE and CORRECT_AND_HALT

set_property POST_CRC_INIT_FLAG ENABLE [current_design]

#Leaves the INIT_B pin enabled as a source of the CRC error signal. Useful especially if FRAME_ECC is not used

如需了解更多有關這些設置的詳細信息,請參閱《Vivado Design Suite?屬性參考指南》(官網搜索?UG912)。

運行設計流程并生成比特流。在生成了比特流之后,PRE_COMPUTED CRC 的值可在 .bit 文件中校驗。該值會是非零值。

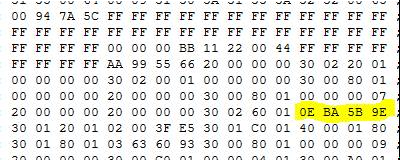

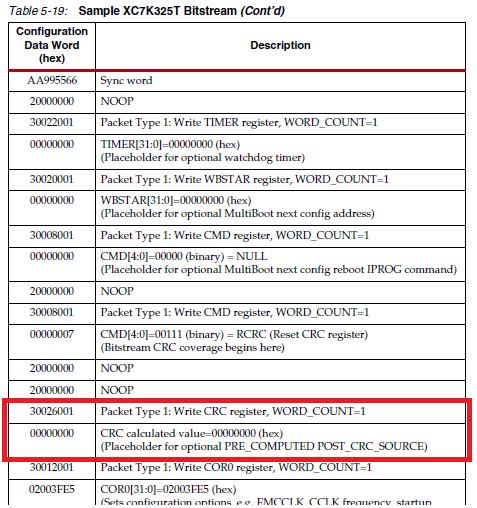

若要確定?PRE_COMPUTED CRC?值在比特流中的哪個位置,可查閱《7?系列 FPGA?配置用戶指南》(UG470)?中的示例 7 系列比特流。

若要測試插入錯誤,您就要禁用一般 CRC 校驗,以便讓比特流成功載入。切記,如果對位于正常 CRC 覆蓋范圍內的比特流進行了任何編輯,即會標注 CRC 錯誤并阻止比特流加載。

若要禁用一般 CRC 校驗,您應使用以下設置:

set_property BITSTREAM.GENERAL.CRC DISABLE [current_design]

#Disables the general CRC checking

set_property POST_CRC ENABLE [current_design]

#Enables the Post CRC checking

set_property POST_CRC_SOURCE PRE_COMPUTED [current_design]

#Determines an expected CRC value from the bitstream

set_property POST_CRC_ACTION CONTINUE [current_design]

#Even if a CRC error is detected, continue CRC checking.

#Other options include HALT, CORRECT_AND_CONTINUE and CORRECT_AND_HALT

set_property POST_CRC_INIT_FLAG ENABLE [current_design]

#Leaves the INIT_B pin enabled as a source of the CRC error signal.Useful especially if FRAME_ECC is not used

再次運行設計流程并生成比特流。

在生成比特流之后,您應觀察 PRE_COMPUTED CRC 的值是否為零。這是禁用 GENERAL.CRC 的結果,以便進行錯誤測試。

由于預計有前面的非零值,要配置器件并觀察其行為。

INIT_B 引腳的監控應顯示 CRC 錯誤。

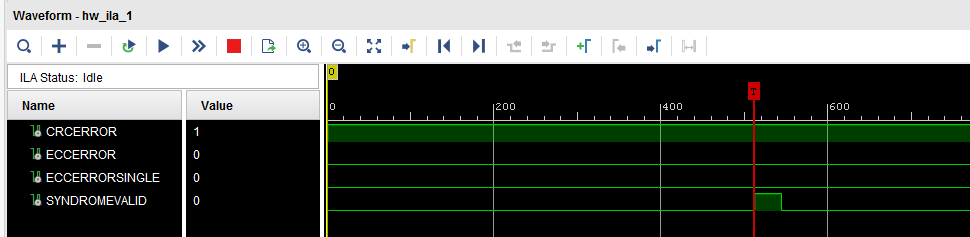

FRAME_ECCE2 也可被用于接收連接到 ILA 上的 FRAME_ECCE2 發出的輸出信號。然后它將有可能觀察到 CRCERROR。

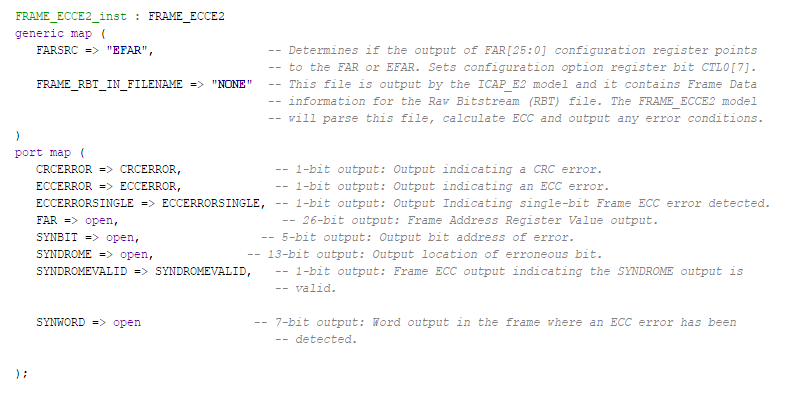

下文的例化可被用于 FRAME_ECCE2 原語的連接:

然后輸出可被傳輸給 ILA。

當器件被編程后,通過校驗 ILA 上的信號,它應有可能查看類似于以下示例的輸出。例如,由于未找到預期的非零 PRE_COMPUTED 值,標注了 CRCERROR 錯誤。

可以理解的是,大部分用戶都想要測試錯誤檢測,以確定在此等錯誤被檢測到時,將會以某種形式予以報告。該測試可讓用戶堅信,在真實的情景中,錯誤會被正確檢測并報告。

如上文所述,由于 SEM IP 所提供的能力,賽靈思推薦使用 SEM IP,而不是 POST_CRC。POST_CRC 的功能在較新的架構中不受支持。

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論