本文首先介紹了各種分頻器的實現原理,并在FPGA開發平臺上通過VHDL文本輸入和原理圖輸入相結合的方式,編程給出了仿真結果。最后通過對各種分頻的分析,利用層次化設計思想,綜合設計出了一種基于FPGA的通用數控分頻器,通過對可控端口的調節就能夠實現不同倍數及占空比的分頻器。

2015-05-07 09:43:16 4685

4685

大規模的整數加法在數字信號處理和圖像視頻處理領域應用很多,其對資源消耗很多,如何能依據FPGA物理結構特點來有效降低加法樹的資源和改善其時序特征是非常有意義的。

2023-11-08 09:06:32 636

636

12864如何能在串行模式下實現任意點畫點畫線的功能啊 ,晚上的很多資料都是寫的并口模式下的 。找到一些資料說可以自己建立一個數據緩存區域用作虛擬的cdram但是不太懂,希望有人能幫我解答一下

2020-06-05 05:55:09

提高競爭力,嵌入式系統開發人員需要一種能夠幫助他們開發獨具優勢產品的解決方案,非常靈活,效率也非常高。基于FPGA的單芯片實現方法具有低成本和快速面市等優點,是多芯片和ASICSoC非常有吸引力的替代

2021-07-14 08:00:00

CPU 的控制下按照順序依次實現的。而 FPGA 設計,實質是電路設計,是在一個可以現場編程的通用邏輯器件中去搭建各種具有一定功能的邏輯電路,各個邏輯電路間是各自獨立的,能夠并行執行。同時,各個功能

2020-12-04 18:47:16

的。傳統SPI接口的FPGA實現往往使用廠家提供的IP核實現,但是經筆者實踐發現,這種方法雖然能夠滿足基本SPI通信要求而且速度比較快,但是設計不夠靈活,不利于功能擴展,例如用戶無法知道其內部工作狀況,控制

2019-05-05 09:29:34

對于常規MCU,通用輸入輸出(GPIO)是其最基本、最常用的功能,用于實現最基本的數字量輸入和輸出。信號一般為:以3.3VDC為高電平的LTTL電平以5.0VDC為高電平的TTL電平。一般情況下

2021-11-03 08:36:10

LTC2983為何能夠測量18個兩線式RTD看了就明白

2021-03-29 06:03:54

LabVIEW如何能夠將三維平面圖控件輸出的圖像從word 和 excel打印輸出呢?

2015-11-22 15:48:58

大家好: MIMXRT1601這個芯片并沒有PDM接口, 如何能實現8通道的pdm麥克風數據采集。另外,MQS inte**ce 是實現了什么功能, 誰能簡單的給介紹一下。

2022-01-12 07:33:34

可編程控制器的發展經歷了哪些階段?PLC的特點是什么?PLC如何能夠更加開放?

2021-11-03 07:33:16

基于SDRAM控制器實現FPGA模塊化和通用性的解決方案設計

2020-12-22 07:58:55

大家好,請教一下:F4的SPI口如何能實現幀長為24bit的操作呢(DAC接口時序為24bit),不用GPIO模擬,直接讓SPI + DMA支持,以免占用太多CPU資源。謝謝!

2019-03-14 07:44:01

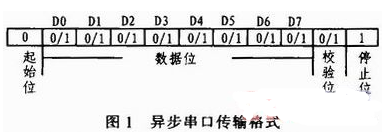

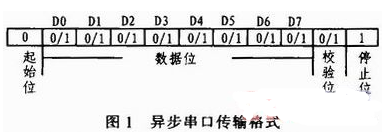

的UART的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA片上UART的設計,給出了仿真結果。關鍵詞:通用異步收發器;串口通信;現場可編程邏輯器件;有限狀態機

2019-06-21 07:17:24

,并設計了基于FPGA的通用硬件平臺。在此平臺上,通過PC機下載軟件,實時實現了軟件無線電中頻至基帶的波形處理和多種不同的調制解調方式。

2019-05-28 06:39:46

進行LabVIEW圖形化的開發,大大加快了FPGA的開發速度以及降低了FPGA的開發難度;該技術被國際巨頭壟斷長達數年之久;同時我們現在提供兩款產品分別是Pocket-RIO和Atom-RIO來佐證能夠實現上述所述內容。體現我們有打破技術壟斷的能力,以及通過該技術造福更多人類的決心。`

2017-02-06 15:08:40

大神門,使用定時器控制pwm發送脈沖,如何能夠同時控制頻率,脈沖個數。因為需要精準控制步進電機轉動角度,還有速度,需要這個功能。并且頻率需要能夠根據速度來改變。

2023-08-05 07:09:36

大神門,使用定時器控制pwm發送脈沖,如何能夠同時控制頻率,脈沖個數。因為需要精準控制步進電機轉動角度,還有速度,需要這個功能。并且頻率需要能夠根據速度來改變。

2024-03-14 07:02:41

循環來實現最低1.25M的數字時鐘輸出(就是第一個周期賦1,第二個周期賦0,無限循環),可是如何能夠做到更低的時鐘信號輸出?比如說我需要一個180KHz的精確時鐘信號,能實現嗎?又該如何實現?若有

2013-01-08 20:20:14

通信和多媒體應用的發展,如互聯網通信、安全無線通信以及消費娛樂設備,都在驅動著對能夠有效實現復數運算和信號處理算法的高性能設備的需求。這些應用中需要一些典型的DSP算法包括快速傅里葉變換(FFT

2021-12-15 06:30:00

在嵌入式軟件中,如何能使程序簡潔清晰?如何能使程序高效運行?

2021-12-23 07:51:28

提高競爭力,嵌入式系統開發人員需要一種能夠幫助他們開發獨具優勢產品的解決方案,非常靈活,效率也非常高。基于FPGA的單芯片實現方法具有低成本和快速面市等優點,是多芯片和ASICSoC非常有吸引力的替代

2021-07-12 08:00:00

基于FPGA的通用異步收發器設計

2012-08-18 00:03:20

基于FPGA的通用高速串行互連協議設計基于FPGA的通用高速串行互連協議設計

2012-08-11 15:46:52

是處理數字信號如圖形、語音及圖像等領域的重要變換工具。快速傅里葉變換(FFT)是DFT的快速算法。FFT算法的硬件實現一般有3種形式:1)使用通用DSP來實現;2)用專用DSP來實現;3)通過FPGA來

2009-06-14 00:19:55

說明了現場可編程門陣列的內部工作原理,其由嵌入在通用路由結構中的邏輯塊組成。這邏輯門陣列是FPGA中的G和A。邏輯塊包含用于執行簡單組合邏輯的處理元件以及觸發器用于實現時序邏輯。因為邏輯單元通常只是

2023-09-21 06:04:41

Peter認為,鑒于其高性能、易編程及低成本特點,GPGPU技術在許多情況下能夠替代FPGA和DSP

2019-10-17 08:07:18

如何能提高權限啊???

2011-11-24 10:36:48

在使用這個主板時,我是一個完全的初學者。有人可以解釋一下我如何能夠從Atlys Spartan-6開發板上的VHDCI連接器讀取值嗎?我已經安裝了Digilent Adept,在搜索了參考手冊后

2019-09-24 09:58:19

請問,在含有BGA的PCBlayout中。經常會遇到需要換pin上的網絡進行布線,如何能夠快速的對BGA上面的網絡進行自動交換

2019-06-18 03:56:58

如何能夠讓ESP8266主動連接到到無線路由呢?怎樣通過按鍵進行smartconfig自動連接WiFi呢?

2021-12-17 06:54:43

通用測試系統是如何組成的?如何實現通用測試系統的硬件設計?如何實現通用測試系統的軟件設計?

2021-04-14 06:47:55

文中采用Ahera公司最新、具有最佳性能、最大密度和最低功耗的高端FPGA StratixⅢ設計了基于CPCI總線的通用FPGA信號處理板,并在某雷達系統中進行了實際應用。

2021-05-07 06:54:25

本文介紹了采用Xilinx公司的Spartan-3 FPGA實現通用視頻采集系統的設計方案。

2021-06-08 06:34:30

以避免對FPGA邏輯資源的浪費,實現最優設計。但對浮點數的獲取卻關注很少。在浮點運算中,單精度浮點以其極強的通用性得到了最廣泛的應用。

2019-08-29 06:50:37

本帖最后由 gk320830 于 2015-3-4 17:23 編輯

求助,有什么方式能夠用FPGA實現虛擬光柵的生成

2014-11-03 23:07:57

求教課題:如何能夠讓電阻管不以熱能方式放出電量而以電流方式放出電量

2013-01-24 23:40:43

我在做fpga與dsp的SRIO通信,我用的是論壇上提供的SRIO test程序,目前dsp端能夠實現端口0的外部回環測試。fpga端的協議還沒做通,我想用dsp直接給fpga發包,fpga根據收到

2018-06-21 10:45:13

前幾天在論壇里看到一個冷笑話,一位媽媽說自己兒子:“你什么都好,就不該是個程序員。” 可是,有些開發者朋友說,程序員中有相當一部分是生活得還不錯的,甚至是高富帥。 所以想問問大家,程序員中究竟有沒有高富帥?更重要的是,程序猿如何能夠升級為糕富帥?本人程序員一枚,請不吝賜教。

2014-11-24 17:00:11

前幾天在論壇里看到一個冷笑話,一位媽媽說自己兒子:“你什么都好,就不該是個程序員。” 可是,有些開發者朋友說,程序員中有相當一部分是生活得還不錯的,甚至是高富帥。 所以想問問大家,程序員中究竟有沒有高富帥?更重要的是,程序猿如何能夠升級為糕富帥?本人程序員一枚,請不吝賜教。

2014-11-24 17:00:42

AD9268官方評估板只提供將采集數據發送到FPGA數據采集板后傳到計算機中。我想使用AD評估板進行數據采集,然后將數據傳輸到自己的FPGA板卡中,自己的FPGA板卡擁有48pin 的歐式連接器連接至FPGA芯片的GPIO引腳。請問想如何能夠實現這種需求的連接。

2018-08-13 06:03:14

Hello,我利用2812的AD對一個200Hz的正弦信號進行采樣,要求每個周期采20個點,然后在Ad的中斷服務子程序中進行處理,雖然經過計算可以設置AD的采樣頻率,但是因為中斷服務子程序的執行時間不好控制,我想問一下,如何能夠保證我的Ad采樣頻率?謝謝!

2018-08-19 07:40:23

需要實現這樣的功能,我有比如說10個IO從CPLD或者FPGA的左邊10個管腳輸入,序號為0到9,期望實現能夠輸出的為任意的序號,比如說我需要輸出對應的序號為1,0,3,2,5,4,7,8,9,6

2023-04-23 14:19:12

在做FX-LMS算法中,Labview如何能夠實時處理。

2018-11-20 17:00:10

請教一下,arduino如何能實現多線程控制 ???

2020-07-27 23:51:55

有一個access數據庫,里面有多張數據表(每個表的字段都是一樣的)。如何能夠把表的名稱讀出來?

2018-04-01 13:12:08

請問射頻433M雙向反饋功能的開關,如何能夠提高反饋信號強度。發射功率足夠,反饋信號強度差。求大神指點。

2016-09-02 11:36:08

。EasyGo FPGA Solver 的優點在于,能夠將Simulink的圖形化模型利用解算器軟件轉化成FPGA執行的代碼,而不需要進行FPGA的編譯

2022-05-19 09:21:43

提出用FPGA 來實現指紋識別算法, 代替了PC 機、通用MCU 或者DSP。算法由硬件來實現, 提高了運算速度。同時具體說明了指紋識別系統的基本原理、系統總體結構、FPGA 模塊劃分, 以及指

2009-07-22 15:17:27 0

0 本文簡述空間對接的基本概念,對空間對接裝置中的通用算法,包括預處理、自動門限和隔點差分的FPGA 實現進行了詳盡的分析,對VHDL 與Verilog HDL 兩種硬件描述語言的區別加

2009-08-19 09:33:07 6

6 在復雜數字邏輯電路設計中,經常會用到多個不同的時鐘信號。介紹一種通用的分頻器,可實現2~256 之間的任意奇數、偶數、半整數分頻。首先簡要介紹了FPGA 器件的特點和應用范

2009-11-01 14:39:19 78

78 FPGA 能夠快速和經濟地將電路描述轉化為硬件實現,而且對設計的修訂也比較方便。而通常的ASIC 需要的設計時間較長,制作費用也較高,也不便于調整。所以本設計是基于FPGA的RS 編

2009-11-30 13:56:35 53

53 本文詳細介紹了一種借助VHDL 硬件描述性語言實現基于FPGA 硬件平臺的通用微處理器設計的完整方案。該型CPU 具有實現簡單快捷、成本低、通用性強、擴展容易的特性。本文分兩

2009-11-30 15:41:28 20

20 本文介紹了一種能夠完成半整數和各種占空比的奇/偶數和的通用的分頻器設計,并給出了本設計在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中實現后的測試數據和設計硬件的測

2009-12-19 16:25:09 65

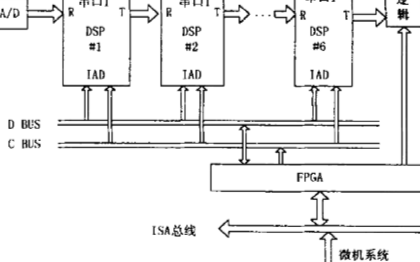

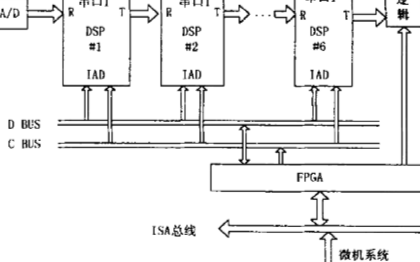

65 設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP進行復雜圖像處理算法和邏輯控制,實現圖像數據的高速傳輸

2010-12-25 17:06:54 60

60 摘 要: 本文通過在QuartursⅡ開發平臺下,一種能夠實現等占空比、非等占空比整數分頻及半整數分頻的通用分頻器的FPGA設計與實現,介紹了利用VHDL硬件描

2009-06-20 12:43:07 562

562

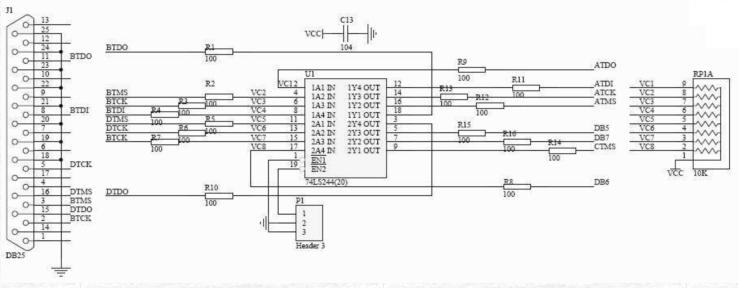

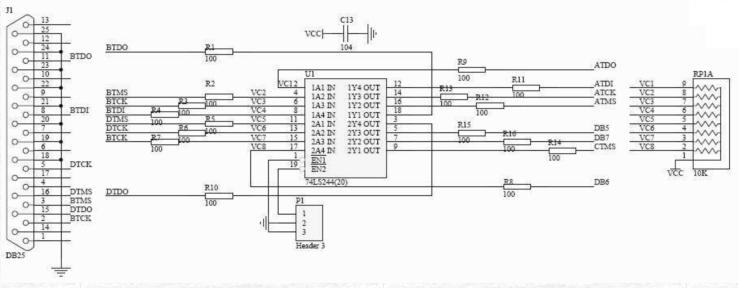

CPLD/FPGAS/51單片機通用的下載電路接法

2009-07-16 10:05:44 2343

2343

基于DSP和FPGA的通用圖像處理平臺設計

摘要:設計一種基于DSP和FPGA架構的通用圖像處理平臺,運用FPGA實現微處理器接口設計,并對圖像數據進行簡單預處理,利用DSP

2010-02-01 11:10:21 1379

1379

本站提供的fpga實現jpeg Verilog源代碼資料,希望能夠幫你的學習。

2011-05-27 15:09:53 200

200 SPI 串行總線是一種常用的標準接口,其使用簡單方便而且占用系統資源少,應用相當廣泛。本文將介紹一種新的通用的SPI 總線的FPGA 實現方法。

2011-09-09 11:58:27 67

67 在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進行了功能驗證. 由于數字時鐘的通用

2011-11-29 16:51:43 178

178 本文在分析現有的解決方案優缺點的基礎上提出了一種在FPGA上實現ORB的改進設計方案,不但為彼此分離的、工作于多處理器平臺上的各個GPP,DSP和FPGA開發小組提供了通用的CORBA通信機制

2011-12-22 10:18:54 3341

3341

基于FPGA的通用高速串行互連協議設計。

2016-05-11 09:46:01 18

18 用 Verilog實現基于FPGA 的通用分頻器的設計時鐘分頻包括奇數和偶數分頻

2016-07-14 11:32:47 45

45 上一篇寫了基于Xilinx FPGA的通用信號發生器的案例,反響比較好,很多朋友和我探討相關的技術,其中就涉及到信號的采集,為了使該文更有血有肉,我在寫一篇基于Xilinx FPGA的通用信號采集器,望能形成呼應,以解答大家的疑問。

2017-02-11 03:11:37 1712

1712

基于FPGA的通用傳感器信號處理系統設計_李輝

2017-03-19 19:07:17 3

3 基于FPGA的通用CNN加速器整體框架如下,通過Caffe/Tensorflow/Mxnet等框架訓練出來的CNN模型,通過編譯器的一系列優化生成模型對應的指令;同時,圖片數據和模型權重數據按照優化規則進行預處理以及壓縮后通過PCIe下發到FPGA加速器中

2017-10-27 14:09:58 9882

9882

不同市場領域的連接需求。全新的 Spartan-7 FPGA 將得到免費 Vivado 設計套件 WebPACK 版本以及 Vivado 設計版本和系統版本的支持,能夠快速集成和實現。

2018-08-20 10:48:00 1464

1464 通用多DSP 目標系統的構成由6片ADSP2181、2片A/D變換器以及實現邏輯功能的FPGA組成,其原理框圖如圖1所示。

2020-03-12 07:55:00 1758

1758

華為的雙品牌為何能夠取得成功?榮耀總裁趙明在接受媒體的采訪中作了解答。

2019-04-28 17:45:39 3085

3085 AI黑科技新品紛紛亮相,智能制造為何能夠脫穎而出?除此之外,SEW還關注柔性生產方向,柔性化生產和物流可以打破傳統流水線的生產作業,實現靈活的內物流。隨著工業4.0的實現,柔性生產將是未來智能化工廠的主流生產方式。而打造智能化工廠還需要基于云數據的物理信息技術升級和智能化工廠平臺的搭建。

2019-07-02 15:46:37 727

727 何能夠讓計算和Memory水乳交融,這個看起來的確是一個一石二鳥的想法。畢竟,作為CPU/GPU以及memory,從本質上大家都是門電路,沒理由不在一起。

2019-07-25 16:59:33 2651

2651

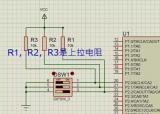

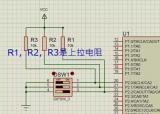

在上拉電阻和下拉電阻的電路中,經常有的疑問是:上拉電阻為何能上拉?下拉電阻為何能下拉?下拉電阻旁邊為何經常會串一個電阻?

2020-04-28 14:17:04 11546

11546

的的UART功能和一些輔助功能時,就可以將需要的UART功能集成用FPGA來實現,然而,FPGA內部并不擁有CPU控制單元,無法處理由UART控制器產生的中斷,所以FPGA不能利用現成的UART控制器

2020-07-10 10:28:51 811

811

應用能夠有更高的性能,您需要熟悉如下介紹的硬件。另外,將會介紹編譯優化選項,有助于將您的 OpenCL 應用更好的實現 RTL 的轉換和映射,并部署到 FPGA 上執行。

2020-07-16 17:58:28 6015

6015

2020中國年會即將召開之際,海爾智家再傳喜訊,海爾智家云云互聯接口協議成為全球首個通過OCF認證的接口協議,這也代表著海爾智家向互聯標準 智啟未來的愿景邁進了堅實的一步。 統一的智慧家庭標準生態,海爾智家緣何能夠主導? 結緣已久 推動智慧家庭標準統一

2020-09-12 09:46:31 1525

1525 討論了Avago Technologies與最新一代的增強帶寬多模光纖配合使用時,如何能夠實現550 m距離的40 Gb / s鏈路。

2021-04-12 16:35:29 2176

2176

給出一個可以通用于Modbus主設備和從設備的協議接口單元,然后基于該接口設計了一個通用的Modbus從設備協處理器。實踐證明該方法能夠滿足工業環境的通訊要求,此外,該方法在其他FPGA上也具有一定通用性和推廣價值。

2021-01-28 17:22:48 32

32 參考電壓分解的通用多電平SVM算法的基礎上,適用于任何電平數目的多電平變流器。采用可編程邏輯門陣列(field-programmable gate array,FPGA)實現所提出的多電平SVM IC

2021-03-10 17:13:47 21

21 UART即通用異步收發器,傳統上采用多功能的專用集成電路實現。但是在一般的使用中往往不需要完整的UART的功能,比如對于多串口的設備或需要加密通訊的場合使用專用集成電路實現的UART就不是最合適

2021-04-27 14:07:25 8

8 本文通過GA3816、FPGA和DSP構建了一個高速、通用、可擴展的多功能信號處理平臺,該信號處理平臺經過動態配置GA3816處理芯片可實現一些信號處理領域常用的運算,也可以通過對DSP、FPGA芯片的編程來實現一些其它算法,所以該平臺能夠廣泛的應用于信號處理等領域。

2021-05-22 15:29:05 1594

1594

電子發燒友網站提供《基于DSP和FPGA的通用控制器設計.pdf》資料免費下載

2023-10-25 10:57:56 0

0 電子發燒友網站提供《基于流水線CORDIC算法通用數字調制器的FPGA實現方案.pdf》資料免費下載

2023-10-27 09:46:19 0

0 數字電路有兩大類:組合電路和時序電路,時序電路即“組合電路+存儲”。所有組合電路都有對應的真值表,FPGA的可編程邏輯塊中的LUT,本質上是一個對應真值表輸出的查找表,可以完成任意組合電路的功能。

2024-02-21 12:33:37 114

114 FPGA(現場可編程門陣列)的通用語言主要是指用于描述FPGA內部邏輯結構和行為的硬件描述語言。目前,Verilog HDL和VHDL是兩種最為廣泛使用的FPGA編程語言。

2024-03-15 14:36:34 87

87

電子發燒友App

電子發燒友App

評論