能力進一步提升開發(fā)效率。同時,SwiftUI也是真正意義上開始通過一套框架,逐步統(tǒng)一Apple生態(tài)中的不同的設(shè)備/OS上的應(yīng)用開發(fā)。

另外,2019年Google將更簡潔的Kotlin語言升級為

2023-05-04 10:48:26

:使用已知的庫(cuBLAS)或框架(Torch with cuDNN)FPGA:使用Quartus Early Beta版本和Power Play圖3:GEMM測試結(jié)果。GEMM是DNN中的關(guān)鍵操作在低

2017-04-27 14:10:12

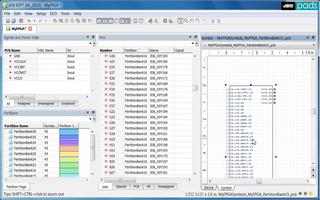

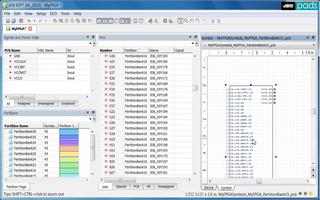

,即將 HDL 合成和先進的 FPGA-PCB I/O 優(yōu)化添加到 PADS Professional 中,便可應(yīng)對這些挑戰(zhàn)。HDL 設(shè)計環(huán)境和 PCB 上物理實施之間的這一接口大大縮短了產(chǎn)品的上市

2018-09-20 11:11:16

FPGA中的I_O時序優(yōu)化設(shè)計在數(shù)字系統(tǒng)的同步接口設(shè)計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優(yōu)化設(shè)計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

FPGA實現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法介紹了利用現(xiàn)場可編程邏輯門陣列FPGA實現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點介紹了DDS技術(shù)在FPGA中的實現(xiàn)

2012-08-11 18:10:11

FPGA的時序優(yōu)化高級研修班通知通過設(shè)立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優(yōu)化的方法。1.FPGA靜態(tài)時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優(yōu)化方法

2013-03-27 15:20:27

了一系列優(yōu)化算法,但是用戶仍有必要遵循一定的編碼風(fēng)格去引導(dǎo) 綜合工具在特定 FPGA 架構(gòu)上達到最優(yōu)結(jié)果。 設(shè)計規(guī)劃用于指導(dǎo)用戶把設(shè)計更好地適配到所選用的 FPGA上并合理地 平衡面積和速度的要求,目的

2022-09-29 06:12:02

EDA技術(shù)具有什么特征?FPGA是什么原理?FPGA設(shè)計應(yīng)用及優(yōu)化策略基于VHDL的FPGA系統(tǒng)行為級設(shè)計

2021-04-15 06:33:58

`FPGA面積優(yōu)化1.對于速度要求不是很高的情況下,我們可以把流水線設(shè)計成迭代的形式,從而重復(fù)利用FPGA功能相同的資源。2.對于控制邏輯小于共享邏輯時,控制邏輯資源可以用來復(fù)用,例如FIR濾波器

2014-12-04 13:52:40

HDMI顯示有幾套流程框架呢?DRM標(biāo)準(zhǔn)HDMI框架是怎樣的?RK HDMI框架又是怎樣的呢?

2022-03-04 07:27:35

實時性在嵌入式開發(fā)中的非常重要,優(yōu)化MCU串口傳輸處理方式可以提高嵌入式系統(tǒng)的實時性。在互聯(lián)網(wǎng)上學(xué)習(xí)并親自實驗(基于STM32單片機)后,我將分兩次介紹優(yōu)化MCU串口收發(fā)數(shù)據(jù)的方法,參考資料將在

2022-02-11 06:18:51

介紹一種一體化儀表優(yōu)化交換式測量示例

2021-05-11 07:01:37

本文介紹一種基于FIFO結(jié)構(gòu)的優(yōu)化端點設(shè)計方案。

2021-05-31 06:31:35

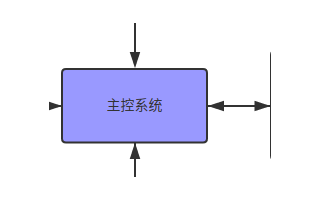

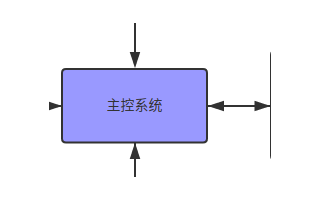

介紹一種嵌入式框架模板的構(gòu)建方案

2022-02-22 06:25:45

1、FPGA開發(fā)板上組合邏輯電路的設(shè)計實現(xiàn)在之前的文章中已經(jīng)介紹過了安路EG4S20 FPGA開發(fā)板以及TD工具的使用,從這篇文章開始,我們將介紹和分享一系列的基礎(chǔ)實例,期望能幫助大家逐步

2022-07-21 15:38:45

上是最優(yōu)的。

簡單易用是指播放框架提供了兩種接口形式:JS和結(jié)合ArkUI提供的UI控件接口,便于開發(fā)者使用。

靈活擴展是指播放框架針對服務(wù)類目的引擎,可增強、可擴展、可替換。

2 、播放框架介紹

2023-01-03 16:36:59

本章提要最優(yōu)化問題廣泛存在于國民經(jīng)濟各部門和工程應(yīng)用各領(lǐng)域中。在所有可能的方案中搜索出最合理的、邊到事先預(yù)定的最優(yōu)目標(biāo)方案(即最優(yōu)方案〉的方法稱為最優(yōu)化方法。本章簡要介紹了優(yōu)化問題的分類及工程背景

2012-03-06 14:53:54

目錄STM32硬件框架介紹IIC初始化STM32硬件框架介紹首先我們來看IIC通信的硬件架構(gòu)可以看出,可以分為以上4部分。第一部分:通信接口SDA信號和SCL信號由此產(chǎn)生或輸入第二部分:時鐘部分

2021-08-24 06:18:53

不方便,計算效率低下而設(shè)計的一個軟件生態(tài)系統(tǒng),用于加速 TI 嵌入式設(shè)備上的深度神經(jīng)網(wǎng)絡(luò)Deep Neural Networks (DNN)計算加速。上一代產(chǎn)品 TDA2/3 系列處理器,集成了計算單元

2022-11-03 06:53:11

《ARM嵌入式Linux系統(tǒng)開發(fā)詳解》第25章USB驅(qū)動開發(fā),本章講解了Linux內(nèi)核USB驅(qū)動體系結(jié)構(gòu)、USB設(shè)備驅(qū)動結(jié)構(gòu)等知識,并在最后給出了兩個USB設(shè)備驅(qū)動開發(fā)實例。本節(jié)為大家介紹USB驅(qū)動程序框架。

2019-07-11 07:38:15

系列文章目錄嵌入式開發(fā)|嵌入式軟件框架《一》常用的軟件框架介紹與選擇文章目錄系列文章目錄前言一、cola os程序框架1.cola_init2.cola_device3.cola_os task任務(wù)

2021-11-08 08:17:44

的發(fā)行版不是很多,比如DKhadoop,可以說是目前國內(nèi)自主做hadoop商業(yè)版比較好的了。下面就以大快搜索DKhadoop為例來給大家介紹一下hadoop框架結(jié)構(gòu)! 圖示:DKhadoop技術(shù)技術(shù)架構(gòu)圖

2018-10-15 15:59:43

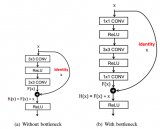

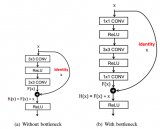

AI等方面。在許多領(lǐng)域中,DNN目前的準(zhǔn)確性已經(jīng)超過人類。與早期的專家手動提取特征或制定規(guī)則不同,DNN的優(yōu)越性能來自于在大量數(shù)據(jù)上使用統(tǒng)計學(xué)習(xí)方法,從原始數(shù)據(jù)中提取高級特征的能力,從而對輸入空間進行

2017-06-14 21:01:14

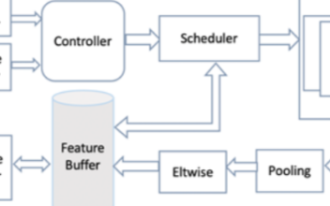

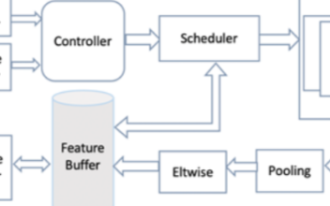

和CPU映射的系統(tǒng)架構(gòu);在FPGA上實現(xiàn)并優(yōu)化的NPU軟核和指令集。下圖展示了使用腦波項目進行DNN加速的完整流程。對于一個訓(xùn)練好的DNN模型,工具會首先將其表示為計算流圖的形式,稱為這個模型的“中間表示

2019-08-11 04:00:00

模塊可以作為任何初學(xué)者進入基于深度學(xué)習(xí)的計算機視覺領(lǐng)域的一個完美起點。OpenCV DNN模塊對于Intel CPU有深度的優(yōu)化,性能不錯,在ARM上的表現(xiàn)就比較一般了。我們使用的人臉檢查模型

2023-01-11 22:06:56

本帖最后由 donatello1996 于 2022-2-22 12:25 編輯

飛凌文檔中有對OpenCV-DNN例程的使用介紹,看著運行效果,我對此產(chǎn)生了濃厚的興趣,想要自己嘗試編譯運行

2022-02-21 00:22:42

一個簡單實用的MCU程序框架(非操作系統(tǒng),簡單調(diào)度任務(wù)) - 總體介紹?單片機程序,總體上可分為跑操作系統(tǒng)的和沒操作系統(tǒng),對于無MMU的小單片機,操作系統(tǒng)通常是UCOS、RTOS等實時操作系統(tǒng)

2022-02-11 06:21:42

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應(yīng)等等,各種不同因素都在迅速推動系統(tǒng)設(shè)計人員關(guān)注節(jié)能問題。一項有關(guān)設(shè)計優(yōu)先考慮事項的最新調(diào)查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。在功耗方面,FPGA帶來了獨特的挑戰(zhàn)。為什么要設(shè)計優(yōu)化FPGA功耗?

2019-08-08 07:39:45

本文闡述了Spartan-3 FPGA針對DSP而優(yōu)化的特性,并通過實現(xiàn)示例分析了它們在性能和成本上的優(yōu)勢。

2019-10-18 07:11:35

FPGA實現(xiàn)。易于適應(yīng)新的神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu)深度學(xué)習(xí)是一個非常活躍的研究領(lǐng)域,每天都在設(shè)計新的 DNN。其中許多結(jié)合了現(xiàn)有的標(biāo)準(zhǔn)計算,但有些需要全新的計算方法。特別是在具有特殊結(jié)構(gòu)的網(wǎng)絡(luò)難以在 GPU 上

2023-02-17 16:56:59

方案如圖4所示。這是一個功能正確的應(yīng)用實現(xiàn)方案,但沒有進行任何性能優(yōu)化或為充分利用FPGA架構(gòu)的功能進行考慮。因此該代碼在SDAccel中編譯完成后,在Alpha Data卡上運行得到的最大吞吐量僅為

2019-06-19 07:27:40

關(guān)注FPGA,那么世界將拋棄你,時代將拋棄你。盡量用硬核,比如硬件乘法器,這個應(yīng)該都知道。結(jié)構(gòu)上的pipeline,簡言之就是“拆",最極端的情形是拆到源和目的Reg間只有基本的組合邏輯門,比如說

2018-06-07 17:55:37

我想知道基于FPGA出租車計價系統(tǒng)實現(xiàn)的技術(shù)框架是什么?

2016-04-26 10:36:46

其在設(shè)計思路和編程風(fēng)格等方面也存在差異,這些差異會對系統(tǒng)綜合后的電路整體性能產(chǎn)生重要的影響。在VHDL語言電路優(yōu)化設(shè)計當(dāng)中,優(yōu)化問題主要包括面積優(yōu)化和速度優(yōu)化。面積優(yōu)化是指CPLD/FPGA的資源

2019-06-18 07:45:03

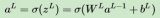

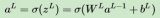

《深度學(xué)習(xí)工程師-吳恩達》02改善深層神經(jīng)網(wǎng)絡(luò)--超參數(shù)優(yōu)化、batch正則化和程序框架 學(xué)習(xí)總結(jié)

2020-06-16 14:52:01

機智云物聯(lián)網(wǎng)開源框架App工程(Eclipse工程)介紹:機智云開源框架(GizOpenSource_AppKit_Android) 是開源的適用于物聯(lián)網(wǎng)的軟件框架,用于無縫的支持設(shè)備到設(shè)備的互聯(lián)

2017-02-15 17:56:40

機智云物聯(lián)網(wǎng)開源框架App工程(Eclipse工程)https://git.oschina.net/dantang/GizOpenSource_AppKit_Android 介紹:機智云開源框架

2016-12-27 15:47:27

CPU優(yōu)化深度學(xué)習(xí)框架和函數(shù)庫機器學(xué)***器

2021-02-22 06:01:02

DNN:關(guān)于神經(jīng)網(wǎng)絡(luò)DNN的知識點總結(jié)(持續(xù)更新)

2018-12-26 10:41:47

FPGA怎么選擇?針對功耗和I/O而優(yōu)化的FPGA介紹

2021-05-06 09:20:34

。 這本書把多年推廣到諸多公司和工程師團隊的經(jīng)驗以及由專門的白皮書和應(yīng)用要點匯集的許多知識進行濃縮,可以用來完善工程師的知識,幫助他們成為高級的fpga設(shè)計者。...高級FPGA設(shè)計 結(jié)構(gòu)、實現(xiàn)和優(yōu)化

2012-03-01 14:59:23

高級FPGA設(shè)計、結(jié)構(gòu)、實現(xiàn)與優(yōu)化(Advanced FPGA Design Architecture, Implementation,and Optimization)

2013-12-10 14:16:25

概述EasyGo FPGA Solver是EasyGo開發(fā)的專門部署在FPGA 硬件上的解算器軟件。根據(jù)不同的應(yīng)用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

針對某航空望遠鏡主結(jié)構(gòu)的重量過高的問題,提出了對航空相機望遠鏡主框架進行拓撲優(yōu)化設(shè)計的方法。基于拓撲優(yōu)化理論,在重力過載的工況下對望遠鏡主框架拓撲優(yōu)化,以整

2010-01-18 12:04:48 19

19 產(chǎn)品概述 Ansys ModelCenter是美國Ansys公司旗下的一款產(chǎn)品,用于賦能工程師創(chuàng)建和自動化多工具工作流,優(yōu)化產(chǎn)品設(shè)計

2024-02-29 14:37:00

本文討論了MELP混合線性碼激勵的FPGA實現(xiàn)的硬件構(gòu)成,介紹了硬件主要組成芯片及MELP編解碼的主要框架,可以用于下一步軟件程序的編制。

2011-12-29 09:38:13 1089

1089

高級FPGA設(shè)計結(jié)構(gòu)、實現(xiàn)和優(yōu)化 作者:(美)克里茲著,孟憲元譯;出版社:機械工程出版社 學(xué)FPGA不一定需要開發(fā)板,自己學(xué)會modelsim仿真、寫testbench,用PC機仿真就能有不少長進。這

2012-11-28 14:03:22 0

0 基于FPGA的SM3算法優(yōu)化設(shè)計與實現(xiàn)的論文

2015-10-29 17:16:51 4

4 高級FPGA設(shè)計 結(jié)構(gòu)、實現(xiàn)和優(yōu)化,適合于FPGA的進階學(xué)習(xí)。

2016-05-11 16:40:55 15

15 高級FPGA設(shè)計 結(jié)構(gòu)、實現(xiàn)和優(yōu)化,適合于學(xué)習(xí)FPGA的進階學(xué)習(xí)。

2016-05-11 16:40:55 14

14 ST MCU選型框架介紹,感興趣可以看看。

2016-07-25 18:52:51 9

9 基于FPGA的可堆疊存儲陣列設(shè)計與優(yōu)化

2017-01-07 21:28:58 0

0 基于FPGA的高速固態(tài)存儲器優(yōu)化設(shè)計_楊玉華

2017-01-13 21:40:36 1

1 SC15大會Alpha Data宣傳的是基于Xilinx Virtex-7 690T FPGA運行Auviz DNN(Auviz公司開發(fā)的在賽靈思 FPGA 上實現(xiàn)卷積神經(jīng)網(wǎng)絡(luò)的函數(shù)庫)算法,并且演示

2017-02-08 18:10:29 563

563

參加 ?FPGA? 功率優(yōu)化班,將幫助您創(chuàng)建更高電源效率的 ?FPGA? 設(shè)計。通過本課程的學(xué)習(xí),將有助于您的設(shè)計滿足更小型化的 ?FPGA? 器件,降低 ?FPGA? 功耗,或在更低的溫度下運行

2017-02-09 06:24:11 167

167 MapReduce框架下的Skyline結(jié)果優(yōu)化算法_馬學(xué)森

2017-03-19 11:41:51 0

0 深度神經(jīng)網(wǎng)絡(luò)(DNN)目前是許多現(xiàn)代AI應(yīng)用的基礎(chǔ)。自從DNN在語音識別和圖像識別任務(wù)中展現(xiàn)出突破性的成果,使用DNN的應(yīng)用數(shù)量呈爆炸式增加。這些DNN方法被大量應(yīng)用在無人駕駛汽車,癌癥檢測,游戲

2018-07-08 06:45:00 21269

21269

本文介紹了基于FPGA的機載視頻圖形顯示系統(tǒng)架構(gòu)的設(shè)計與優(yōu)化,并介紹了三種系統(tǒng)架構(gòu),對系統(tǒng)各組成部分進行了詳細的分析與概述。

2017-10-15 10:19:56 2

2 android框架與應(yīng)用開發(fā)介紹

2017-10-24 09:35:00 7

7 基于FPGA的通用CNN加速器整體框架如下,通過Caffe/Tensorflow/Mxnet等框架訓(xùn)練出來的CNN模型,通過編譯器的一系列優(yōu)化生成模型對應(yīng)的指令;同時,圖片數(shù)據(jù)和模型權(quán)重數(shù)據(jù)按照優(yōu)化規(guī)則進行預(yù)處理以及壓縮后通過PCIe下發(fā)到FPGA加速器中

2017-10-27 14:09:58 9882

9882

資源、速度和功耗是FPGA設(shè)計中的三大關(guān)鍵因素。隨著工藝水平的發(fā)展和系統(tǒng)性能的提升,低功耗成為一些產(chǎn)品的目標(biāo)之一。功耗也隨之受到越來越多的系統(tǒng)工程師和FPGA工程師的關(guān)注。Xilinx新一代開發(fā)工具Vivado針對功耗方面有一套完備的方法和策略,本文將介紹如何利用Vivado進行功耗分析和優(yōu)化。

2017-11-18 03:11:50 4873

4873 谷歌用深度學(xué)習(xí)分析電子病例的重磅論文給出了一個意外的實驗結(jié)果,DNN與邏輯回歸效果一樣,引發(fā)了熱烈討論。

2018-06-28 16:01:33 5747

5747

。機器之心對該論文進行了編譯介紹。 摘要 我們通過 12 種不同類型的圖像劣化(image degradation)方法,比較了人類與當(dāng)前的卷積式深度神經(jīng)網(wǎng)絡(luò)(DNN)在目標(biāo)識別上的穩(wěn)健性。首先,對比三種著名的 DNN(ResNet-152、VGG-19、GoogLeNet),我們發(fā)現(xiàn)

2018-10-19 00:48:01 416

416 可是,設(shè)計一個基于FPGA的高性能DNN推理加速器還是充滿了困難,它需要寄存器傳輸級(RTL)編程技巧,硬件驗證知識和豐富的硬件資源分配經(jīng)驗等硬件設(shè)計相關(guān)知識,對于在算法層面關(guān)注深度學(xué)習(xí)的研究人員來說是非常不友好的。

2018-11-16 10:39:17 5141

5141 在本演示中,來自IBM的Bruce Wile討論了新推出的CAPI SNAP框架,該框架支持FPGA加速。

“SNAP”框架是“存儲,網(wǎng)絡(luò)和分析編程”的縮寫,可以在數(shù)據(jù)流動時加速對數(shù)據(jù)的分析

2018-11-29 06:09:00 2963

2963 高層次的設(shè)計可以讓設(shè)計以更簡潔的方法捕捉,從而讓錯誤更少,調(diào)試更輕松。然而,這種方法最受詬病的是對性能的犧牲。在復(fù)雜的 FPGA 設(shè)計上實現(xiàn)高性能,往往需要手動優(yōu)化 RTL 代碼,這也意味著

2018-12-16 11:19:28 1435

1435

Optuna作為超參數(shù)優(yōu)化框架可以和PFN自己的深度學(xué)習(xí)框架Chainer充分結(jié)合使用。只需要在Chainer中寫接受來自O(shè)ptuna的超參數(shù)的代碼即可。通過這一接口Optuna可以不斷調(diào)用了用戶編寫的模型代碼,神經(jīng)網(wǎng)絡(luò)也可以在你不同的超參數(shù)下得以訓(xùn)練并搜尋較好的結(jié)果。

2018-12-14 09:47:58 2777

2777 FPGA I/O 優(yōu)化功能提供了自動化 FPGA 符號生成流程,該流程與原理圖設(shè)計和 PCB 設(shè)計相集成,可節(jié)省大量創(chuàng)建 PCB 設(shè)計的時間,同時提高原理圖符號的總體質(zhì)量和準(zhǔn)確性。

2019-05-20 06:16:00 2844

2844

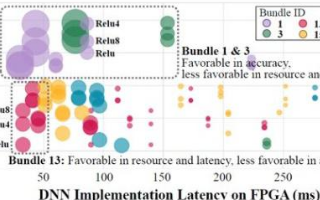

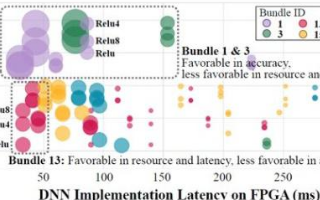

UIUC、IBM 和 Inspirit IoT, Inc(英睿物聯(lián)網(wǎng))的研究人員提出 DNN 和 FPGA 加速器的協(xié)同設(shè)計方案(DNN/FPGA co-design),通過首創(chuàng)的「Auto-DNN

2019-06-10 14:39:30 1041

1041

DNN是去中心化新聞網(wǎng)絡(luò)的簡稱,是一個政治新聞平臺,結(jié)合去中心化網(wǎng)絡(luò)與新聞制作,傳遞社區(qū)制作的最真實有效的內(nèi)容。

當(dāng)今的新聞報道充斥著博人眼球的頭條新聞和錯誤信息,導(dǎo)致虛假新聞和信息不對稱的報道。DNN提供了一個公開世界的藍圖,制作和消費新聞的同時通過激勵保證新聞的準(zhǔn)確性。

2019-08-20 14:26:11 2099

2099 浪潮宣布開源發(fā)布基于FPGA的高效AI計算框架TF2,這一框架的推理引擎采用全球首創(chuàng)的DNN移位計算技術(shù),結(jié)合多項最新優(yōu)化技術(shù),可實現(xiàn)通用深度學(xué)習(xí)模型基于FPGA芯片的高性能低延遲部署。

2019-09-09 14:17:53 932

932 浪潮宣布開源發(fā)布基于FPGA的高效AI計算框架TF2,這一框架的推理引擎采用全球首創(chuàng)的DNN移位計算技術(shù),結(jié)合多項最新優(yōu)化技術(shù),可實現(xiàn)通用深度學(xué)習(xí)模型基于FPGA芯片的高性能低延遲部署,這也是全球首個包含從模型裁剪、壓縮、量化到通用模型實現(xiàn)等優(yōu)化算法的完整方案的FPGA上AI開源框架。

2019-09-23 15:04:56 1799

1799 簡要介紹了遺傳算法的基本原理, 建立了弧形閘門主框架優(yōu)化數(shù)學(xué)模型, 探討了各種尋優(yōu)算法的優(yōu)劣及約束問題的處理方法, 并結(jié)合MAT LAB 語言將遺傳算法應(yīng)用于該主框架優(yōu)化設(shè)計中。結(jié)果表明, 遺傳算法對閘門優(yōu)化設(shè)計是有效的、可行的。

2019-09-23 17:10:00 2

2 在北京舉行的2019人工智能計算大會(AICC2019)上,浪潮宣布開源發(fā)布基于FPGA的高效AI計算框架TF2,這一框架的推理引擎采用全球首創(chuàng)的DNN移位計算技術(shù),結(jié)合多項最新優(yōu)化技術(shù),可實現(xiàn)通用深度學(xué)習(xí)模型基于FPGA芯片的高性能低延遲部署。

2019-12-17 15:22:00 852

852

近日,浪潮宣布為可重構(gòu)AI計算發(fā)展計劃參與者提供最新FPGA加速卡支持。參與該計劃的高校將FPGA開源AI框架TF2應(yīng)用于AI科研或應(yīng)用并取得創(chuàng)新成果,并承諾將優(yōu)化后代碼反饋回TF2開源社區(qū),即可

2020-06-04 09:55:36 812

812

本文檔的主要內(nèi)容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現(xiàn)優(yōu)化設(shè)計。

2021-01-13 17:00:59 25

25 在 深度神經(jīng)網(wǎng)絡(luò)(DNN)模型與前向傳播算法 中,我們對DNN的模型和前向傳播算法做了總結(jié),這里我們更進一步,對DNN的反向傳播算法(Back Propagation,BP)做一個總結(jié)。 1. DNN反向傳播算法要解決的問題

2021-03-22 16:28:22 3110

3110

優(yōu)秀的 Verilog/FPGA開源項目介紹(一)-PCIe通信 今天開始會陸續(xù)介紹一些優(yōu)秀的開源項目,項目基本都是和FPGA或HDL相關(guān)的。對于一些找工作或者急需項目經(jīng)驗的人來說,這些項目都有一定

2021-10-11 15:31:47 8424

8424

例如,經(jīng)過訓(xùn)練以識別狗品種的 DNN 將遍歷給定的圖像并計算圖像中的狗是某個品種的概率。用戶可以查看結(jié)果并選擇網(wǎng)絡(luò)應(yīng)該顯示哪些概率(超過某個閾值等)并返回建議的標(biāo)簽。每個數(shù)學(xué)操作都被認為是一個層,復(fù)雜的 DNN 有很多層,因此被稱為“深度”網(wǎng)絡(luò)。

2022-06-16 09:27:14 928

928 ./oschina_soft/mkl-dnn.zip

2022-06-22 11:17:33 0

0 電子發(fā)燒友網(wǎng)站提供《ThunderGP:基于HLS的FPGA圖形處理框架.zip》資料免費下載

2022-10-27 16:49:59 0

0 本篇文章我們將介紹瑞薩為R-Car V4H提供的三種類型的DNN開發(fā)模擬器,以及它們的使用情況和特點。

2023-02-02 11:06:53 639

639 英特爾 加速器架構(gòu)實驗室的Eriko Nurvit ad hi 博士以 最新 的? GPU ?為參照,對兩代? Intel ? FPGA ?上新興的DNN 算法 進行了評估,認為新興的低精度和稀疏

2023-03-11 13:05:06 403

403 基于提升框架的小波變換方法,利用FPGA 可編程特性可實現(xiàn)多種小波變換。提升框架(LS :Lifting Scheme) 是由Sweldens 等人在近幾年提出的一種小波變換方法,用它的框架結(jié)構(gòu)能有

2023-05-11 15:33:30 456

456

之前的文章介紹了FPGA在線調(diào)試的方法,包括選定抓取信號,防止信號被優(yōu)化的方法等等。

2023-06-20 10:38:48 3333

3333

摘要 在瑞薩提供的R-Car SoC相關(guān)的一些DNN模擬器中,本文將重點介紹 能夠?qū)崿F(xiàn)與實際硬件等價運算的Accurate Simulator ,并說明如何應(yīng)用它來 分析和提高神經(jīng)網(wǎng)絡(luò)的精度

2023-07-13 18:15:04 225

225

深度學(xué)習(xí)cntk框架介紹? 深度學(xué)習(xí)是最近幾年來非常熱門的話題,它正在徹底改變我們生活和工作的方式。隨著越來越多的創(chuàng)新和發(fā)展,人工智能和機器學(xué)習(xí)的應(yīng)用范圍正在大大擴展。而對于深度學(xué)習(xí)這個領(lǐng)域來說

2023-08-17 16:11:23 881

881 電子發(fā)燒友網(wǎng)站提供《FPGA在新興DNN推理領(lǐng)域的應(yīng)用.pdf》資料免費下載

2023-09-15 10:52:53 0

0 電子發(fā)燒友網(wǎng)站提供《新興DNN推理領(lǐng)域的FPGA.pdf》資料免費下載

2023-09-15 10:09:41 0

0 電子發(fā)燒友網(wǎng)站提供《使用賽靈思Alveo加速器卡加速DNN.pdf》資料免費下載

2023-09-18 09:27:24 0

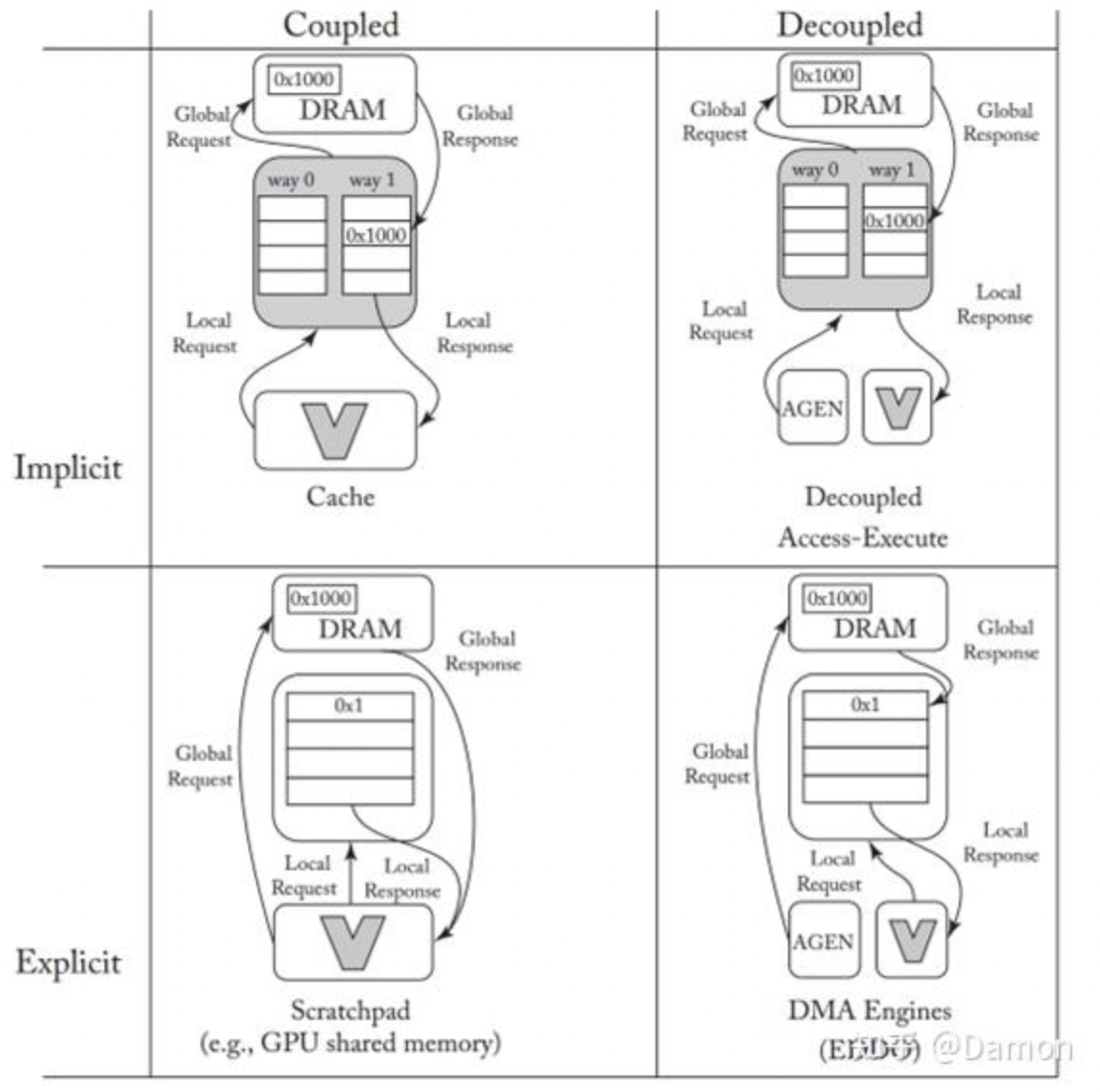

0 如前所述,數(shù)據(jù)緩存是創(chuàng)建高效DNN加速器的關(guān)鍵組件之一。因此,除了選擇適當(dāng)?shù)臄?shù)據(jù)流(控制數(shù)據(jù)緩存的位置和時間)外,DNN加速器還需要一個緩存方案

2023-10-17 17:23:56 772

772

一文看懂FPGA芯片投資框架

2023-01-13 09:06:26 4

4 國產(chǎn)FPGA研究框架

2023-01-13 09:06:57 6

6 電子發(fā)燒友網(wǎng)站提供《基于FPGA的神經(jīng)振蕩器設(shè)計及優(yōu)化.pdf》資料免費下載

2023-11-10 09:39:29 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論