1、E2PROM介紹及其應用現狀

E2PROM(Electically Erasable Programmable Read-Only Memory),即電可擦除只讀存儲器。它是一種非易欠性存儲器,掉電后數據依然存在(一般可保存長達100年),讀寫耗電極低,擦寫時只需相應的電信號即可,控制方式簡單,體積小巧。價格便宜,被廣泛應用于對數據存儲安全性及可靠性要求較高的場合,如各類IC卡、智能家電、工業儀器儀表等。

但E2PROM使用壽命有限,一般為可擦寫100萬次,即某一位由1寫為0或由0寫為1的次數為100萬次。一般的系統往往只對若干同定單元進行頻繁的讀寫,很容易造成這些單元的損壞。而常用的E2PROM存儲系統,只要某一個存儲單元損壞,即使其他絕大部分單元都是完好的,也只能將整個E2PROM芯片報廢。這既是對資源的浪費,也是系統正常運行的潛在風險。

為了延長E2PROM芯片的壽命,提高存儲系統的可靠性,本文提出一種較可靠的E2PROM控制器設計方法,并在FPGA中用VHDL進行了實現。

2、本文E2PROM控制器的工作原理

在很多領域的存儲系統中,可靠性對系統安全至關重要。為了避免系統出錯,并延長系統的壽命,本文在適當犧牲存儲效率的前提下,著重考慮提高存儲系統的可靠性。

E2PROM存儲器存儲單元的損壞主要是由頻繁的寫操作造成的。若要解決問題,首先耍避免對同一單元進行頻繁的擦寫,降低存儲單元損壞的可能;其次當某些單元損壞時,讀寫控制器應該能夠跳過這些損壞的單元,保證系統能繼續正常工作。本文設計的E2PROM控制器具有這兩個方面的功能。

本文的設計思想是,將整個EzpROM地址空間劃分為地址分配表區、備用區和數據區,如圖1所示。

圖1 E2PROM地址空間劃分

在地址分配表區中只存儲所有數據區或備用區存儲單元的地址,初始時與數據區的每個存儲單元一一對應;當某個數據所在的單元損壞時(由于頻繁讀寫的是數據所在的單元,所以首先考慮這種情況),則改用備用區某單元(通過改寫對應的數據分配表單元存儲的地址,使其指向改用的備用區某單元來實現),以后每次讀寫都指向新的存儲單元,這樣就跳過了損壞的單元;若要避免對相同單元頻繁擦寫,則每過一段合適的時間對整個數據分配表進行更新,或對整個E2PROM空間重新劃分;判斷某存儲單元是否損壞的方法是,對該單元進行寫操作之后立刻回讀,若讀寫內容一致則該單元正常,否則已損壞;備用區的首地址存儲該區域未使用部分的開始地址,以方便數據單元損壞時使用該單元,每當有數據單元損壞后使用了該單元,備用區首地址則指向下一單元。

這樣,E2PROM中保存數據區域的損壞單元都能被跳過,只有保存地址的地址分配表和備用區首地址單元的損壞對系統的正常運行有致命的影響。而備用區首地址單元的寫頻率是最高的,保存數據的單元每出現一個損壞單元就要對其改寫一次。因此,理論上當有100萬個單元(1MB)因寫操作損壞時,備用區首地址單元的壽命也即耗盡。但目前較常用的E2PROM芯片的容量最大也就若干MB,如果出現近100萬個損壞單元,芯片早已應該報廢。所以,理論上該方法已足夠可靠。

3、系統總體設計

本文E2PROM存儲芯片選用ATMEL公司的AT24C01,FPGA芯片采用Altera公司的CycIone II系列。

系統的總體框圖如圖1所示。系統主要分為FPGA部分和E2PROM部分。FPGA接受外界控制信號、數據及時鐘等信號,并對E2PROM進行控制。E2PROM根據FPGA的控制信號進行相應的讀寫操作。

AT24C01內部數據單元組織方式為128x8位。將其分為三部分:前48x8位作為地址分配表區,地址范圍0000000~0101111;中間32x8位作為備用區,地址范圍為0110000~1001111;后48x8位為數據區。地址范圍為1010000~1111111。地址空間劃分說明如圖2所示。

本文的E2PROM控制器在FPGA中用VHDL語言進行設計。用有限狀態機技術實現。

圖2系統總體結構

4、AT24C01 E2PROM讀寫控制原理

4.1 I2C總線工作原理

AT24C01采用簡單的雙向兩線串行總線PC總線標準。I2c總線由數據線SDA和時鐘線SCL構成,可發送和接收數據。其數據傳輸過程中共有四種基本類型信號:

(1)開始信號,當SCL為高電平時SDA由高電平向低電平跳變,表明傳送數據開始;

(2)結束信號,當SCL為高電平時SDA由低電平向高電平跳變,表明傳送數據結束;

(3)數據信號。即SDA線上傳輸的數據,當SCL為高電平時有效,不允許改變,當SCL為低電平無效。允許改變;

(4)應答信號,接收端正確接收到8位數據后,向發送端發出特定的低電平脈沖,表示已收到數據。

4.2兩線E2PROM字節讀寫工作原理

兩線E2PROM的寫操作方式分為字節寫和按頁寫。讀操作方式分為字節讀和順序讀。本文僅使用以最基本的讀寫方式——字節寫和字節讀方式為例說明設計過程,其它讀寫方式的設計過程與此相似。

(1)E2PROM的字節寫操作。在控制器對E2PROM發送啟動信號之后,緊接著發送一個8位的寫控制字。控制字的組成包括4位12C特征碼(E2PROM一般為“1010”)、3位芯片地址碼(單片E2PROM為“000”)以及1位讀寫狀態位(讀操作為‘1’,寫操作為‘0’)。 E2PROM正確接收到寫控制字后,發送l位低電平的應答信號。控制器緊接著發送E2PROM存儲單元地址和要寫入的數據。E2PROM每次止確地接收到一個字節的數據都要發送一個應答信號返回給控制器。隨后控制器發送停止信號,對E2PROM寫一個字節的操作完成。

(2)E2PROM的字節讀操作。E2PROM的讀操作包括寫地址和讀數據兩個階段。控制器首先發送一個啟動信號和8位的寫控制字節(讀些狀態位R/W=‘0’),E2PROM正確接收到控制字后發送1位低電平的應答信號,之后控制器發送8位的E2PROM地址。通過寫操作設置E2PROM存儲單元地址。接著控制器再發送一個啟動信號和讀控制字節(此時R/W=‘1’),啟動讀操作,E2PROM收到信息后發送1位的低電平應答信號,然后將指定單元的數據發送到SDA線上,控制器正確收到數據后返回一個低電平的應答信號給E2PROM,隨后發送停止信號,字節讀操作結束。

5、可靠性E2PROM控制器設計

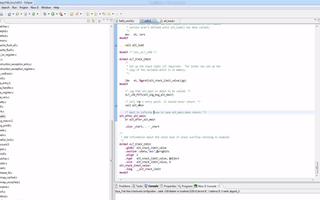

本文用VHDL語言,以有限狀態機的方式在實現FPGA對E2PROM的控制。對于一般的讀寫過程,只需要7個基本狀態便可實現,即:空閑,開始。寫控制字,寫地址,寫數據,讀數據,停止。

但由于本文的讀寫過程較為復雜,雖然基本的狀態仍為這7個,但如果僅用這7種狀態,會使得程序流程異常繁雜。考慮到每次讀寫中都首先要從地址分配表中讀出數據地址,然后才在數據地址讀寫數據,這兩個階段雖然過程相近,但狀態轉換條件不同,將它們分離開來能使狀態轉換和程序流程更清晰。所以本系統對這兩個階段的狀態分開實現,用14個狀態實現整個讀寫過程,即:S0空閑,S1開始,S2控制字(寫操作)。s3寫地址,s4開始,S5控制字(讀操作),S6讀數據(從地址分配表中讀取數據地址),S7結束(查表結束,此后為數據讀寫過程),S8開始,S9寫控制字,S10寫地址,Sll寫數據,S12讀數據,S13停止。其中Sl到S7為查地址分配表的過程.S8到S13為進行數據讀寫的過程。整個過程的狀態轉換過程如圖3所示。

本文設計的E2PROM采用的方法需要首先對E2PROM芯片進行格式化,即對整個E2PROM存儲空間進行劃分,建立地址分配表。這個過程為基本寫操作的循環,可以嵌入系統讀寫過程中。

因此,整個系統共有3個主要進程:時鐘產生進程,狀態轉換進程和狀態控制進程。

1、時鐘產生進程,負責產生滿足系統所需的各種時鐘,主要是E2PROM的SCL,并且為了方便方便按照時鐘要求讀寫數據,將SCL周期內劃分為4個子周期。工作在1.8V、2.5V和2.7v時,E2PROM的工作頻率為100KHz。本文采用100M的外

部晶振產生外部時鐘clk,則需進行1000分頻來產生E2PROM所需的SCL時鐘信號。該進程如下:

CLK_GEN:PROCESS(clk)

BEGIN

IF clk’EVENT AND clk=’1’THEN

IF ncount=499 THEN

ncount《=0;sclsig《=NOT sclsig;

ELSE ncount《=ncount+l;

END IF:

END IF;

sel《=selsig;

END PROCESS;

2、狀態轉換進程,負責在適當的時機將狀態機轉入下一狀態,代碼如下:

STATE_TRANS:PROCESS(sclsig)

BEGIN

IF sclsig’EVENT AND sclsig=’0’THEN

curstate《=nextstate;

END IF;

END PROCESS

3、狀態控制進程,負責在格式化及讀寫過程中各種信號的設置,這是整個系統最復雜也是最核心的部分,其本質就是系統狀態轉換圖的VHDL代碼實現。但其過程相當繁瑣,在這里只能將這個進程代碼的主要部分展示出來,然后對各狀態的具體操作進行適當的說明。

本進程的主要代碼如下:

STATE_CTR:PROCESS(clk)

BEGIN

IF clk’EVENT AND clk=’1’THEN

CASE curstate IS

WHEN S0=》

IF rwf/=“00”

THEN nextstate《=S1;

END IF;

。..。..

WHEN S13=》

IF sclsig=O AND ncount=499

THEN sda《=’0’:

ELSIF sclsig=1 AND nclk=124

THEN sda《=’1’;nextstate《=sO;

END IF;

END CASE;

END IF;

END PROCESS;

圖3系統狀態轉換圖

對各狀態的說明如下:

S0:空閑狀態,檢測rwf信號輸入。如果為格式化命令(“ll”)則轉入S8,如果為讀操作或寫操作命令(分別為“0l”和“10”)則轉入S1。

S1:產生開始信號。完成后轉入入S2。

S2:向SDA線輸出寫操作控制字。完成后轉入S3。

S3:寫地址(由外部輸入)。即所需操作的數據單元對應在地址分配表中的地址。完成后轉入S4。

S4:產生開始信號。完成后轉入S5。

S5:向SDA線讀操作控制字。完成后轉入S6。

S6:讀取數據,此處為所需數據所在的地址。完成后轉入s7。

S7:產生結束信號。完成后轉入S8。至此查表過程結束,此后為實際讀寫過程。

s8:產生開始信號。完成后轉入S9。

S9:輸出控制字。如果在讀操作過程中且為第二次進入該狀態,則向SDA線輸出讀操作控制字,完成后轉入S12;否則輸出寫操作控制字,完成后轉入S1O。

S1O:寫地址(即S6狀態中讀取的數據)。完成后,如果為讀操作則轉入S11,否則轉入S8。

S11:寫數據,向SDA線寫外部提供的數據。完成后轉入S13。

S12:讀數據,完成后轉入S13。

S13:產生結束信號。如果處于讀操作結束狀態,則轉入SO;如果處于寫操作結束狀態并且沒有對數據回讀以檢查所寫單元是否正常。則轉入S6進行回讀;如果處于寫操作回讀結束狀態,無誤則轉入S0,有誤則轉入S1讀備用區首地址;如果是對備用區寫操作回讀有誤,則地址加l后進入S6寫下一地址,直至能正確寫入,之后將地址加1寫入備用區首地址.然后轉入S0;如果處于格式化過程中,則地址加1后轉入S8,直到格式化結束轉入S0。

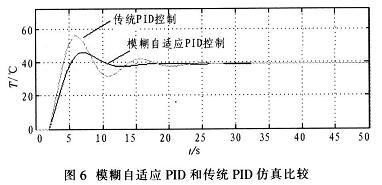

6 、仿真結果和結論

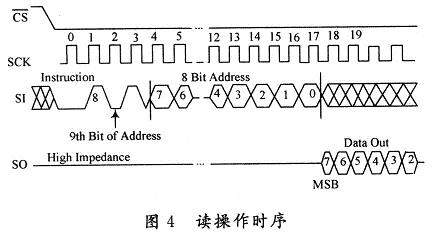

圖4寫操作功能仿真的部分波形

圖5讀操作功能仿真的部分波形

在Quartos II軟件中對本文設計的E2PROM控制器進行了功能仿真。寫操作和讀操作功能仿真的部分波形如圖4和圖5所示。根據仿真波形可知,其結果與預期基本一致。在工程中的成功應用也證明了本設計的正確性。

本文作者創新點:對E2PROM存儲空間進行適當的劃分,以類似指針的方式進行讀寫操作,減少了系統對特定存儲單元的依賴,提高了系統的可靠性。

責任編輯:gt

電子發燒友App

電子發燒友App

評論