28335主要應(yīng)用在哪些場合?目前應(yīng)用成熟嗎?

2018-06-07 04:14:35

兼顧速度及靈活性。高層運(yùn)算的特點(diǎn)是所處理的數(shù)據(jù)量較底層少,但算法結(jié)構(gòu)復(fù)雜,適宜采用運(yùn)算速度高、尋址方式靈活、通信能力強(qiáng)的DSP 芯片來實(shí)現(xiàn)。DSP+FPGA 結(jié)構(gòu)最大的特點(diǎn)是結(jié)構(gòu)靈活,有較強(qiáng)的通用性

2018-12-06 10:05:49

綜合實(shí)驗(yàn) 基于FPGA的視頻增強(qiáng)算法與實(shí)現(xiàn) 介紹具體的算法,針對項(xiàng)目做出一定介紹,包括算法原理,所實(shí)現(xiàn)的功能,體系結(jié)構(gòu),及設(shè)計(jì)結(jié)果的分析,調(diào)試和驗(yàn)證等;進(jìn)一步鞏固和加強(qiáng)對視頻

2009-07-16 14:05:25

有限的場合2.FPGA相比其他MCU,他的競爭力在于并行處理和可定制性,這也是為什么FPGA的主要應(yīng)用場合在通信和驗(yàn)證領(lǐng)域,SOC功能對于FPGA來說能提升開發(fā)速度,降低在算法實(shí)現(xiàn)上的復(fù)雜度,填補(bǔ)一定的市場

2015-01-06 17:22:57

中心點(diǎn)畫圓和Bresenham畫圓,哪種算法速度更快?

2023-10-28 08:04:32

什么是巡線?巡線為何如此重要?光感中心與小車轉(zhuǎn)向中心有什么關(guān)系?

2021-07-13 07:25:19

matlab圖像處理中光條中心提取的程序代碼怎么寫?

2012-05-10 12:09:43

請教高手:寫FPGA代碼時(shí),是先自己畫出電路原理圖或框圖、或流程圖,再對照電路框圖寫代碼;還是不需此過程,直接寫代碼。看好多論文都是研究某算法實(shí)現(xiàn)的VLSI結(jié)構(gòu),故個(gè)人認(rèn)為通常應(yīng)先有電路框圖及結(jié)構(gòu),再寫verilog,不知對不對?

2013-05-14 21:04:38

AD7400的時(shí)鐘是10MHZ,處理器是TI的28335時(shí)鐘是150MHZ,AD7400的采樣范圍要和同步信號中心線對齊,AD7400的時(shí)鐘和同步信號時(shí)鐘怎么設(shè)置。

2023-12-11 08:13:29

Dear,AD7400的時(shí)鐘是10MHZ,處理器是TI的28335時(shí)鐘是150MHZ,AD7400的采樣范圍要和同步信號中心線對齊,AD7400的時(shí)鐘和同步信號時(shí)鐘怎么設(shè)置。

2018-08-02 09:01:30

`在工程圖中用戶希望標(biāo)記為對稱的兩條現(xiàn)有的直線之間創(chuàng)建中心線,中心線的長度是按照用戶首先選擇的直線長度來生成的。下面我們就來介紹一下CAD直線間中心線的具體操作教程。1、 首先,打開浩辰CAD機(jī)械

2021-01-11 13:39:16

FPGA實(shí)現(xiàn)的 FFT 處理器的硬件結(jié)構(gòu)。接收單元采用乒乓RAM 結(jié)構(gòu), 擴(kuò)大了數(shù)據(jù)吞吐量。中間數(shù)據(jù)緩存單元采用雙口RAM , 減少了訪問RAM 的時(shí)鐘消耗。計(jì)算單元采用基 2 算法, 流水線結(jié)構(gòu), 可在

2017-11-21 15:55:13

在信號處理中,FFT占有很重要的位置,其運(yùn)算時(shí)間影響整個(gè)系統(tǒng)的性能。傳統(tǒng)的實(shí)現(xiàn)方法速度很慢,難以滿足信號處理的實(shí)時(shí)性要求。針對這個(gè)問題,本文研究了基于FPGA芯片的FFT算法,把FFT算法對實(shí)時(shí)性

2010-05-28 13:38:38

,它的局限性也逐漸暴露出來.在很多計(jì)算機(jī)信息安全系統(tǒng)中,硬件加密手段被應(yīng)用到設(shè)備中來提高密碼運(yùn)算速度和系統(tǒng)的安全性. 給出了一種RC4加密算法的FPGA實(shí)現(xiàn)方案,相比用軟件實(shí)現(xiàn),該方案速度更快,安全性更高

2012-08-11 11:48:18

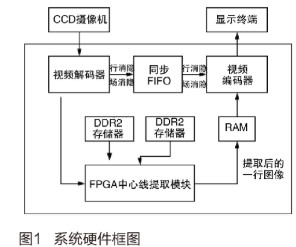

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過程。實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于用

2019-07-01 07:38:06

摘要為有效提高視頻監(jiān)控應(yīng)用領(lǐng)域中多屏幕畫面顯示的清晰度、分辨度等問題,提出了一種基于FPGA的實(shí)時(shí)視頻圖像處理算法。文中介紹了系統(tǒng)的整體結(jié)構(gòu),然后針對FPGA模塊介紹了視頻圖像的緩存及圖像分割,并

2019-06-28 07:06:54

三相不對稱負(fù)載星型連接有無中心線對電路工作是否有影響?若有影響是什么影響?

2023-03-23 09:55:20

為什么高斯濾波廣泛的應(yīng)用在圖像處理中

2023-10-09 06:31:45

什么是光模塊?光模塊又有著哪些類型和參數(shù)?光模塊又應(yīng)用在哪些領(lǐng)域呢?

2021-05-18 06:10:08

; 1310nm和1550nm波段:多用于中長距離傳輸; 看到這里,你知道光模塊是怎樣的一回事了吧。那么,光模塊這么精細(xì)小件的東西,它是應(yīng)用在什么地方的呢?【光模塊應(yīng)用】光模塊廣泛運(yùn)用于交換機(jī),路由器,服務(wù)器網(wǎng)卡

2017-11-01 13:36:50

什么是CWDM光模塊?CWDM光模塊有哪些封裝方式?CWDM光模塊應(yīng)用在什么地方?

2021-05-18 06:46:07

低歐姆測試主要應(yīng)用在哪些行業(yè)?3706型主機(jī)特性及益處是什么?

2021-05-11 06:20:39

,具有以下特點(diǎn):體積小,功耗低;無機(jī)械運(yùn)動,使用時(shí)間長;IP68防水等級,防水性高;支持個(gè)性化機(jī)型定制。光電液位傳感器如何應(yīng)用在加濕器?主要是通過內(nèi)置安裝光電液位傳感器,光電液位傳感器內(nèi)置紅外發(fā)射管

2023-02-23 09:40:22

`網(wǎng)絡(luò)在我們生活中是越發(fā)的重要,然而網(wǎng)絡(luò)大家只知道只要將網(wǎng)線插入電腦或者路由器,電腦即可上網(wǎng),只知道光纖上網(wǎng)速度之快,但是您知道光纖跳線的作用和光纖跳線可以應(yīng)用在哪些場景中嗎?首先,我們先來了解一下

2017-08-18 14:53:49

的周期來處理其他算法。此外,FPGA 結(jié)構(gòu)還可以具有多時(shí)鐘域,從而允許選擇性硬件模塊根據(jù)各自的計(jì)算要求使用獨(dú)立的時(shí)鐘速度。理論上質(zhì)量的最優(yōu)性。當(dāng)且僅當(dāng)對復(fù)雜度沒有限制時(shí),任何基于速率失真曲線的理論最優(yōu)

2008-06-25 11:33:26

的提升。運(yùn)算速度或者數(shù)據(jù)路徑寬度都可以進(jìn)一步提高,另外,時(shí)序操作可以在結(jié)構(gòu)上增加一些并行度。這些措施中,每一種都可以提高一定的性能。在利用了目標(biāo)FPGA器件靈活性的結(jié)構(gòu)中實(shí)現(xiàn)算法,會獲得比較大的好處

2021-12-15 06:30:00

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過程。 實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-28 08:10:26

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過程。 實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-19 06:12:05

以降低系統(tǒng)速度為代價(jià)。從FPGA發(fā)展趨勢和DSP運(yùn)算要求看,系統(tǒng)速度指標(biāo)的意義比面積指標(biāo)更趨重要,需要我們進(jìn)一步深入研究提高芯片的最高工作速度的設(shè)計(jì)策略。我們需要討論一下基于FPGA的DSP系統(tǒng)設(shè)計(jì)中的流水線技術(shù)主要應(yīng)用在哪些方面?

2019-08-02 06:03:48

本文介紹了如何在FPGA 中利用Block RAM 的特殊結(jié)構(gòu)實(shí)現(xiàn)HDTV 視頻增強(qiáng)算法中灰度直方圖統(tǒng)計(jì)。灰度直方圖統(tǒng)計(jì)灰度直方圖統(tǒng)計(jì)是圖像處理過程中很常用的一個(gè)步驟,簡單來講,就是對一幅圖像各個(gè)

2012-05-14 12:37:37

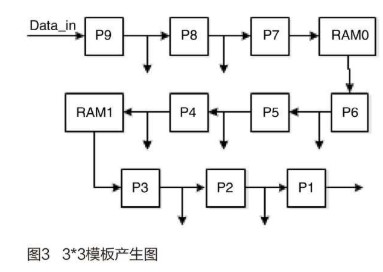

’。3 FPGA二值圖像邊界提取算法實(shí)現(xiàn)圖2 二值圖像膨脹FPGA模塊架構(gòu)圖2中我們使用串口傳圖傳入的是二值圖像。FPGA源碼:/*Module name

2018-08-10 09:21:35

:https://pan.baidu.com/s/1M7PLzRs-yMJv7NFJE8GVAw 提取碼:qr0t 1系統(tǒng)概述如圖所示,這是整個(gè)視頻采集系統(tǒng)的原理框圖。上電初始,FPGA需要通過IIC接口

2019-07-10 09:12:31

VGA顯示屏上,前面我們把硬件平臺已經(jīng)搭建完成了,后面我們將利用這個(gè)硬件基礎(chǔ)平臺上來實(shí)現(xiàn)基于FPGA的一系列圖像處理基礎(chǔ)算法。椒鹽噪聲(salt &pepper noise)是數(shù)字圖像的一

2017-08-28 11:34:10

基于FPGA的多路回聲消除算法的實(shí)現(xiàn)中文期刊文章作 者:尹邦政 朱靜 毛茅作者機(jī)構(gòu):[1]廣州廣哈通信股份有限公司,廣東廣州510663;[2]廣州大學(xué)實(shí)驗(yàn)中心,廣東廣州510006出 版 物

2018-05-08 10:23:36

`大家好,給大家介紹一下,這是基于FPGA的膚色識別算法實(shí)現(xiàn)。我們今天這篇文章有兩個(gè)內(nèi)容一是實(shí)現(xiàn)基于FPGA的彩色圖片轉(zhuǎn)灰度實(shí)現(xiàn),然后在這個(gè)基礎(chǔ)上實(shí)現(xiàn)基于FPGA的膚色檢測算法實(shí)現(xiàn)。將彩色圖像轉(zhuǎn)化

2017-10-28 08:48:57

本篇文章我要寫的是基于的腐蝕膨脹算法實(shí)現(xiàn),腐蝕膨脹是形態(tài)學(xué)圖像處理的基礎(chǔ),,腐蝕在二值圖像的基礎(chǔ)上做“收縮”或“細(xì)化”操作,膨脹在二值圖像的基礎(chǔ)上做“加長”或“變粗”的操作。那么什么是二值圖像呢?把

2017-09-22 13:20:55

數(shù)據(jù)速度,實(shí)現(xiàn)圖像的邊緣檢測。從機(jī)接口一般通過嵌入式軟件讀寫寄存器來完成。1 邊緣檢測和Sobel算法 邊緣檢測是分析視頻和圖像的重要方法,主要檢測和確定圖像在哪些區(qū)域上亮度發(fā)生突變,這些亮度突變的區(qū)域

2017-11-29 08:57:04

電視圖像或紅外兩個(gè)波段,實(shí)現(xiàn)圖像跟蹤各項(xiàng)功能。本文提出的跟蹤算法與設(shè)計(jì)的跟蹤裝置可在一定程度上解決視頻跟蹤精度低、處理速度慢的問題,同時(shí)本視頻跟蹤裝置也可作為進(jìn)一步研究圖像處理與跟蹤控制的平臺。

2019-06-26 06:09:46

模塊,而且總體上結(jié)構(gòu)更為簡單。此CORDIC算法還采用流水線結(jié)構(gòu)提高了運(yùn)算的速度,從當(dāng)前VLSI的發(fā)展趨勢上來看,芯片內(nèi)的門資源相對富裕,對流水線CORDIC的實(shí)現(xiàn)規(guī)模約束很小。此外,流水線CORDIC

2011-07-11 21:32:29

本文介紹了如何在FPGA中利用Block RAM的特殊結(jié)構(gòu)實(shí)現(xiàn)HDTV視頻增強(qiáng)算法中灰度直方圖統(tǒng)計(jì)。

2021-04-30 07:34:58

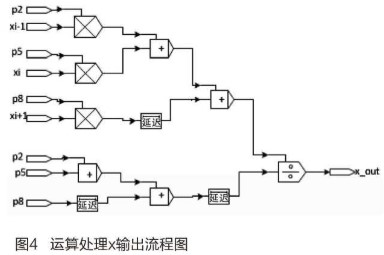

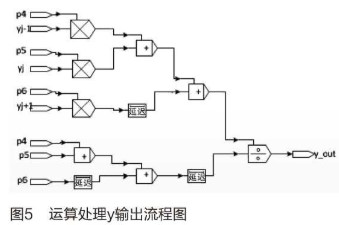

能夠充分利用有限位長。這樣處理比定點(diǎn)方法擴(kuò)大了動態(tài)范圍,并且提高了精度,比浮點(diǎn)運(yùn)算在速度上有了提高。塊浮點(diǎn)結(jié)構(gòu)如圖4所示。3 結(jié) 語著重討論基于FPGA的64點(diǎn)高速FFT算法的實(shí)現(xiàn)方法。采用高基數(shù)結(jié)構(gòu)和流水線

2019-06-17 09:01:35

如何把W25Q16模塊應(yīng)用在TM4C1294上?

2022-02-17 07:20:54

基于線性預(yù)測的FIR自適應(yīng)語音濾波器的系統(tǒng)結(jié)構(gòu)由那幾部分組成?如何降低LMS算法的計(jì)算復(fù)雜度,加快程序在DSP上運(yùn)行的速度,實(shí)現(xiàn)DSP?

2021-04-12 06:27:49

截短Reed-Solomon碼譯碼器的FPGA實(shí)現(xiàn)提出了一種改進(jìn)的BM算法,并在此基礎(chǔ)上提出了一種大量采用并行結(jié)構(gòu)的截短RS碼譯碼器的實(shí)現(xiàn)方式。驗(yàn)證表明,該算法能顯著提高基于FPGA的RS譯碼器

2009-09-19 09:39:43

空域?yàn)V波算法是圖像增強(qiáng)技術(shù)的一種,直接對圖像的象素進(jìn)行處理,不需要進(jìn)行變換。常見的濾波算子如銳化算子、高通算子、平滑算子等,可以完成圖像的邊緣提取、噪聲去除等處理。這些濾波算子盡管功能不同,實(shí)現(xiàn)

2011-02-24 14:20:18

數(shù)字式加速度傳感器是怎樣應(yīng)用在車載導(dǎo)航系統(tǒng)中的?

2021-05-13 06:27:27

設(shè)計(jì)可提高監(jiān)控效率的同時(shí)有效解決校園安防中人員復(fù)雜、流動大,監(jiān)控面積大、監(jiān)控點(diǎn)多與管理人員不足的矛盾。 智能一體化監(jiān)控平臺可對從前端接收的視頻進(jìn)行智能分析,并在此基礎(chǔ)上實(shí)現(xiàn)各種應(yīng)用,例如,對校

2015-03-23 10:29:02

求助大神,在FPGA上實(shí)現(xiàn)retinex算法 。。。

2013-05-08 23:29:41

本帖最后由 upup11 于 2012-11-21 20:45 編輯

我想請教一個(gè)問題:如何用FPGA硬件實(shí)現(xiàn)小波變換。 問題的由來:我在做一個(gè)不影響語音通信的前提下,電話線感應(yīng)信號特征提取

2012-11-20 21:35:16

用FPGA實(shí)現(xiàn)優(yōu)化的指紋識別預(yù)處理算法在選取較優(yōu)化的指紋識別預(yù)處理算法的基礎(chǔ)上,根據(jù)算法的結(jié)構(gòu)選取具有并行處理、低功耗、速度快等特點(diǎn)的FPGA作為實(shí)現(xiàn)算法的基本器件。由于用FPGA實(shí)現(xiàn)復(fù)雜算法較傳統(tǒng)

2009-09-19 09:38:11

本文推導(dǎo)出一種適合在FPGA上實(shí)現(xiàn)從RGB到Y(jié)CbCr。顏色空間變換的新算法,采用單片FPGA完成電路設(shè)計(jì),利用FPGA內(nèi)嵌DSP核實(shí)現(xiàn)乘法運(yùn)算,提高了轉(zhuǎn)換算法的運(yùn)行速度。

2021-04-29 06:57:57

提出用FPGA 來實(shí)現(xiàn)指紋識別算法, 代替了PC 機(jī)、通用MCU 或者DSP。算法由硬件來實(shí)現(xiàn), 提高了運(yùn)算速度。同時(shí)具體說明了指紋識別系統(tǒng)的基本原理、系統(tǒng)總體結(jié)構(gòu)、FPGA 模塊劃分, 以及指

2009-07-22 15:17:27 0

0 本文討論了一種可在FPGA 上實(shí)現(xiàn)的FFT 結(jié)構(gòu)。該結(jié)構(gòu)采用基于流水線結(jié)構(gòu)和快速并行乘法器的蝶形處理器。乘法器采用改進(jìn)的Booth 算法,簡化了部分積符號擴(kuò)展,使用Wallace 樹結(jié)構(gòu)和4-2

2009-09-11 15:46:40 16

16 介紹AES 算法的原理以及基于FPGA 的高速實(shí)現(xiàn)。結(jié)合算法和FPGA 的特點(diǎn),采用查表法優(yōu)化處理了字節(jié)代換運(yùn)算、列混合運(yùn)算。同時(shí),為了提高系統(tǒng)工作速度,在設(shè)計(jì)中應(yīng)用了內(nèi)外結(jié)合

2010-01-25 14:26:51 29

29 提出了基于microblaze軟核處理器的SOPC技術(shù)來進(jìn)行焊縫結(jié)構(gòu)光圖像處理與特征提取;由圖像預(yù)處理模塊實(shí)現(xiàn)對焊縫圖像濾波、二值化、數(shù)學(xué)形態(tài)學(xué)處理、邊緣檢測、中心線提取等步驟的

2010-02-24 14:48:42 14

14 介紹AES算法的原理以及基于FPGA的高速實(shí)現(xiàn)。結(jié)合算法和FPGA的特點(diǎn),采用查表法優(yōu)化處理了字節(jié)代換運(yùn)算、列混合運(yùn)算。同時(shí),為了提高系統(tǒng)工作速度,在設(shè)計(jì)中應(yīng)用了內(nèi)外結(jié)合的流水線

2010-07-17 18:09:43 44

44 將FPGA應(yīng)用在數(shù)字信號處理的主流技術(shù)DSP中是Altera推廣的重要應(yīng)用之一,本文依據(jù)Altera提出的基于FPGA的DSP解決方案,按照面向系統(tǒng)級和算法級的硬件設(shè)計(jì)思路,為語音信號處理領(lǐng)域中

2010-08-06 16:19:08 15

15 使用AUTOCAD自動繪制出中心線

AutoCAD是目前國內(nèi)應(yīng)用最廣范的CAD系統(tǒng)之一,AutoCAD 功能強(qiáng)大,是一個(gè)通用的CAD平臺,但是如果不根據(jù)本專業(yè)的需要進(jìn)行二次

2009-02-14 17:12:05 5351

5351 雷達(dá)視頻積累算法在FPGA上的實(shí)現(xiàn)

1 引 言

由于雷達(dá)所處的環(huán)境的復(fù)雜性,除了地物、云雨、鳥群等干擾外,還可能來自臨近的雷達(dá)異步干擾、電臺干擾等。所有的

2009-11-09 16:08:23 675

675

該文介紹了兩種Viterbi 譯碼器回溯譯碼算法,通過對這兩種算法硬件實(shí)現(xiàn)結(jié)構(gòu)上的優(yōu)化,給出了這兩種算法的FPGA 實(shí)現(xiàn)方法,比較了兩種實(shí)現(xiàn)方法的優(yōu)缺點(diǎn)。最后將其應(yīng)用在實(shí)際的Viter

2011-05-28 15:18:48 33

33 Xilinx FPGA工程例子源碼:在FPGA上實(shí)現(xiàn)CRC算法的程序

2016-06-07 15:07:45 28

28 三維掃描圖像光帶中心線提取的FPGA實(shí)現(xiàn),下來看看

2016-09-17 07:29:56 17

17 基于裂縫中心線方向的土遺址裂縫寬度計(jì)算方法_龍雨

2017-03-22 09:13:17 0

0 算法進(jìn)行深入研究,面向Xilinx K7 410T FPGA 芯片設(shè)計(jì)SHA-1算法實(shí)現(xiàn)結(jié)構(gòu),完成SHA-1算法編程,進(jìn)行測試和后續(xù)應(yīng)用。該算法在FPGA 上實(shí)現(xiàn),可以實(shí)現(xiàn)3.2G bit/s的吞吐

2017-10-30 16:25:54 4

4 傳統(tǒng)的插值算法在視頻圖像縮放尤其是輸出高分辨率的視頻圖像時(shí),對細(xì)節(jié)方面的處理性能較差。采用多相位插值算法實(shí)現(xiàn)視頻圖像縮放,主要闡述算法的原理及算法實(shí)現(xiàn)的硬件結(jié)構(gòu)。其中硬件電路控制部分使用Xilinx

2017-11-16 11:48:09 4559

4559

為解決實(shí)際測量中求光條中心速度慢的問題,提出一種基于閾值法和Hessian矩陣的改進(jìn)算法。首先,使用均值濾波以削弱圖像噪聲,并通過設(shè)定閾值來找出光條中心粗略位置,而后利用高斯函數(shù)的可分離性和對稱性

2017-11-16 15:54:33 8

8 在線結(jié)構(gòu)光三維測量系統(tǒng)中,結(jié)構(gòu)光中心提取的速度和精度直接影響到系統(tǒng)的整體性能。基于幾何中心法、方向模板法和灰度重心法,提出了一種快速提取結(jié)構(gòu)光中心的算法。首先,先對圖像進(jìn)行預(yù)處理,通過幾何中心法快速

2017-12-26 18:43:57 0

0 在復(fù)雜場景下的視頻運(yùn)動目標(biāo)提取是視頻分析技術(shù)的首要工作。為了解決前景運(yùn)動目標(biāo)提取的精確度不高的問題,提出一種基于視覺背景提取( ViBE)的改進(jìn)視頻運(yùn)動目標(biāo)提取算法(ViBE+)。首先,在背景模型

2018-01-08 11:40:58 2

2 本文主要介紹了一種基于FPGA+DSP的視頻控制的智能交通燈設(shè)計(jì)。該交通燈由視頻采集、圖像處理和控制模塊組成,使用FPGA核心搭建專用高速視頻采集模塊,使用DSP處理器進(jìn)行實(shí)時(shí)圖像運(yùn)算,通過圖像算法提取車流量信息,最終結(jié)合模糊算法實(shí)現(xiàn)智能控制。

2018-01-09 14:15:41 1853

1853

本文介紹了如何在FPGA 中利用Block RAM 的特殊結(jié)構(gòu)實(shí)現(xiàn)HDTV視頻增強(qiáng)算法中灰度直方圖統(tǒng)計(jì)。

2019-07-10 08:10:00 2578

2578 圖像預(yù)處理結(jié)構(gòu),該結(jié)構(gòu)具有良好的擴(kuò)展性,并能克服因級聯(lián)而產(chǎn)生的時(shí)序問題。基于這種結(jié)構(gòu),在FPGA中實(shí)現(xiàn)了典型的LoG邊緣檢測算法與中值濾波算法。實(shí)驗(yàn)表明了這種預(yù)處理結(jié)構(gòu)的有效性和算法的可行性, 并能滿足視覺處理的實(shí)時(shí)性要求。

2018-12-13 17:56:52 37

37 為有效提高視頻監(jiān)控應(yīng)用領(lǐng)域中多屏幕畫面顯示的清晰度、分辨度等問題,提出了一種基于FPGA的實(shí)時(shí)視頻圖像處理算法。

2019-09-13 14:53:00 3490

3490 在選取較優(yōu)化的指紋識別預(yù)處理算法的基礎(chǔ)上,根據(jù)算法的結(jié)構(gòu)選取具有并行處理、低功耗、速度快等特點(diǎn)的FPGA作為實(shí)現(xiàn)算法的基本器件。由于用FPGA實(shí)現(xiàn)復(fù)雜算法較傳統(tǒng)器件從思考角度和實(shí)現(xiàn)方向上都有很大區(qū)別,所以本次設(shè)計(jì)從新的方向來完成傳統(tǒng)的指紋處理的設(shè)計(jì)。實(shí)際結(jié)果表明FPGA基本達(dá)到了設(shè)計(jì)的最初要求。

2021-02-03 15:53:00 11

11 CORD IC算法是在許多角度計(jì)算方面有著廣泛應(yīng)用的經(jīng)典算法,通過考慮FPGA 的結(jié)構(gòu)、精度局限和速度要求,采用流水線技術(shù)(pipeline ) ,在FPGA 上用CORDIC算法實(shí)現(xiàn)了對于大吞吐量數(shù)據(jù)的向量傾角的計(jì)算,并對實(shí)際應(yīng)用中內(nèi)部步驟寄存器精度的選取給出了較為詳細(xì)的方法。

2021-03-03 15:55:00 6

6 AN-1334:在3P4WY形系統(tǒng)中添加中心線線衰減網(wǎng)絡(luò)的影響

2021-03-18 21:32:24 8

8 結(jié)合三維掃描系統(tǒng),設(shè)計(jì)了基于FPGA的光帶中心線實(shí)時(shí)處理系統(tǒng),采用列掃描梯度質(zhì)心法,以硬件的形式實(shí)現(xiàn)了對光帶中心線的實(shí)時(shí)、快速、準(zhǔn)確提取,并將處理系統(tǒng)應(yīng)用于三維掃描領(lǐng)域進(jìn)行了實(shí)驗(yàn),所得結(jié)果真實(shí)、有效,滿足對30幀/s的圖像數(shù)據(jù)進(jìn)行實(shí)時(shí)提取的要求.

2021-03-22 16:06:55 12

12 針對多屏幕拼接顯示系統(tǒng)中高分辨率.高清晰、低失真的顯示需求,提出了一種基于FPGA實(shí)現(xiàn)的實(shí)時(shí)視頻處理算法。在介紹了DVI接口屏幕拼接顯示的系統(tǒng)結(jié)構(gòu)及FPGA算法的主要功能后,針對算法處理對象具有視頻

2021-03-31 15:23:09 10

10 為了調(diào)整圖像數(shù)據(jù)灰度,介紹了一種圖像灰度級拉伸算法的FPGA實(shí)現(xiàn)方法,并針對FPGA的特點(diǎn)對算法的實(shí)現(xiàn)方法進(jìn)行了研究,從而解決了其在導(dǎo)引系統(tǒng)應(yīng)用中的實(shí)時(shí)性問題。仿真驗(yàn)證結(jié)果表明:基于FPGA的圖像拉伸算法具有運(yùn)算速度快,可靠性高,功耗低等特點(diǎn),非常適合成像系統(tǒng)使用.

2021-04-01 14:14:49 10

10 為了調(diào)整圖像數(shù)據(jù)灰度,介紹了一種圖像灰度級拉伸算法的FPGA實(shí)現(xiàn)方法,并針對FPGA的特點(diǎn)對算法的實(shí)現(xiàn)方法進(jìn)行了研究,從而解決了其在導(dǎo)引系統(tǒng)應(yīng)用中的實(shí)時(shí)性問題。仿真驗(yàn)證結(jié)果表明:基于FPGA的圖像拉伸算法具有運(yùn)算速度快,可靠性高,功耗低等特點(diǎn),非常適合成像系統(tǒng)使用.

2021-04-01 14:14:49 1

1 顯然OpenCV中常見的輪廓分析無法獲得上面的中心紅色線段,本質(zhì)上這個(gè)問題是如何提取二值對象的骨架,提取骨架的方法在OpenCV的擴(kuò)展模塊中,另外skimage包也支持圖像的骨架提取。

2021-04-26 13:49:13 1632

1632 如何提取二值對象的骨架,提取骨架的方法在OpenCV的擴(kuò)展模塊中,另外skimage包也支持圖像的骨架提取。這里就分別基于OpenCV擴(kuò)展模塊與skimage包來完成骨架提取,得到上述圖示的中心線。 01 安裝skimage與opencv擴(kuò)展包 Python環(huán)境下安裝skimage圖像處理包與op

2021-04-26 13:51:13 3331

3331 第一部分 設(shè)計(jì)概述 1.1 設(shè)計(jì)目的 在多媒體技術(shù)高度發(fā)展的今天,視頻信息安全愈發(fā)受到人們的關(guān)注。傳統(tǒng)的視頻加密方法主要應(yīng)用在軟件層面上,其算法設(shè)計(jì)復(fù)雜、加密速度慢,不適用于視頻的實(shí)時(shí)加密。FPGA

2021-11-01 11:35:41 2692

2692

電動機(jī)產(chǎn)品運(yùn)行過程中,磁力中心線與機(jī)械中心線完全重合,是一種非常完美的狀態(tài),但鑒于實(shí)際生產(chǎn)過程不可避免的一些誤差,往往會存在機(jī)械中心線與磁力中心線的不重合,即在電機(jī)通電后出現(xiàn)磁力中心線的對中,同時(shí)伴隨電機(jī)轉(zhuǎn)子出現(xiàn)不同程度的軸向竄動。

2023-05-30 16:39:01 1152

1152 電子發(fā)燒友網(wǎng)站提供《TouchGFX圖形應(yīng)用在亮屏?xí)r的低功耗實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-09-20 11:26:55 1

1 運(yùn)算的運(yùn)算步驟遠(yuǎn)比定點(diǎn)運(yùn)算繁瑣,運(yùn)算速度慢且所需硬件資源大大增加,因此基于浮點(diǎn)運(yùn)算的LMS算法的硬件實(shí)現(xiàn)一直以來是學(xué)者們研究的難點(diǎn)和熱點(diǎn)。 本文正是基于這種高效結(jié)構(gòu)的多輸入FPA,在FPGA上成功實(shí)現(xiàn)了基于浮點(diǎn)運(yùn)算的LMS算法。測試

2023-12-21 16:40:01 228

228

電子發(fā)燒友App

電子發(fā)燒友App

評論