利用FPGA實現雙口RAM的設計及應用

概述:為了在高速采集時不丟失數據,在數據采集系統和

2010-04-16 14:08:36 11323

11323

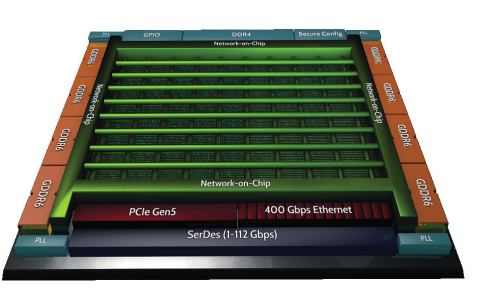

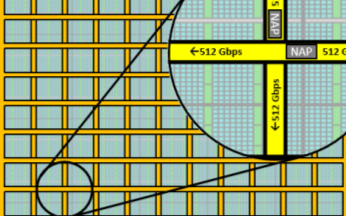

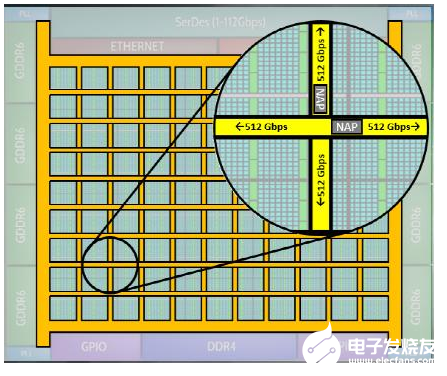

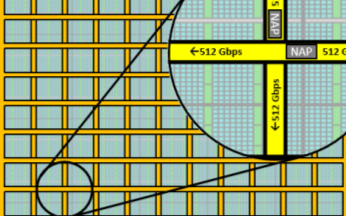

NoC的內部由一組行和列組成,它們在整個FPGA邏輯陣列中將網絡數據流量從水平和垂直方向上進行分發。

2020-06-03 16:55:08 1430

1430

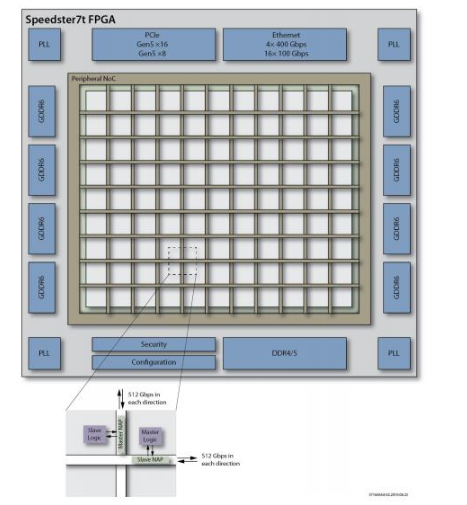

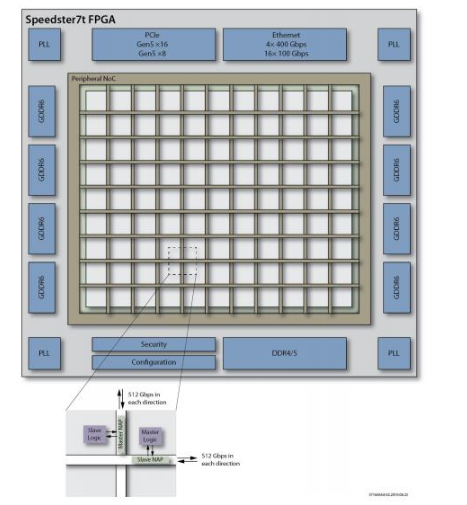

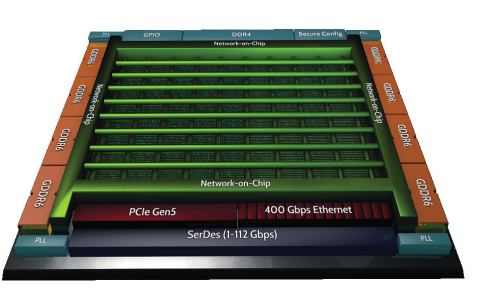

Achronix 在其最新基于臺積電(TSMC)7nm FinFET工藝的Speedster7t FPGA器件中包含了革命性的創新型二維片上網絡(2D NoC)。

2020-08-21 14:44:57 696

696 Speedster7t架構中的2D NoC提供了從邏輯陣列的可編程邏輯到位于I/O環中的高速接口子系統的高帶寬連接,用于連接到片外資源。

2021-07-07 16:31:31 1863

1863

創新的二維片上網絡(2D NoC)來處理這些高帶寬數據流。Achronix的FPGA中特有的2D NoC實現是一種創新,它與用可編程邏輯資源來實現2D?NoC的傳統方法相比,有哪些創新和價值呢?本白皮書討論了這兩種實現2D NoC的方法,并提供了一個示例設計,以展示與軟2D NoC實現相比,

2022-04-21 18:02:56 5750

5750

只有在腦海中建立了一個個邏輯模型,理解FPGA內部邏輯結構實現的基礎,才能明白為什么寫Verilog和寫C整體思路是不一樣的,才能理解順序執行語言和并行執行語言的設計方法上的差異。在看到一段簡單程序的時候應該想到是什么樣的功能電路。

2022-08-25 11:12:00 739

739 2D NoC如同在FPGA可編程邏輯結構上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數據傳輸提供了超高帶寬。

2021-11-11 14:20:14 2760

2760

背光區域調節技術2D區域調光的優點2D區域調光面臨的難題及機遇

2021-02-26 08:21:12

FPGA 內部詳細架構FPGA 芯片整體架構1.可編程輸入輸出單元(IOB)(Input Output Block)2.可配置邏輯塊(CLB)(Configurable Logic Block)3.

2021-07-30 08:10:06

刪除高扇出 nets。因此,如果您正在開發基于FPGA的高速設計,即使不是數字射頻應用,您有必要盡快下載和閱讀上述白皮書以開始您的設計—— “利用賽靈思All Programmable FPGA 和 SoC 實現高速無線電設計”。

2017-02-10 17:10:32

FPGA實現高速FFT處理器的設計介紹了采用Xilinx公司的Virtex - II系列FPGA設計高速FFT處理器的實現方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復雜邏輯,采用

2012-08-12 11:49:01

FPGA(Field-Programmable Gate Array,現場可編程門陣列)是一種特殊的集成電路,其內部結構由大量的可配置邏輯塊和互連線組成。FPGA可以通過編程來實現各種數字系統功能

2024-01-26 10:03:55

排列于芯片四周;可編程內部互連包括各種長度的連線線段和一些可編程連接開關,它們將各個可編程邏輯塊或I/O塊連接起來,FPGA在可編程邏輯塊的規模,內部互連線的結構和采用的可編程元件上存在較大的差異.較

2020-08-28 15:41:47

兩種技術實現。并發是指重復分配計算資源,使得多個模塊之間可以同時獨立進行計算。 FPGA的基本特點 1)采用FPGA設計ASIC電路,用戶不需要投片生產,就能得到合用的芯片。 2)FPGA可

2020-10-26 14:35:32

通道主要提供邏輯塊、宏單元、輸入/輸出引腳間的互連網絡。輸入/輸出塊(I/O塊)提供內部邏輯到器件I/O引腳之間的接口。FPGA :FPGA(Field Programmable Gate Array

2023-02-23 15:24:55

NoC在高端FPGA的應用是什么?NoC給Speedster 7t FPGA帶來的優勢有哪些?

2021-06-17 11:12:26

。為了解決這一問題,Achronix 在其最新基于臺積電(TSMC)7nm FinFET 工藝的 Speedster7t FPGA 器件中包含了革命性的創新型二維片上網絡(2D NoC)。這種 2D

2020-09-07 15:25:33

在超高速數據采集方面,FPGA(現場可編程門陣列)有著單片機和DSP所無法比擬的優勢。FPGA時鐘頻率高,內部時延小,目前器件的最高工作頻率可達300MHz;硬件資源豐富,單片集成的可用門數達1000萬門;全部控制邏輯由硬件資源完成,速度快,效率高;組成形式靈活,可以集成外圍控制、譯碼和接口電路。

2019-08-02 06:51:33

ADSP-21065L的片內RAM來中轉,然后再完成高速緩存到海量緩存的數據傳輸,具體做法如圖4所示。 ADSP內部開設有1k32bit的RAM塊構成中轉區,可利用外部口DMA通道0進行A/D高速緩存到片內

2020-12-04 15:59:14

Arm?CoreLink? NI?710AE片上網絡互連是一種高度可配置的AMBA?兼容系統級互連,可實現汽車和工業應用的功能安全。使用NI?710AE,您可以創建一個非相干互連,該互連針對SoC

2023-08-08 06:24:43

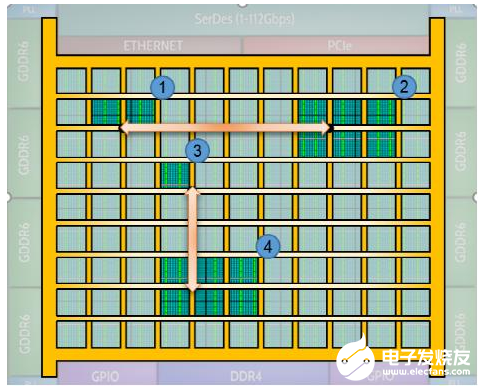

的7nmFinFET工藝,其架構采用革命性的新型2D片上網絡(NoC),獨創的機器學習處理器矩陣(MLP),并利用高帶寬GDDR6控制器、400G以太網和PCIExpressGen5接口,在保障ASIC級別性能的同時

2021-07-07 08:00:00

第41章 STM32F429的LTDC應用之LCD漢字顯示和2D圖形顯示本章教程為大家講解LTDC應用中最基本的漢字顯示和2D圖形顯示功能實現。目錄第41章 STM32F429的LTDC應用之LCD

2021-08-10 07:24:07

【作者】:李旺遠;王長山;【來源】:《計算機與現代化》2010年03期【摘要】:隨著芯片集成度的提高,基于片上系統[1](SoC)的片上網絡(NoC)已成為芯片設計的重點。隨著IP核的增多,節點和鏈

2010-04-22 11:35:04

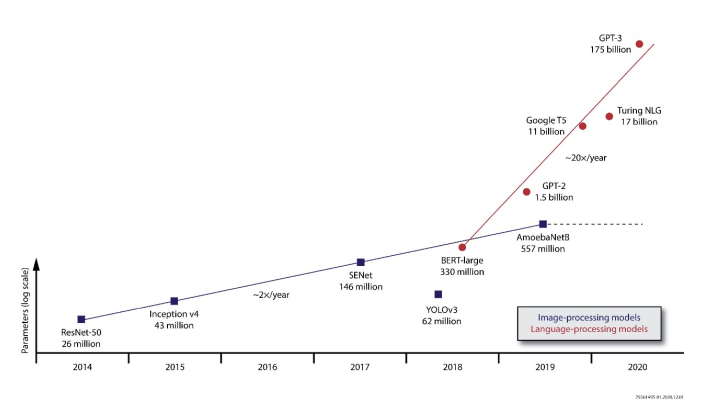

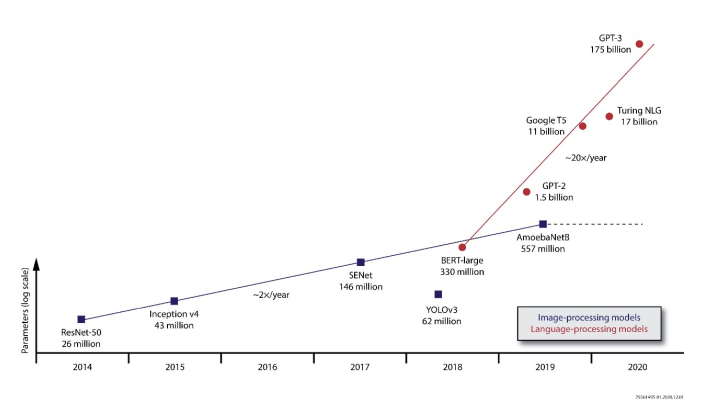

的FPGA資源可以看成是“無限”的,因此可以將一個大的DNN模型分解成若干小部分,每個小部分可以完整映射到單個FPGA上實現,然后各部分再通過高速數據中心網絡互連。這樣不僅保證了低延時與高帶寬的性能要求,也

2019-08-11 04:00:00

)來實現組合邏輯,每個查找表連接到一 個D觸發器的輸入端,觸發器再來驅動其他邏輯電路或驅動I/O,由此構成了既可實現組合邏輯功能又可實現時序邏輯功能的基本邏輯單元模塊,這些模塊間利用 金屬連線互相連接或

2019-08-11 04:30:00

高速主機接口,用于與服務器軟件進行數據交互。上述所有模塊均通過具有高帶寬的NoC實現互連。GNN內核微架構在開始討論GNN內核的微架構之前,有必要先回顧一下GraphSAGE算法。其內層循環的聚合和合

2021-09-25 17:20:41

互聯網絡,如何在傳統二維平面結構電子插件的三維空間上實現光通信,而目前的研究已經深入到VLSI器件的內部。目前發展最快的多級光互連交換系統是自由空間光互連交換網絡。這主要有兩個方面的原因:1)自由空間光

2016-01-29 09:17:10

求大佬分享一款不錯的基于FPGA超高速雷達住處實時采集存儲系統

2021-04-15 06:56:25

你好,我正在使用帶有AD6676-EBZ高速adc的定制FPGA平臺。該邏輯包含JESD24B IP。我想將VIO范圍用于眼圖。但我真的不明白它是如何運作的。我發現2D眼睛掃描邏輯提供了通過axi4

2020-07-30 10:24:35

基于FPGA的超高速FFT硬件實現介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數超高速FFT硬件系統設計與實現方法,當多組大點數進行FFT運算時,利用FPGA

2009-06-14 00:19:55

。 2 輸入輸出接口研究 Virtex Ⅱ-PRO系列是在Virtex Ⅱ系列FPGA的基礎上,嵌入了高速I/O接口和IBM PowerPC處理器,它能實現超高帶寬的系統芯片設計,支持LVDS

2018-12-18 10:22:18

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

機載視頻圖形顯示系統主要實現2D圖形的繪制,構成各種飛行參數畫面,同時疊加實時的外景視頻。由于FPGA具有強大邏輯資源、豐富IP核等優點,基于FPGA的嵌入式系統架構是機載視頻圖形顯示系統理想的架構

2019-06-24 06:07:53

基于FPGA的通用高速串行互連協議設計基于FPGA的通用高速串行互連協議設計

2012-08-11 15:46:52

一秒鐘的意義得到了升華。汪博士和他的同事們成功的創造出了壓縮超高速攝影(CUP)相機,這是目前全球拍攝速度最快的2D相機,其每秒能夠拍攝高達1,000億幀畫面,而典型的傻瓜相機每秒僅能拍攝2至15幀畫面

2018-09-11 11:21:58

】:CNKI:SUN:HZLG.0.2010-03-010【正文快照】:為解決蟲孔交換機制下的隊列頭阻塞問題,大多數片上網絡(NoC)[1~3]采用了虛通道技術[4,5],利用該技術能減少隊列頭阻塞的次數

2010-04-22 11:34:25

高速連續數據采集系統的背景及功能是什么?如何利用FPGA實現高速連續數據采集系統設計?FPGA在高速連續數據采集系統中的應用有哪些?

2021-04-08 06:19:37

如何利用FPGA實現一個ROM FPGA片內ROM測試實驗

2021-03-03 06:47:23

本文研究設計了一種基于高速隔離芯片的高速串行隔離型ADC。該數字隔離型ADC頻帶寬,延時小,穩定性高并且電路結構簡單。利用FPGA作為控制器,很好地實現了模數轉換和隔離傳輸。

2021-05-06 06:38:57

邏輯結構之上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數據傳輸提供了大約高達27Tbps的超高帶寬。作為Speedster7t FPGA器件中的重要創新之一,2D NoC為FPGA

2020-10-20 09:54:00

NoC為FPGA設計提供了哪些優勢?NoC在FPGA內部邏輯互連中發揮的作用是什么?如何利用片上高速網絡創新地實現FPGA內部超高帶寬邏輯互連?

2021-06-17 11:35:28

影響著系統開發人員在機械和電氣方面的板級設計工作。裸片、芯片封裝和電路板構成了一個緊密連結的系統,在這個系統中,要完全實現FPGA的功能,需要對PCB板進行精心設計。

2019-08-20 07:33:53

再利用FET5718核心板控制超高速雙通道ADC進行數據采集,并實現動態波形繪制顯示,硬件設計需要如何進行資源分配,可以達到顯示不丟失數據的性能. ADC 為24bit 采樣率 為256K~1Mhz需要提供高速同步時鐘獲取數據.硬件設計可以實現嗎?

2022-11-21 12:10:01

介紹了利用現場可編程邏輯門陣列FPGA實現直接數字頻率合成(DDS)的原理、電路結構和優化方法。重點介紹了DDS技術在FPGA中的實現方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進行直接數字頻率合成的VHDL源程序。

2021-04-30 06:29:00

。ECP5 FPGA支持與ASIC、ASSP和應用處理器實現互連,并具備優化的I/O和體系架構。增強的嵌入式DSP塊和高度并行的FPGA邏輯架構為計算密集型協處理功能提供了所需的高性能支持。ECP5 FPGA

2020-10-21 11:53:02

前言FPGA 可以實現高速硬件電路,如各種時鐘,PWM,高速接口,DSP計算等硬件功能。這是Cortex-M 處理器軟件無法比擬的。要實現FPGA 的邏輯設計,對于嵌入式系統工程師又是比較復雜和具有

2021-12-21 06:13:49

網絡連接到USB主機。本文將探討其設計方法,可以在FPGA或ASIC系統中實現高效高速USB 2.0接口。圖1 基于USB的分布式***采集系統 在介紹整合通用串行總線接口到FPGA或ASIC系統的各種

2012-11-22 16:11:20

。 解析FPGA的片上資源使用情況 如何分析FPGA芯片上的組合邏輯(LUT)和時序邏輯(REG)的利用率。 一、如何得到LUT與REG的使用比例我們先看一個FPGA工程的編譯結果

2019-06-17 09:03:28

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

本文利用CORDIC算法在FPGA上實現了高速自然對數變換器。

2021-04-30 06:05:22

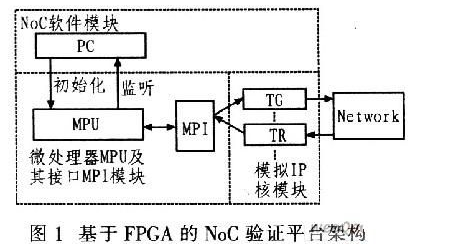

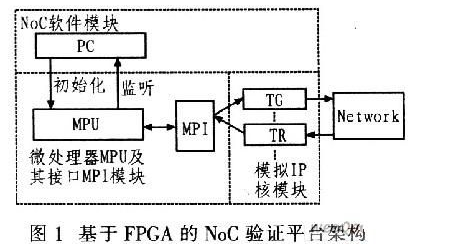

本文提出了一種基于FPGA的NoC驗證平臺。詳細討論了該驗證平臺中FPGA硬件平臺和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點。通過一個實例仿真驗證的結果說明了該驗證平臺的基本功能和優越性。

2021-05-06 07:20:48

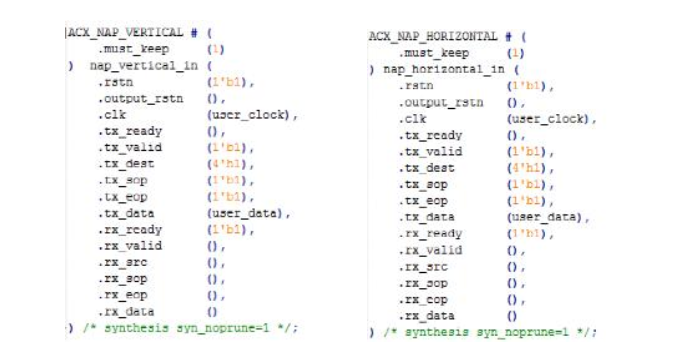

288bit的原始數據模式(Raw data mode)。 用戶可以通過這288bit的信號進行邏輯直連或者自定義協議互連。圖3利用2D NoC進行內部邏輯互連在NoC的每個交叉點上都有兩個網絡接入點

2020-05-12 08:00:00

實時處理,因而帶來了對FPGA等硬件數據處理加速器的需求。如圖1所示。在這樣的數據高速增長的情況下,用于傳輸數據的網絡帶寬和處理數據所需要的算力也必須急速增長。傳統的CPU已經越來越不堪重負,所以用硬件加速

2021-12-21 08:00:00

的讀寫效率最后,我們測試一下7t1500上GDDR6控制器的讀寫效率,所有的測試結果基于仿真數據。因為7t1500包含了片上網絡(NoC),并且NoC已經實現了仲裁,時鐘域轉換的邏輯,我們用三個用戶邏輯

2021-12-22 08:00:00

的 7nm FinFET 工藝,其架構采用革命性的新型 2D 片上網絡 (NoC),獨創的機器學習處理器矩陣 (MP),并利用高帶寬 GDDR6 控制器、400G 以太網和 PCI Express

2020-10-20 09:48:39

好久沒發帖了,最近比較忙也比較急,求推薦16位以上高速AD芯片

2019-06-19 04:36:14

請問這樣的2D數組怎么創建代表什么意思

2019-09-02 15:51:55

采用片上網絡(NoC)的新型FPGA數據架構賦能5G網絡和數據中心智能網卡(SmartNIC)設計方案

2021-02-22 08:01:25

ADC 及DAC 的DRFM 系統得到廣泛應用[1~4 ]。本文利用GaAs MESFET 全離子注入非自對準常規工藝設計了用于3bit 相位體制DRFM 系統的單片超高速相位體制ADC。測試結果表明

2019-07-09 06:57:23

,如果大家想在對話框上面繪制2D圖形的話,可以將STemWin的2D繪制函數放在對話框回調函數中的WM_PAINT消息中實現。 這里跟大家講一下如何利用uCGUIBulder4.0在對話框上面繪制簡單的橫線和豎線。60.1.1 第一步:建立如下界面

2016-10-18 11:33:49

最重要的提升帶寬的方法,這也是推動數據中心網絡高速發展的原始動力。隨著物理層單鏈路達到 112Gbps ,數據中心網絡將會在絡系統設計、設備整機設計、關鍵組件設計多個方面面臨巨大的信號完整性的挑戰

2022-09-28 10:43:13

與FPGA中的普通路由相比,使用片上網絡來互連DSP48A會降低性能嗎?以上來自于谷歌翻譯以下為原文Will the use of network on chip to interconnect

2019-06-28 09:39:03

無誤,則寫入為該接口分配的PL4模塊中的FIFO,否則丟棄。為了充分利用帶寬,PL4接口把MAC幀劃分為數據片(以64字節或MAC幀尾之前數據為一片)調度輸出,并采用帶內控制字的形式指示幀頭、數據、幀尾

2019-04-29 07:00:07

手勢功能并與2D PCAP多點觸摸設計實現無縫結合而言,GestIC技術可謂是一款復雜性極低的解決方案。利用這一方案,設計人員現在可以輕松地結合2D和3D用戶界面技術來建立易用的創新應用。” 2D/3D觸摸與手勢開發工具包(DV102014)現已開始供應。

2018-11-07 10:45:56

《Fundamentals of Computer Graphics》翻譯(三):隱式2D直線

2019-09-03 12:19:29

介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數超高速FFT硬件系統設計與實現方法,當多組大點數進行FFT運算時,利用FPGA內部大容量存儲資源,采

2009-04-26 18:33:08 26

26 片上網絡(Network-on-Chip, NoC)以網絡互連結構代替傳統總線結構,很好地解決了片上高性能計算資源之間的通信瓶頸問題。路由器是實現NoC 的重要基礎部件,本文在分析國內外相關

2009-12-14 09:37:38 34

34 介紹了一種基于FPGA 的超高速數據采集與處理系統,給出了系統實現的方案,并詳細闡述了各硬件電路的具體構成。對系統軟件功能做了簡要介紹,并利用嵌入式邏輯分析儀對該超高

2010-01-20 16:03:27 58

58 比較了多種DSP芯片的互連性能,給出了一種簡單高性能DSP網絡結構。針對構成DSP網絡通訊接口的鏈路口,分析其基本特點,并且提出了在FPGA中實現的設計原理。最后給出了設計仿真圖和

2010-07-27 16:46:46 22

22 高速串并轉換器的設計是FPGA 設計的一個重要方面,傳統設計方法由于采用FPGA 的內部邏輯資源來實現,從而限制了串并轉換的速度。該研究以網絡交換調度系統的FGPA 驗證平臺中多路高

2010-09-22 08:29:41 81

81 分析當前高速互連網絡中同時存在的TCP/IP, GAMMA, InfiniBand, SCI 等技術的實現機制,介紹RapidIO 高性能總線技術。研究RapidIO 協議和MPC8548 處理器的相關技術,提出在RapidIO 高速互連網

2010-09-22 08:35:11 20

20 隨著FPGA設計復雜度的增加,傳統測試方法受到限制。在高速集成FPGA測試中,其內部信號的實時獲取和分析比較困難。介紹了Quartus II中SingalTap II嵌入式邏輯分析器的使用,并給出一個

2010-12-17 15:25:17 16

16 針對基于軟件仿真片上網絡NoC(Network on Chip)效率低的問題,提出基于FPGA的NoC驗證平臺構建方案。該平臺集成可重用的流量產生器TG(Traffic Generation),流量接收器TR(Traffic Receiver)

2011-01-04 16:24:38 12

12 基于漢明碼的糾錯原理.根據對64位數據進行檢糾錯處理的需要,設計一個利用8位校驗碼,以實現該功能的算法邏輯,并通過FPGA實現。

2011-09-15 15:14:58 1382

1382

基于FPGA的通用高速串行互連協議設計。

2016-05-11 09:46:01 18

18 DSP與FPGA高速的數據傳輸有三種常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 現場可編程邏輯門陣列) 設計 FIFO的接口電路,即可實現高速互聯。

2017-02-11 14:16:10 2487

2487

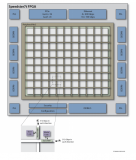

為了能夠靈活地驗證和實現自主設計的基于NoC的多核處理器,縮短NoC多核處理器的設計周期,提出了設計集成4片Virtex-6—550T FPGA的NoC多核處理器原型芯片設計/驗證平臺。分析和評估

2017-11-22 09:15:01 4137

4137 本文提出的基于FPGA的NoC驗證平臺在仿真速度方面是一般基于HDL的軟件仿真的16 000倍,而基于PC機編寫的NoC軟件更增強了該平臺的靈活性和實用性。

2019-04-13 11:33:47 2053

2053

了革命性的新型二維片上網絡(2D NoC)。2D NoC如同在FPGA可編程邏輯結構上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數據傳輸提供了超高帶寬(~27Tbps

2020-03-04 15:59:39 1517

1517 Achronix 最新基于臺積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網絡(2D NoC)。

2020-05-04 09:43:00 593

593 Achronix 最新基于臺積電(TSMC)的7nm FinFET工藝的Speedster7t FPGA器件包含了革命性的新型二維片上網絡(2D NoC)。

2020-05-28 10:27:12 527

527

在數字系統互連設計中,高速串行/O技術取代傳統的并行/O技術成為當前發展的趨勢。與傳統并行丨/技術相比,串行方案提供了更大的帶寬、更遠的距離、更低的成本和更高的擴展能力,克服了并行l/O設計存在的缺陷在實際設計應用中,采用現場可編程門陣列FPGA實現高速串行接口是一種性價比較高的技術途徑。

2020-08-24 17:28:00 15

15 可編程邏輯結構上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數據傳輸提供了超高帶寬。 2. 2D NoC給Speedster 7t FPGA帶來的優勢 日益增長的數據加速需求對硬件平臺

2021-11-12 09:21:22 1777

1777

片上網絡(2D NoC)來處理這些高帶寬數據流。Achronix的FPGA中特有的2D NoC實現是一種創新,它與用可編程邏輯資源來實現2D NoC的傳統方法相比,有哪些創新和價值呢?本白皮書討論

2022-04-21 09:27:35 1044

1044 Achronix Speedster7t FPGA除了在外圍Hard IP上都采用目前業內領先的大帶寬高速率IP,在內部的可編程邏輯的架構中也做了大量的優化去進一步提高內部可編程邏輯的性能,從而適配

2022-07-05 15:37:41 924

924 的數據傳輸帶寬以及 存儲器 帶寬。但是在FPGA內部,可編程邏輯部分隨著工藝提升而不斷進步的同時,內外部數據交換性能的提升并沒有那么明顯,所以FPGA內部數據的交換越來越成為數據傳輸的瓶頸。 為了解決這一問題,Achronix 在其? 基于臺積電(TSMC)7nm FinFET工藝

2023-04-18 11:30:06 300

300 NoC是相對于SoC的新一代片上互連技術,從計算機發展的歷史可以看到NoC 必將是SoC 之后的下一代主流技術

2023-07-13 15:56:43 635

635

2023年9月18日, 由傳智驛芯科技和Arteris聯合舉辦的技術研討會——“利用創新NoC技術駕馭復雜的片上系統(SoC)設計” 在深圳成功舉辦。西安交通大學任鵬舉教授,Arteris中國

2023-09-18 18:17:53 325

325

可以商用的集成全域硬2D NoC的FPGA器件,以每通道512Gbps的速率和超過2Tbps的總帶寬來與所有系統接口和FPGA邏輯陣列互連。

2023-11-24 16:19:45 185

185

電子發燒友App

電子發燒友App

評論