3KW工業變頻器電路設計方案詳細說明

2024-03-19 08:33:09 50

50

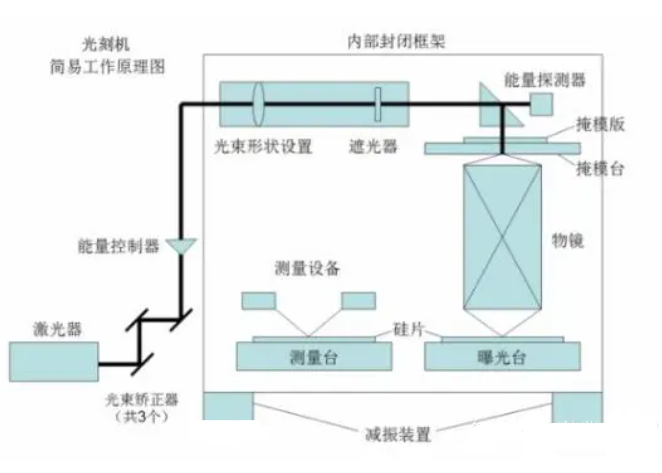

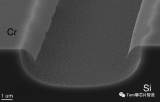

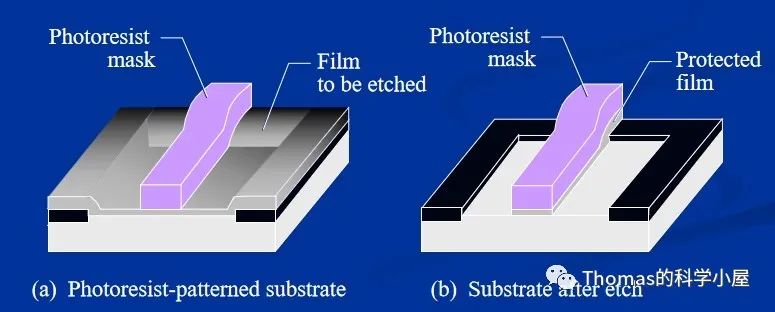

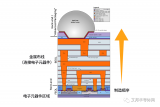

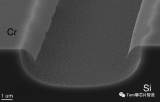

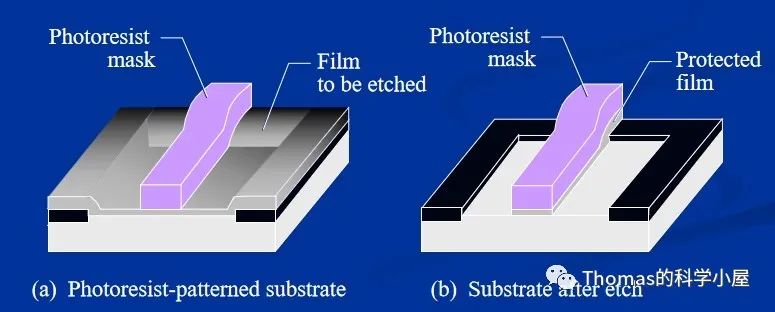

刻蝕機的刻蝕過程和傳統的雕刻類似,先用光刻技術將圖形形狀和尺寸制成掩膜,再將掩膜與待加工物料模組裝好,將樣品置于刻蝕室內,通過化學腐蝕或物理磨蝕等方式將待加工物料表面的非掩膜區域刻蝕掉,以得到所需的凹槽和溝槽。

2024-03-11 15:38:24 462

462

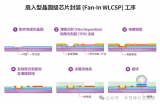

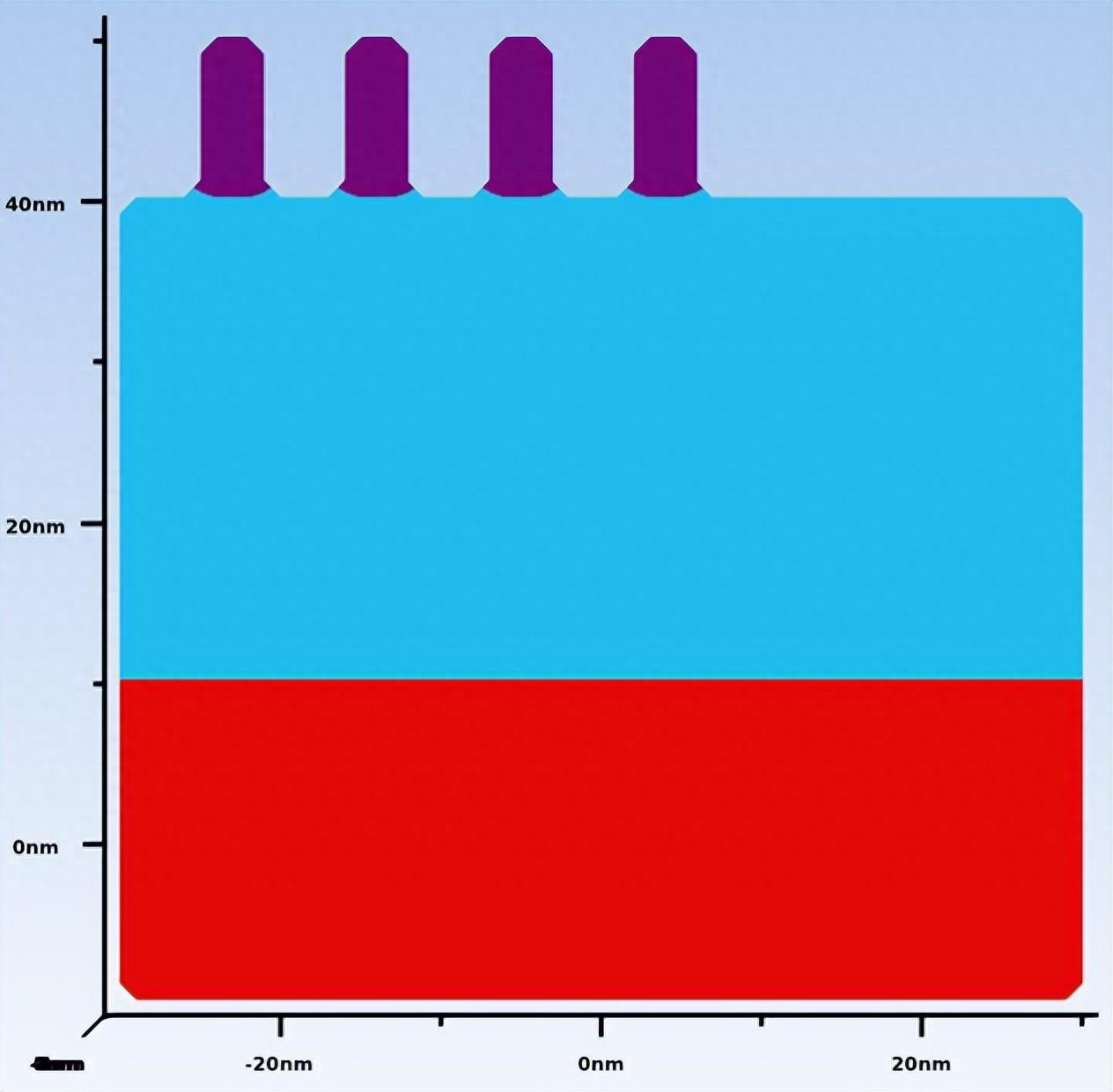

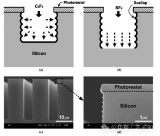

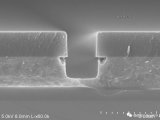

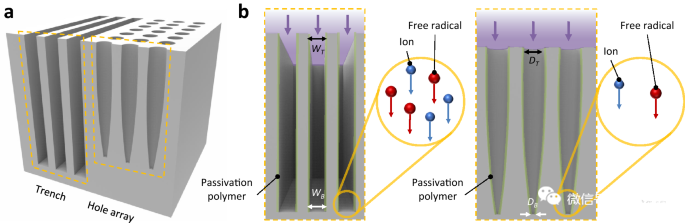

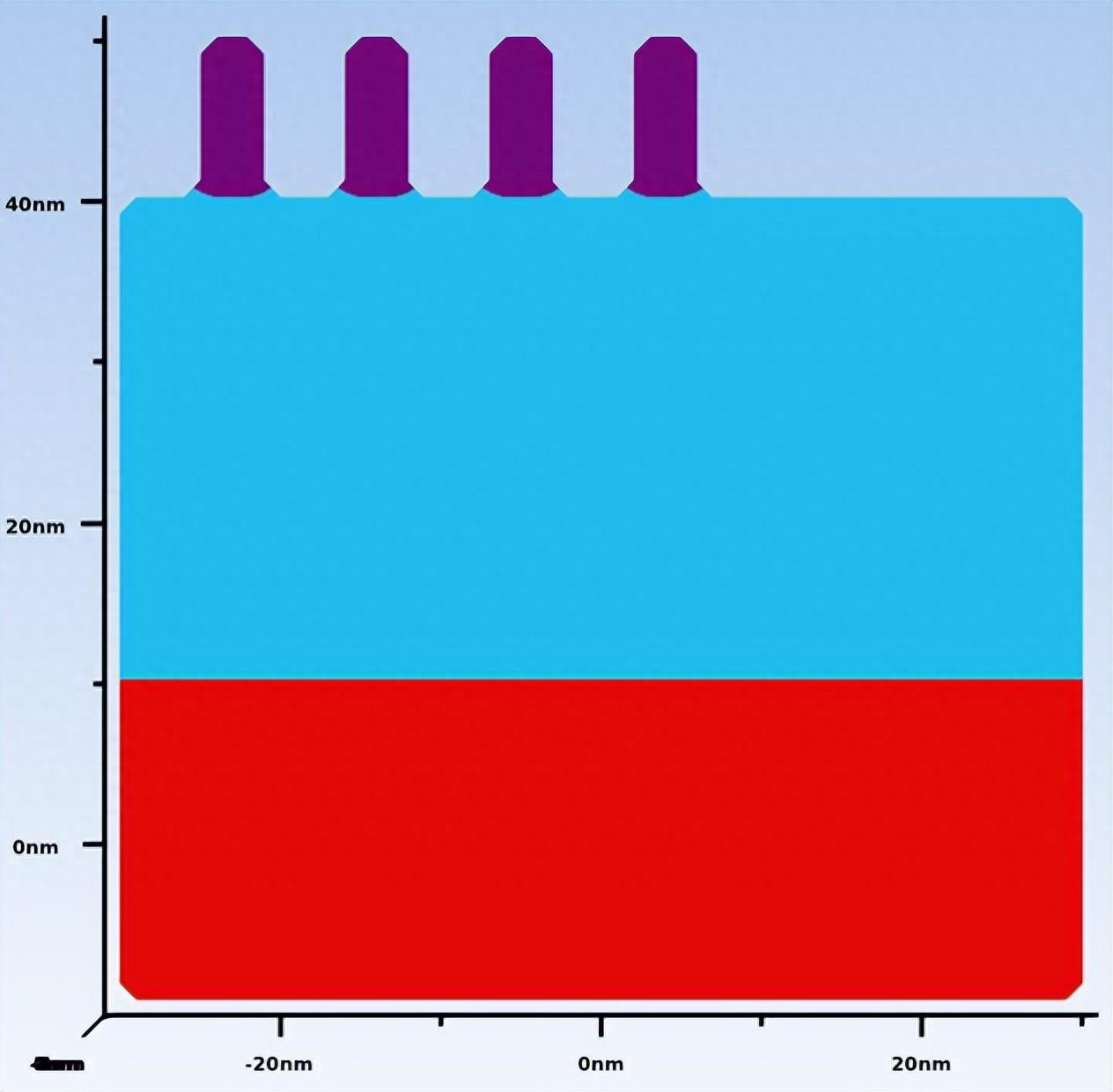

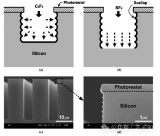

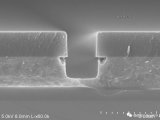

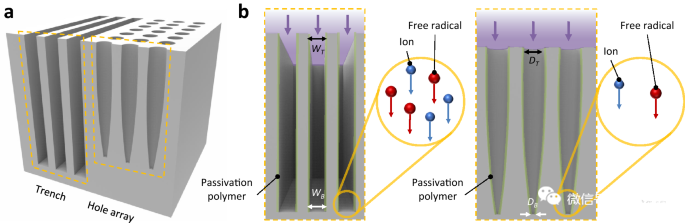

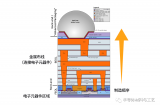

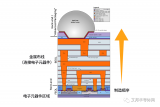

的 2.5D/3D 封裝技術可以實現芯片之間的高速、低功耗和高帶寬的信號傳輸。常見的垂直 TSV 的制造工藝復雜,容易造成填充缺陷。錐形 TSV 的側壁傾斜,開口較大,有利于膜層沉積和銅電鍍填充,可降低工藝難度和提高填充質量。在相對易于實現的刻蝕條件下制備

2024-02-25 17:19:00 119

119

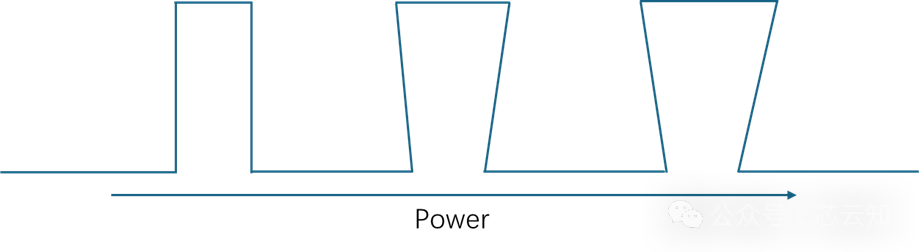

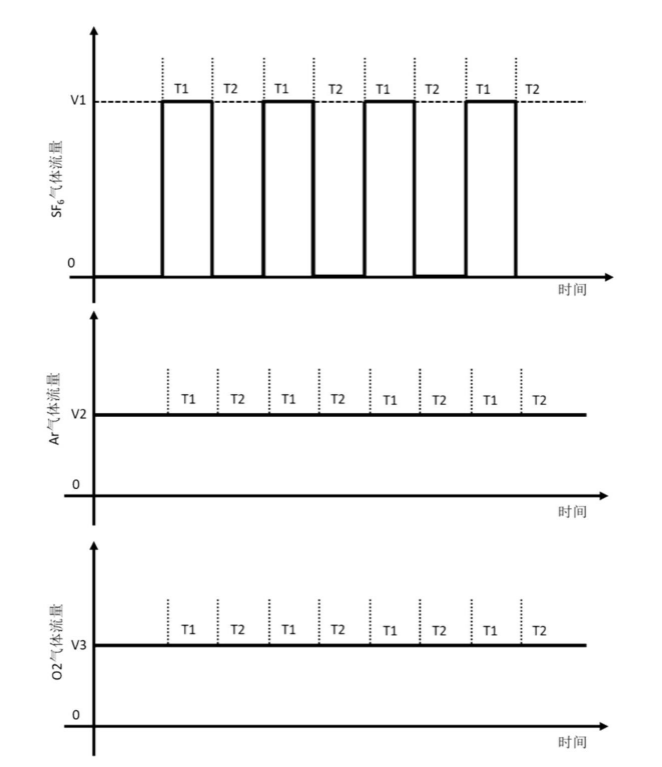

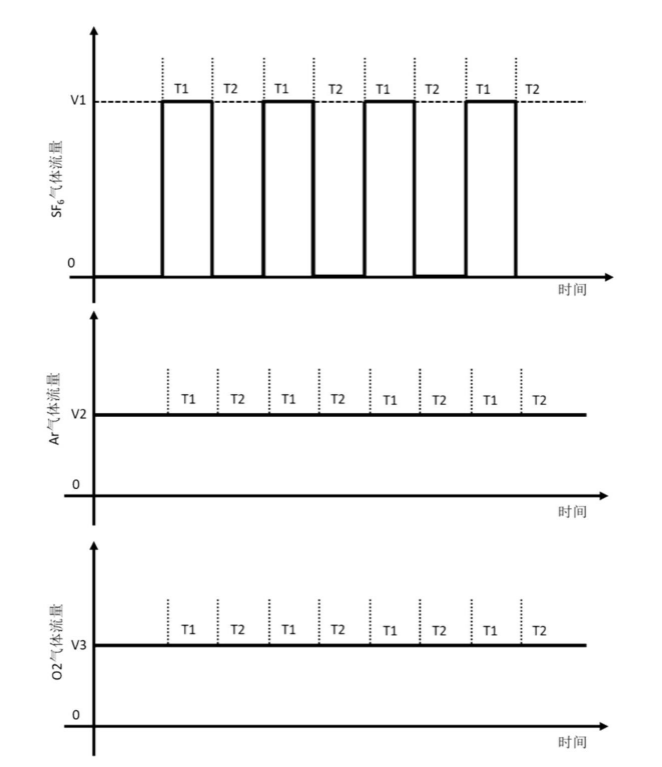

影響深硅刻蝕的關鍵參數有:氣體流量、上電極功率、下電極功率、腔體壓力和冷卻器。

2024-02-25 10:44:39 283

283

影響深硅刻蝕的關鍵參數有:氣體流量、上電極功率、下電極功率、腔體壓力和冷卻器。

2024-02-25 10:40:16 19

19

電源模塊外殼材質詳細說明 保護散熱絕緣 AC電源模塊 BOSHIDA 選擇電源模塊外殼材質時,需要考慮以下幾個因素: 保護性能:外殼材質需要具有足夠的強度和硬度,能夠保護電源模塊內部的電路和元件不受

2024-02-20 09:03:44 93

93 在半導體加工工藝中,常聽到的兩個詞就是光刻(Lithography)和刻蝕(Etching),它們像倆兄弟一樣,一前一后的出現,有著千絲萬縷的聯系,這一節介紹半導體刻蝕工藝。

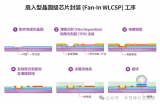

2024-01-26 10:01:58 548

548

、電鍍(Electroplating)工藝、光刻膠去膠(PR Stripping)工藝和金屬刻蝕(Metal Etching)工藝。

2024-01-24 09:39:09 335

335

干法刻蝕技術是一種在大氣或真空條件下進行的刻蝕過程,通常使用氣體中的離子或化學物質來去除材料表面的部分,通過掩膜和刻蝕參數的調控,可以實現各向異性及各向同性刻蝕的任意切換,從而形成所需的圖案或結構

2024-01-20 10:24:56 1106

1106

使用SEMulator3D?工藝步驟進行刻蝕終點探測 作者:泛林集團 Semiverse Solutions 部門軟件應用工程師 Pradeep Nanja 介紹 半導體行業一直專注于使用先進的刻蝕

2024-01-19 16:02:42 128

128

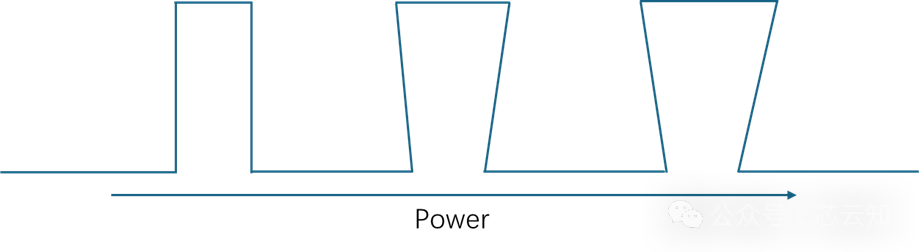

電源規格詳細說明了標題為“線路調整率”的參數的數字。結果發現,當線路或輸入電壓發生變化時,輸出端可能會出現微小的變化。線路調整率圖詳細說明了這一變化。

2024-01-17 14:35:20 194

194 對DRIE刻蝕,是基于氟基氣體的高深寬比硅刻蝕技術。與RIE刻蝕原理相同,利用硅的各向異性,通過化學作用和物理作用進行刻蝕。不同之處在于,兩個射頻源:將等離子的產生和自偏壓的產生分離

2024-01-14 14:11:59 511

511

ADUC7029 串口下載,利用官方ARMWSD.EXE軟件,請問一下,ADUC7029的SPM0 和SPM1怎么和PC的RS232連接?電源和GND呢?

2024-01-12 06:07:34

在紅外探測器的制造技術中,臺面刻蝕是完成器件電學隔離的必要環節。

2024-01-08 10:11:01 206

206

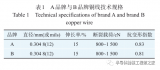

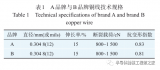

為了提高功率模塊銅線鍵合性能,采用6因素5水平的正交試驗方法,結合BP(Back Propaga‐tion)神經網絡與遺傳算法,提出了一種銅線鍵合工藝參數優化設計方案。首先,對選定樣品進行正交試驗

2024-01-03 09:41:19 248

248

下面就常見的焊接缺陷、外觀特點、危害、原因分析進行詳細說明。

2023-12-28 16:17:09 190

190 該專利詳細闡述了一種針對含硅有機介電層的高效刻蝕方法及相應的半導體工藝設備。它主要涉及到通過交替運用至少兩個刻蝕步驟來刻蝕含硅有機介電層。這兩個步驟分別為第一刻蝕步驟和第二刻蝕步驟。

2023-12-06 11:58:16 370

370

W刻蝕工藝中使用SF6作為主刻步氣體,并通過加入N2以增加對光刻膠的選擇比,加入O2減少碳沉積。在W回刻工藝中分為兩步,第一步是快速均勻地刻掉大部分W,第二步則降低刻蝕速率減弱負載效應,避免產生凹坑,并使用對TiN有高選擇比的化學氣體進行刻蝕。

2023-12-06 09:38:53 1536

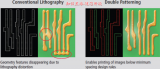

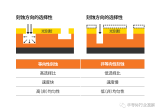

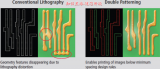

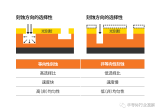

1536 很小的尺寸了(寬度或者間距),所以可以用兩層甚至更多層mask來制造一層金屬,如下圖所示,所以可以看到版圖中有紅色和綠色(但看一種顏色,它們的間距光刻是可以加工的)。工藝有LELE(光刻 刻蝕 光刻

2023-12-01 10:20:03 596

596

半導體前端工藝(第四篇):刻蝕——有選擇性地刻蝕材料,以創建所需圖形

2023-11-27 16:54:26 256

256

濕法刻蝕由于成本低、操作簡單和一些特殊應用,所以它依舊普遍。

2023-11-27 10:20:17 452

452

模組,其實就是把類似和相關的工序組成一個集合的概念,這樣就可以分配給相對的部門去負責,他們只做這一部分對應的工作。比如:刻蝕工藝工程師就專門做刻蝕這一部分工作,不要做薄膜的工作。

2023-11-25 15:08:25 3280

3280

PCB表面處理的選擇和優化,如何選擇最合適的工藝?

2023-11-24 17:16:09 304

304 在芯片制程中,很多金屬都能用等離子的方法進行刻蝕,例如金屬Al,W等。但是唯獨沒有聽說過干法刻銅工藝,聽的最多的銅互連工藝要數雙大馬士革工藝,為什么?

2023-11-14 18:25:33 2626

2626

但是里面也有幾個關鍵的工藝參數需要控制的。同樣Etch GaAs也可以用ICP干法刻蝕的工藝,比濕法工藝效果要好些,側壁也垂直很多。

2023-11-14 09:31:29 406

406 干法蝕刻(dry etch)工藝通常由四個基本狀態構成:蝕刻前(before etch),部分蝕刻(partial etch),蝕刻到位(just etch),過度蝕刻(over etch),主要表征有蝕刻速率,選擇比,關鍵尺寸,均勻性,終點探測。

2023-10-18 09:53:19 788

788

KT148A語音芯片的組合播放詳細說明 ,包含:語音制作 、壓縮、下載、播放

這里總共的步驟大概分為5步,其實也很簡單

組合播放的原理,其實就是KT148A一次性接收需要播放的語音組合,存入

2023-10-13 11:17:01 369

369

黑金Spartan6開發板的Verilog教程詳細說明

2023-10-11 18:02:45 1

1 刻蝕(或蝕刻)是從晶圓表面去除特定區域的材料以形成相應微結構。但是,在目標材料被刻蝕時,通常伴隨著其他層或掩膜的刻蝕。

2023-10-07 14:19:25 2073

2073

有過深硅刻蝕的朋友經常會遇到這種情況:在一片晶圓上不同尺寸的孔或槽刻蝕速率是不同的。

2023-10-07 11:29:17 1447

1447

在半導體制造中,刻蝕工序是必不可少的環節。而刻蝕又可以分為干法刻蝕與濕法刻蝕,這兩種技術各有優勢,也各有一定的局限性,理解它們之間的差異是至關重要的。

2023-09-26 18:21:00 3305

3305

本文檔的主要內容詳細介紹的是電子管的代換資料詳細說明。

2023-09-26 07:24:46

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-09-24 17:42:03 996

996

制作紅外激光感應的雷達組件!包含代碼、詳細說明

2023-09-22 07:49:01

在使用 ST FOC 電機庫時,當使用 Hall 信號作為位置信號時,需要輸入同步電角度數據,這個數據根據當前使用電機的特性進行輸入,會在每次 Hall 信號變化時同步電角度,如果角度偏差較大時會影響控制效果,可能帶來效率或者電機的震蕩,初始測試還是有必要的,本文詳細說明測試注意事項以及測試方法。

2023-09-11 07:43:13

KT142C-sop16語音芯片ic的串口指令詳細說明_默認9600指令可設

2023-09-07 12:00:04 382

382

NUC505支持多種啟動方式, 每種啟動的方式和流程,有沒有相關文檔說明? 官網沒有找到, 參考文檔也沒有詳細說明

2023-08-29 06:27:01

濕法刻蝕由于精度較差,只適用于很粗糙的制程,但它還是有優點的,比如價格便宜,適合批量處理,酸槽里可以一次浸泡25張硅片,所以有些高校和實驗室,還在用濕法做器件,芯片廠里也會用濕法刻蝕來顯露表面缺陷(defect),腐蝕背面多晶硅。

2023-08-28 09:47:44 890

890

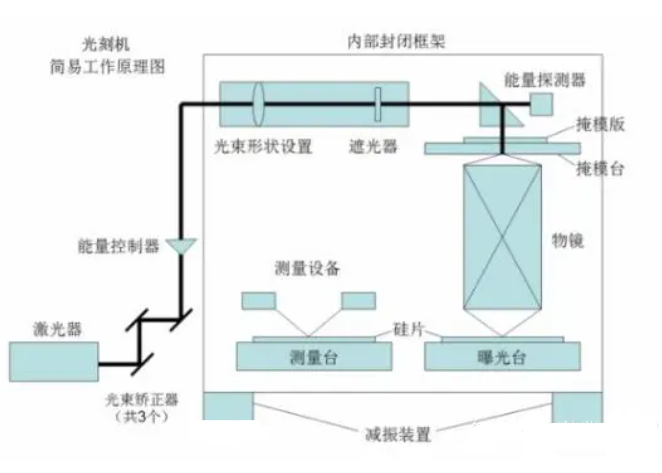

光刻蝕(Photolithography)是一種在微電子和光電子制造中常用的加工技術,用于制造微細結構和芯片元件。它的基本原理是利用光的化學和物理作用,通過光罩的設計和控制,將光影投射到光敏材料上,形成所需的圖案。

2023-08-24 15:57:42 2270

2270 PVP可以在刻蝕過程中形成一層保護性的膜,降低刻蝕劑對所需刻蝕材料的腐蝕作用。它可以填充材料表面的裂縫、孔洞和微小空隙,并防止刻蝕劑侵入。這樣可以減少不需要的蝕刻或損傷,提高刻蝕的選擇性。

2023-08-17 15:39:39 2855

2855 模式下運行。

有關AXI協議的詳細說明,請參閱AMBA AXI協議規范。

有關APB協議的詳細說明,請參閱AMBA APB協議規范。

本節總結了周期模型的功能與硬件的功能,以及周期模型的性能和準確性

2023-08-16 06:41:45

PL340內存控制器是一款高性能、面積優化的SDRAM或移動SDR內存控制器,兼容高級微控制器總線架構(AMBA)AXI協議。

有關AXI協議的詳細說明,請參閱AMBA AXI協議規范。

本節總結

2023-08-12 06:25:03

PL341內存控制器是一款高性能、面積優化的DDR2 SDRAM內存控制器,兼容高級微控制器總線架構(AMBA)AXI協議。

有關AXI協議的詳細說明,請參閱AMBA AXI協議規范。

本節總結了周期模型的功能與硬件的功能,以及周期模型的性能和準確性。

2023-08-12 06:01:49

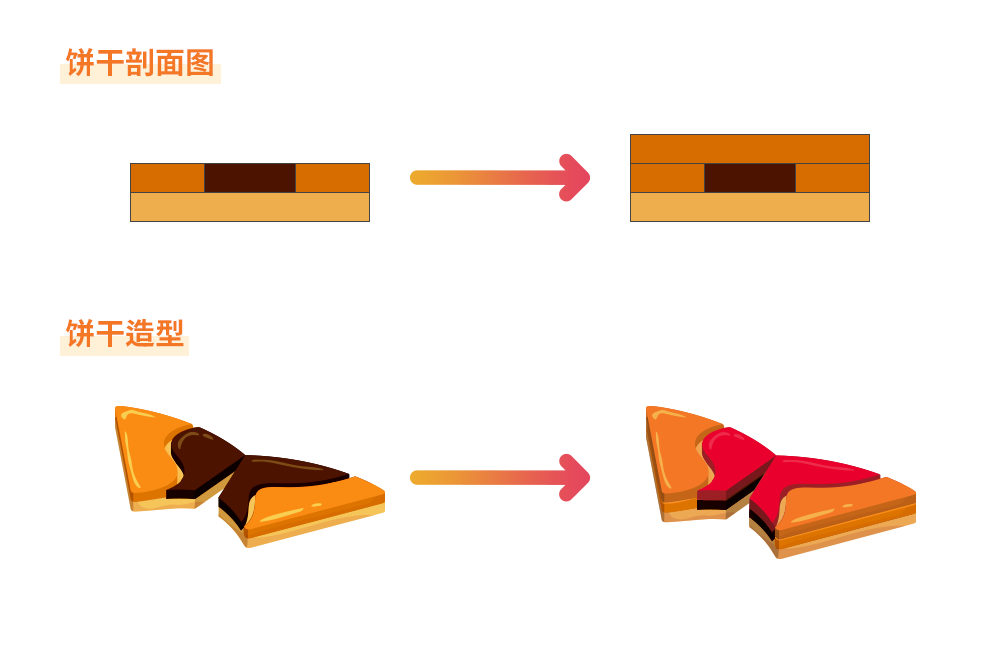

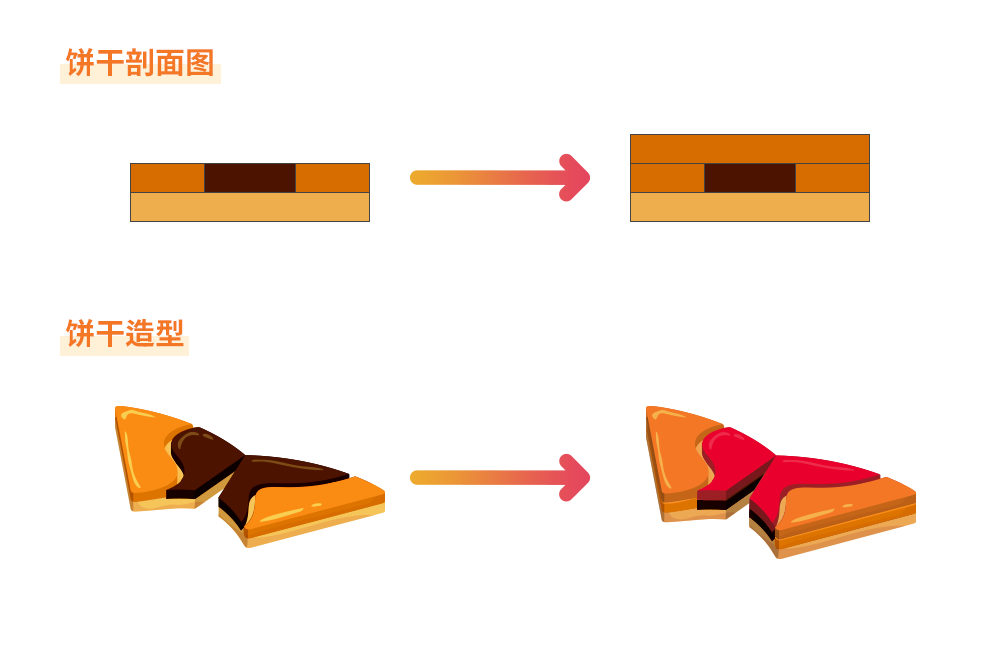

在半導體前端工藝第三篇中,我們了解了如何制作“餅干模具”。本期,我們就來講講如何采用這個“餅干模具”印出我們想要的“餅干”。這一步驟的重點,在于如何移除不需要的材料,即“刻蝕(Etching)工藝”。

2023-08-10 15:06:10 506

506 在微電子制造中,刻蝕技術是制作集成電路和其他微型電子器件的關鍵步驟之一。通過刻蝕技術,微電子行業能夠在硅晶片上創建復雜的微觀結構。本文旨在探討刻蝕設備的市場規模以及行業內的競爭格局。

2023-08-02 10:01:08 623

623

刻蝕(Etching)的目的是在材料表面上刻出所需的圖案和結構。刻蝕的原理是利用化學反應或物理過程,通過移除材料表面的原子或分子,使材料發生形貌變化。

2023-08-01 16:33:38 3908

3908 電子發燒友網報道(文/周凱揚)在半導體制造的各路工序中,尤其是前道工序中,技術難度最大的主要三大流程當屬光刻、刻蝕和薄膜沉積了。這三大工藝的先進程度直接決定了晶圓廠所能實現的最高工藝節點,所用產品

2023-07-30 03:24:48 1556

1556

刻蝕和蝕刻實質上是同一過程的不同稱呼,常常用來描述在材料表面上進行化學或物理腐蝕以去除或改變材料的特定部分的過程。在半導體制造中,這個過程常常用于雕刻芯片上的細微結構。

2023-07-28 15:16:59 4140

4140 在設計MOS管開關電路時,就要充分了解MOS管的工作原理。下面咱們來詳細說明。

2023-07-20 09:40:17 1104

1104

Accura BE作為國產首臺12英寸晶邊刻蝕設備,其技術性能已達到業界主流水平。” Accura BE通過軟件系統調度優化和特有傳輸平臺的結合,可以提升客戶的產能。

2023-07-19 16:50:01 1140

1140 據介紹,在器件制造過程中,由于薄膜沉積、光刻、刻蝕和化學機械拋光等工藝步驟的大幅增長,在晶圓的邊緣造成了不可避免的副產物及殘留物堆積,這些晶邊沉積的副產物及殘留物驟增導致的缺陷風險成為產品良率的嚴重威脅。

2023-07-19 15:02:26 607

607 CMP 主要負責對晶圓表面實現平坦化。晶圓制造前道加工環節主要包括7個相互獨立的工藝流程:光刻、刻蝕、薄膜生長、擴散、離子注入、化學機械拋光、金屬化 CMP 則主要用于銜接不同薄膜工藝,其中根據工藝

2023-07-18 11:48:18 3030

3030

第一種是間歇式刻蝕方法(BOSCH),即多次交替循環刻蝕和淀積工藝,刻蝕工藝使用的是SF6氣體,淀積工藝使用的是C4F8氣體

2023-07-14 09:54:46 3214

3214

在前幾篇文章(點擊查看),我們一直在借用餅干烘焙過程來形象地說明半導體制程 。在上一篇我們說到,為制作巧克力夾心,需通過“刻蝕工藝”挖出餅干的中間部分,然后倒入巧克力糖漿,再蓋上一層餅干層。“倒入巧克力糖漿”和“蓋上餅干層”的過程在半導體制程中就相當于“沉積工藝”。

2023-06-29 16:56:17 830

830

需要使用我分享的EDA虛擬機:IC_EDA_ALL虛擬機(豐富版)詳細說明.

2023-06-29 10:21:17 2488

2488

在上一篇文章,我們介紹了光刻工藝,即利用光罩(掩膜)把設計好的電路圖形繪制在涂覆了光刻膠的晶圓表面上。下一步,將在晶圓上進行刻蝕工藝,以去除不必要的材料,只保留所需的圖形。

2023-06-28 10:04:58 843

843

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。其中,刻蝕工藝是光刻(Photo)工藝的下一步,用于去除光刻膠(Photo Resist

2023-06-26 09:20:10 816

816

中國科學院大學集成電路學院是國家首批支持建設的示范性微電子學院。為了提高學生對先進光刻技術的理解,本學期集成電路學院開設了《集成電路先進光刻技術與版圖設計優化》研討課。在授課過程中,除教師系統地講授

2023-06-20 10:51:43 335

335

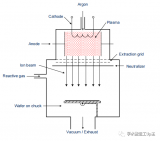

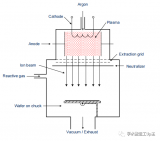

離子束蝕刻 (Ion beam etch) 是一種物理干法蝕刻工藝。由此,氬離子以約1至3keV的離子束輻射到表面上。由于離子的能量,它們會撞擊表面的材料。晶圓垂直或傾斜入離子束,蝕刻過程是絕對

2023-06-20 09:48:56 3989

3989

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-06-15 17:51:57 1177

1177

中國科學院大學集成電路學院是國家首批支持建設的示范性微電子學院。為了提高學生對先進光刻技術的理解,本學期集成電路學院開設了《集成電路先進光刻技術與版圖設計優化》研討課。在授課過程中,除教師系統地講授

2023-06-12 11:19:55 562

562

光刻工藝后,在硅片或晶圓上形成了光刻膠的圖形,下一步就是刻蝕。

2023-06-08 10:52:35 3320

3320

硅的堿性刻蝕液:氫氧化鉀、氫氧化氨或四甲基羥胺(TMAH)溶液,晶片加工中,會用到強堿作表面腐蝕或減薄,器件生產中,則傾向于弱堿,如SC1清洗晶片或多晶硅表面顆粒,一部分機理是SC1中的NH4OH

2023-06-05 15:10:01 1597

1597 集成電路前道工藝及對應設備主要分八大類,包括光刻(光刻機)、刻蝕(刻蝕機)、薄膜生長(PVD-物理氣相沉積、CVD-化學氣相沉積等薄膜設備)、擴散(擴散爐)、離子注入(離子注入機)、平坦化(CMP設備)、金屬化(ECD設備)、濕法工藝(濕法工藝設備)等。

2023-05-30 10:47:12 1131

1131

但是,HCl為基體的刻蝕溶液,會嚴重地侵蝕Ni(Pt)Si或Ni(Pt)SiGe,使金屬硅化物阻值升高。這就要求有一種刻蝕劑是無氯基體,而且對Ni(Pt)Si或Ni(Pt)SiGe無傷害、對金屬選擇性又高。這就是目前常用的高溫硫酸和雙氧水混合液

2023-05-29 10:48:27 1461

1461

上文FPGA IP之AXI4協議1_信號說明把AXI協議5個通道的接口信息做了說明,本文對上文說的信號進行詳細說明。

2023-05-24 15:06:41 669

669

本文主要介紹Vivado布線參數設置,基本設置方式和vivado綜合參數設置基本一致,將詳細說明如何設置布線參數以優化FPGA設計的性能,以及如何設置Vivado壓縮BIT文件。

2023-05-16 16:40:45 2956

2956

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。

2023-04-28 11:24:27 1073

1073

經過氧化、光刻、刻蝕、沉積等工藝,晶圓表面會形成各種半導體元件。半導體制造商會讓晶圓表面布滿晶體管和電容(Capacitor);

2023-04-28 10:04:52 532

532

本篇要講的金屬布線工藝,與前面提到的光刻、刻蝕、沉積等獨立的工藝不同。在半導體制程中,光刻、刻蝕等工藝,其實是為了金屬布線才進行的。在金屬布線過程中,會采用很多與之前的電子元器件層性質不同的配線材料(金屬)。

2023-04-25 10:38:49 986

986

我在使用 ESP32AT 命令模擬 BLE 鼠標時遇到 了一個問題,在 AT 指令集中查到了 AT+BLEHIDMUS=,,,指令參數的簡單說明, 但實際使用中不清楚< wheel

2023-04-24 09:08:43

等離子體均勻性和等離子體位置的控制在未來更加重要。對于成熟的技術節點,高的產量、低的成本是與現有生產系統競爭的關鍵因素。如果可以制造低成本的可靠的刻蝕系統,從長遠來看,可以為客戶節省大量費用,有可能

2023-04-21 09:20:22 1349

1349 壓力主要控制刻蝕均勻性和刻蝕輪廓,同時也能影響刻蝕速率和選擇性。改變壓力會改變電子和離子的平均自由程(MFP),進而影響等離子體和刻蝕速率的均勻性。

2023-04-17 10:36:43 1922

1922 為什么MFR4310E1MAE40型號的絲印是1M63J而不是0M63J?說明書里有詳細說明,怎么看?

2023-04-14 06:09:49

1、 B150外觀,詳細說明書可登錄官網2、 B150電氣特性:輸入電壓220V,功率1.5KW 3、 B150接線圖 4、 參數設置: 5、 參數清單

2023-04-10 10:26:43 0

0 金屬刻蝕具有良好的輪廓控制、殘余物控制,防止金屬腐蝕很重要。金屬刻蝕時鋁中如果 有少量銅就會引起殘余物問題,因為Cu Cl2的揮發性極低且會停留在晶圓表面。

2023-04-10 09:40:54 2330

2330 DRAM柵工藝中,在多晶硅上使用鈣金屬硅化物以減少局部連線的電阻。這種金屬硅化物和多晶硅的堆疊薄膜刻蝕需要增加一道工藝刻蝕W或WSi2,一般先使用氟元素刻蝕鈞金屬硅化合物層,然后再使用氯元素刻蝕多晶硅。

2023-04-07 09:48:16 2198

2198 不多說,上貨。Xilinx FPGA 開發流程及詳細說明本篇目錄1. 設計前準備2. 建立工程3. 輸入設計4. 綜合分析5. RTL仿真6. 鎖定管腳7. 布局布線8. 生成配置文件并下載9.

2023-03-30 19:04:10

FinFET三維器件也可以用體硅襯底制作,這需要更好地控制單晶硅刻蝕工藝,如CD、深度和輪廓。

2023-03-30 09:39:18 2459

2459 810-SPM3015T-1R5M

2023-03-29 22:11:27

SPM3020T-R47M

2023-03-29 22:06:43

SPM3020T-1R0M

2023-03-29 22:01:18

SPM5015T-2R2M

2023-03-29 22:01:04

SPM5015T-R47M

2023-03-29 22:00:37

SPM3015T-1R5M

2023-03-29 21:58:42

SPM4030T-3R3M

2023-03-29 21:56:24

本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白及打算進階提升的職業開發者都可以有

2023-03-29 21:28:27

SPM4020T-1R0M

2023-03-29 18:14:29

SPM5030VT-3R3M-D

2023-03-29 17:28:52

SPM5010T-3R3M-LR

2023-03-29 17:19:18

SPM10040XT-R33M

2023-03-29 16:27:51

SPM4030T-3R3M-HZ

2023-03-28 18:09:10

SPM5012T-2R2M-LR

2023-03-28 18:06:49

SPM3015T-1R0M

2023-03-28 14:29:57

SPM3015T-R47M

2023-03-28 14:23:08

SPM0687LR5H-1

2023-03-28 13:14:03

電子發燒友App

電子發燒友App

評論