PLUS153DN - Programmable logic arrays 18 × 42 × 10 - NXP Semiconductors

1970-01-01 08:00:00

實驗一、MAX+PLUSⅡ的基本應(yīng)用一 實驗?zāi)康?掌握MAX+PLUSⅡ的安裝及基本使用。2掌握MAX+PLUSⅡ基本輸入法—圖形輸入工具按鈕的使用。二 實驗設(shè)備

2009-03-13 19:15:01 3677

3677

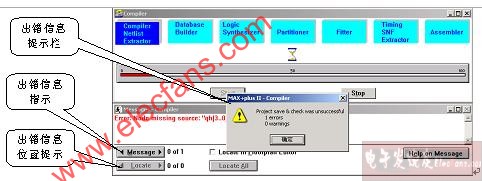

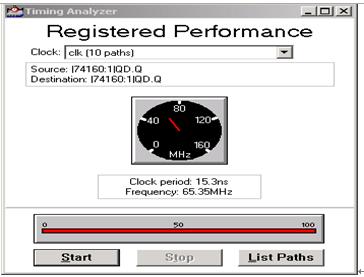

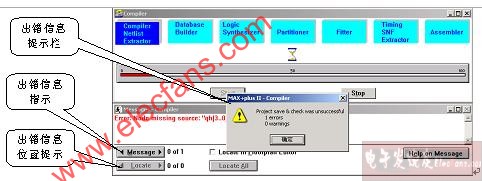

實驗三 MAX+PLUSⅡ的設(shè)計處理

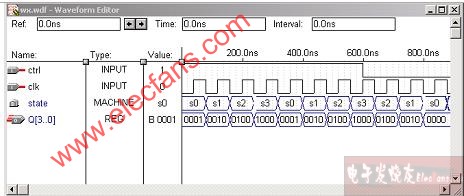

一 實驗?zāi)康?掌握MAX+PLUSⅡ的基本使用。2掌握MAX+PLUSⅡ的設(shè)計處理過程中的編譯和仿真。3 掌

2009-03-13 19:19:02 965

965

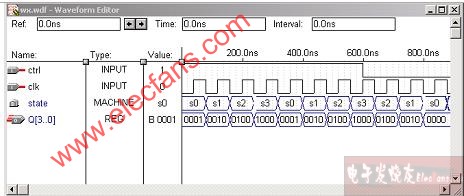

MAX+PLUSⅡ的基本應(yīng)用-波形輸入練習(xí)一 實驗?zāi)康?掌握MAX+PLUSⅡ的基本使用。2掌握MAX+PLUSⅡ基本輸入法—波形輸入法的使用。二 實驗設(shè)備與儀器

2009-03-13 19:16:05 2115

2115

Altera MAX+plus II 介紹

一、軟件功能簡介MAX+plusⅡ(Multiple Array and Programming Logic User System)開發(fā)工具是美國Altera 公司推出的一種EDA

2008-09-24 10:15:36 6502

6502

MAX+PLUS II軟件下載入口

2012-09-14 14:27:47 447

447 Max+plusⅡ是Altera公司提供的FPGA/CPLD開發(fā)集成環(huán)境,Altera是世界上最大可編程邏輯器件的供應(yīng)商之一。Max+plusⅡ界面友好,使用便捷,被譽為業(yè)界最易用易學(xué)的EDA軟件

2022-07-13 10:09:01 9

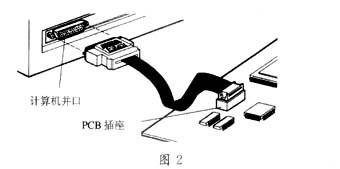

9 【摘 要】 介紹利用MAX+PLUSⅡ軟件對Altera公司的CPLD進行圖形設(shè)計、編譯以及在系統(tǒng)編程的基本方法和步驟。 關(guān)鍵詞:MAX+

2009-05-15 21:56:09 796

796

Max+Plus II簡易用戶使用入門指南

nMAX+PLUS II 為實現(xiàn)不同的邏輯功能提供了許多符號,如:圖元符

2008-09-11 15:09:05 3

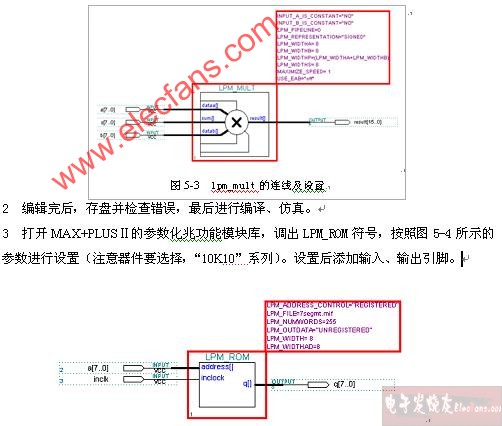

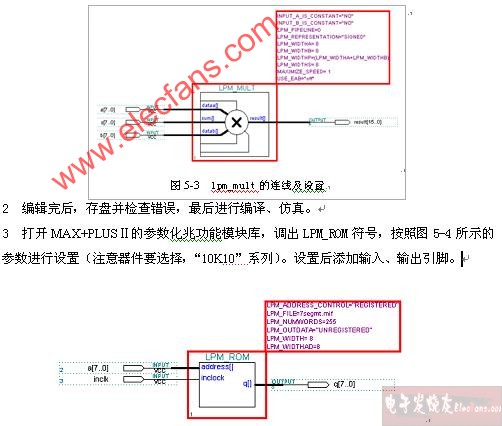

3 實驗五、MAX+PLUSⅡ的參數(shù)化兆功能模塊庫的使用一 實驗?zāi)康?進一步掌握MAX+PLUSⅡ參數(shù)化兆功能模塊庫的使用。2了解參數(shù)化兆功能模塊庫LP

2009-03-13 19:23:18 1359

1359

O 引言

MAX+PLUSⅡ開發(fā)系統(tǒng)是易學(xué)易用的完全集成化的設(shè)計開發(fā)環(huán)境。目前已發(fā)行10.0版本。該軟

2010-12-23 11:33:45 3162

3162

MAX+PLUSⅡ符號庫提供了很多基本圖元(Primitive, 又稱原語)供圖形設(shè)計文件調(diào)用, 這些圖元大體上可分為緩沖器、 寄存器、 輸入輸出端口、 邏輯門圖元等幾類。其中寄存器和組合

2010-06-07 10:26:59 3838

3838 Max+plusⅡ功能簡介 1 、原理圖輸入(Graphic Editor) MAX+PLUSII軟件具有圖形輸入能力,用戶可以方便的使用圖形編輯器輸入電路圖,圖中的元器件可以調(diào)用元件庫中元器件,除

2017-12-05 10:27:33 5

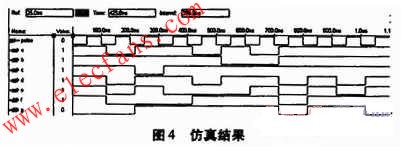

5 本文利用Max+ Plus 軟件對PCM30/ 32 路系統(tǒng)的發(fā)送端時序與幀結(jié)構(gòu)進行了仿真,由仿真結(jié)果可以清楚地發(fā)現(xiàn)該系統(tǒng)發(fā)端時序的規(guī)律

2011-03-28 10:55:27 2397

2397

Third Party EDA Tools Interface with Altera Max+Plus II

2022-08-01 11:11:45 5

5 VHDL語言 在第一章我們詳細(xì)介紹了VHDL語言,世界各大半導(dǎo)體公司開發(fā)的設(shè)計軟件都支持該語言,MAX+PLUS II軟件也支持該語言,下面介紹VHDL語言是如何在MAX+PLUS II軟件中使

2017-12-05 10:37:54 11

11 EDA技術(shù)以可編程邏輯器件FPGA和CPLD及其開發(fā)系統(tǒng)為硬件平臺,以EDA開發(fā)軟件如Max+PlusⅡ為開發(fā)工具,基于邏輯功能模塊的層次化設(shè)計方法設(shè)計數(shù)字系統(tǒng)。Max+PlusⅡ設(shè)計可采用原理圖

2017-09-07 15:37:45 8

8 2014-12-02 11:38:13 3

3 幫助讀者學(xué)會設(shè)計數(shù)字系統(tǒng)的硬件描述語言VHDL、并熟悉Altera公司產(chǎn)品和軟件Max+PlusⅡ。

2022-07-10 14:34:02 18

18 在第一章我們詳細(xì)介紹了VHDL語言,世界各大半導(dǎo)體公司開發(fā)的設(shè)計軟件都支持該語言,MAX+PLUS II軟件也支持該語言,下面介紹VHDL語言是如何在MAX+PLUS II軟件中使用的。

2022-08-01 14:30:45 4

4 Third Party EDA Tools Interface with Altera Max+Plus II

What Altera SupportAltera

2008-09-12 09:57:11 49

49 ?摘 要: 介紹了一種利用工具軟件MATLAB強大的數(shù)學(xué)功能來增強ALTERA公司的可編程邏輯器件設(shè)計軟件MAX+PLUSII的仿真功能、提高設(shè)計品質(zhì)的方法,有較強的針對性。

???

2009-06-20 11:45:15 813

813

Max+PlusⅡ是Altera公司提供的FPGA/CPLD開發(fā)集成環(huán)境,它可獨立完成簡單VHDL程序的編譯。然而,自動電梯控制程序是一個復(fù)雜的狀態(tài)機描述,Max+PlusⅡ無法獨立完成該程序的綜合編譯。

2018-05-27 11:38:00 3998

3998

2012-02-07 19:25:09 12

12 設(shè)計可改變方向的流水燈

一、 實驗?zāi)康模?、 熟練MAX+PLUS的操作。2、 熟練掌握VHDL語言3、 設(shè)計流水燈。

2009-06-28 00:07:44 3566

3566 2012-11-17 11:06:41 8

8 EDA 技術(shù)的基本特征是采用具有系統(tǒng)仿真和綜合能力的高級語言描述。它一般采用自頂向下的模塊化設(shè)計方法。但是由于所設(shè)計的數(shù)字系統(tǒng)的規(guī)模大小不一,且系統(tǒng)內(nèi)部邏輯關(guān)系復(fù)雜,如何

2011-09-16 21:27:10 1398

1398

本教材共分為9章 具體內(nèi)容如下.第一章 數(shù)字系統(tǒng)硬件設(shè)計的描述方法 第二章 VHDL設(shè)計描述的基本結(jié)構(gòu) 第三章 MMAX PLUS II VHDL的數(shù)據(jù)類型和操作運算 第四章 MAX PLUS II

2011-03-03 15:40:33 205

205 紅綠燈的控制計算變化時間程序源代碼:

-- MAX+plus II VHDL Example-- Conditional Signal Assignment-- Copyright

2010-02-08 17:14:30 43

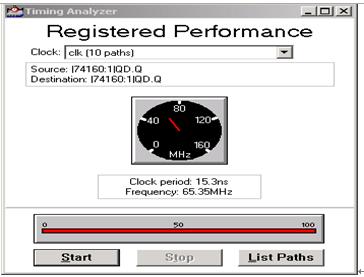

43 Multiple Clock System Design PLD設(shè)計技巧—多時鐘系統(tǒng)設(shè)計

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

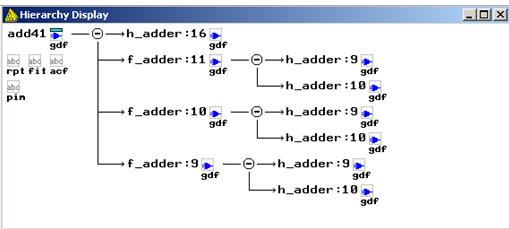

25 4.1 層次原理圖的設(shè)計概念4.2 層次原理圖的結(jié)構(gòu)4.3 層次原理圖的切換方法4.4 層次原理圖的設(shè)計

2010-08-18 08:39:15 46

46 LED數(shù)碼管滾動顯示

一、 實驗?zāi)康模?1、 熟練MAX+PLUS的基本操作。2、 練習(xí)VHDL語言編程。3、 實現(xiàn)LED數(shù)

2009-06-28 00:08:01 2205

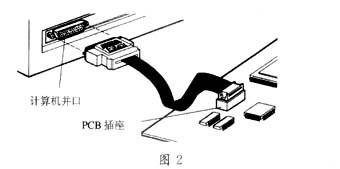

2205 摘 要:本文介紹了一種利用可編程器件CPLD實現(xiàn)CAN總線與微機之間接口的設(shè)計,說明了設(shè)計思想和設(shè)計方案,并給出了使用MAX+PLUS Ⅱ軟件圖形輸入法的邏輯設(shè)計和

2009-06-20 14:56:08 537

537 mif文件的創(chuàng)建與使用是在基于FPGA的系統(tǒng)設(shè)計中引入ROM的關(guān)鍵環(huán)節(jié)。對mif文件的創(chuàng)建與使用展開詳細(xì)討論,給出兩種可行性方法,并引入實例在MAX+PLUS Ⅱ環(huán)境下做了詳細(xì)的仿真

2010-12-13 17:47:29 41

41 摘要: 在簡單介紹算術(shù)編碼和自適應(yīng)算術(shù)編碼的基礎(chǔ)上,介紹了利用FPGA器件并通過VHDL語言描述實現(xiàn)自適應(yīng)算術(shù)編碼的過程。整個編碼系統(tǒng)在LTERA公司的MAX+plus Ⅱ軟

2009-06-20 13:40:24 969

969

Powerful of CLIQUE

What is CLIQUE ?Clique is an option which provided by Altera Max+Plus

2008-09-12 09:56:34 32

32 一、實驗?zāi)康? 初步了解大規(guī)模可編程器件(FPGA)設(shè)計的全 過程;2 掌握利用MAX PLUS II設(shè)計組合邏輯電路的方

2009-03-18 20:27:57 52

52 智慧感測時間變換交通標(biāo)志本專題由計時清除電路,訊號記憶電路,高頻脈波緩沖裝置等邏輯電路所組成,利用MAX+PLUS II平臺繪制電路,模擬結(jié)果。

2009-11-22 18:04:07 6

6 100進制計數(shù)器一、 實驗?zāi)康模?、 熟悉MAX+PLUS環(huán)境的基本操作。2、 掌握VHDL和原理圖的設(shè)計輸入方式。3、 設(shè)計100進制計數(shù)器。二、&

2009-06-28 00:07:21 7414

7414 小米目前已經(jīng)有了Note系列,小米再推出米6 Plus勢必會與其沖突。不過,熱衷大屏的米粉們也用不著失望,因為更大屏的小米Max2就要來了!根據(jù)網(wǎng)友爆料小米MAX 2很有可能在5月23日正式發(fā)布。

2017-05-15 11:15:46 1021

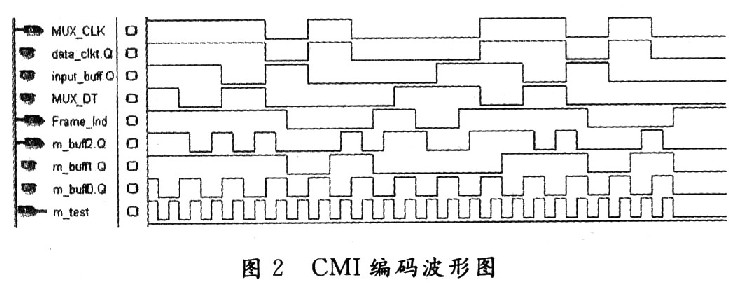

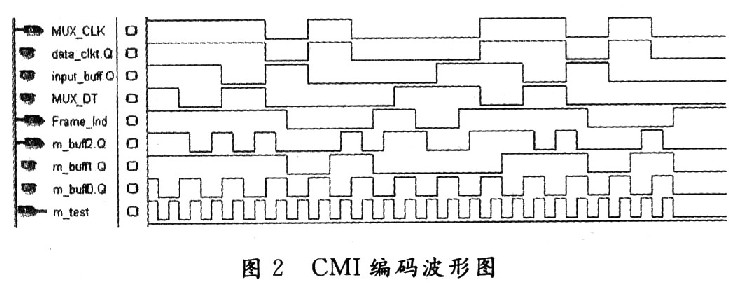

1021 0 引言

CMI碼是傳號反轉(zhuǎn)碼的簡稱,它是一種應(yīng)用于PCM四次群和光纖傳輸系統(tǒng)中的常用線路碼型,具有碼變換設(shè)備簡單、有較多的電平躍變,含有豐富的定時信息,便

2010-08-09 11:51:16 774

774

層次分析法:層次分析法:椅子的問題,席位分配問題,行走步長問題,實物交換模型。

2009-09-15 12:43:07 9

9 什么是層次型數(shù)據(jù)庫

層次型數(shù)據(jù)庫管理系統(tǒng)是緊隨網(wǎng)狀數(shù)據(jù)庫而出現(xiàn)的。現(xiàn)實世界中很多事物是按層次組織起來的。層次數(shù)據(jù)模型的

2009-06-17 07:37:30 2760

2760 層次化設(shè)計是指在一個大型設(shè)計任務(wù)中,將目標(biāo)層分解,在各個層次上進行設(shè)計的方法。

2019-11-19 07:08:00 4929

4929 隨著計算機與微電子技術(shù)的發(fā)展,電子設(shè)計自動化EDA領(lǐng)域已成為電子技術(shù)發(fā)展的主體,數(shù)字系統(tǒng)的設(shè)計正朝著速度快、容量大、體積小、重量輕的方向發(fā)展

2011-09-26 13:41:59 1933

1933

層次式原理圖是如何繪制的?

2022-01-04 15:44:09 9213

9213 周立功示波器ZLG ZDS4054Plus參數(shù)指標(biāo)型號 ZDS4054 Plus ZDS4034 Plus ZDS4024 Plus ZDS3054 Plus ZDS3034 Plus

2023-03-06 15:16:25

電子發(fā)燒友App

電子發(fā)燒友App

評論