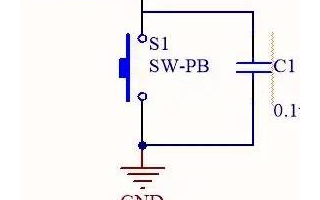

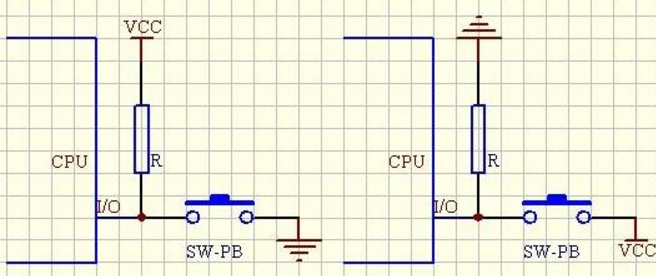

按鍵消抖通常的按鍵所用開關為機械彈性開關,當機械觸點斷開、閉合時,由于機械觸點的彈性作用,一個按鍵開關在閉合時不會馬上穩定地接通,在斷開時也不會一下子斷開。因而在閉合及斷開的瞬間均伴隨有一連串的抖動,為了不產生這種現象而作的措施就是按鍵消抖。

vhdl按鍵消抖程序一:延時性消抖

在本例子中,input是按鍵的輸入,output是消抖之后的按鍵輸出

是clk經歷8個上升沿之后就讓output輸出一個CLK周期的高電平!

本程序實例測試好用

library ieee;

use ieee.std_logic_1164.all;

entity PWlock is

port(clk: in std_logic;

input: in std_logic;

output: out std_logic

);

end PWlock;

architecture one of PWlock is

signal a:std_logic;

signal count:integer range 0 to 9;

begin

process(clk)

begin

if input=‘0’ then

count<=0;

elsif (clk‘event and clk=’1‘) then

if count=9 then

count<=count; --like while(1) in the C program

else

count<=count+1;

end if;

end if; --for elsif

if count=8 then

a<=’0‘;

else

a<=’1‘;

end if;

end process;

output<=a;

end one;

vhdl按鍵消抖程序二

一般按鍵延時在20ms左右,根據時鐘頻率決定你的計數范圍。程序非常簡單,但經常用到,對于FPGA初學者要好好學習這部分。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity reseter is

port(clk,reset_in:in std_logic; --按鍵按下時為0

reset_out:out std_logic:=‘0’);

end reseter;

architecture behav of reseter is

begin

PROCESS(clk,reset_in)

VARIABLE COUNT1 :INTEGER RANGE 0 TO 100000;

BEGIN

IF reset_in=‘0’ THEN

IF RISING_EDGE(clk) THEN

IF COUNT1<10000 THEN COUNT1:=COUNT1+1;

ELSE COUNT1:=COUNT1; END IF;

IF COUNT1<=9999 THEN reset_out<=‘1’;

ELSE reset_out<=‘0’; END IF;

END IF;

ELSE COUNT1:=0;

reset_out<=‘1’;

END IF;

END PROCESS ;

end behav;```

vhdl按鍵消抖程序三:計數器型消抖電路(一)

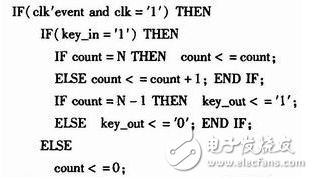

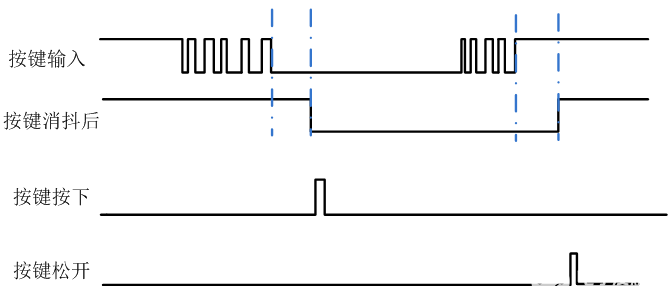

計數器型消抖電路是設置一個模值為(N+1)的控制計數器,clk在上升沿時,如果按鍵開關key_in=‘1’,計數器加1,key_in=‘0’時,計數器清零。當計數器值為2時,key_out輸出才為1,其他值為0時。計數器值為N時處于保持狀態。因此按鍵key_in持續時間大于N個clk時鐘周期時,計數器輸出一個單脈沖,否則沒有脈沖輸出。如果按鍵開關抖動產生的毛刺寬度小于N個時鐘周期,因而毛刺作用不可能使計數器有輸出,防抖動目的得以實現。clk的時鐘周期與N的值可以根據按鍵抖動時間由設計者自行設定。

圖1是N為3的波形仿真圖,當按鍵持續時間大于3個時鐘周期,計數器輸出一個單脈沖,其寬度為1個時鐘周期,小于3個時鐘周期的窄脈沖用作模擬抖動干擾,從圖1可以看出,抖動不能干擾正常的單脈沖輸出。

該方案的特點是能很好消除按鍵抖動產生的窄脈沖,還可以濾去干擾、噪音等其他尖峰波,但遇到脈寬大于N個Tclk時鐘周期的干擾、噪音等時會有輸出從而產生誤操作,而對于按鍵操作要求按鍵時間必須大于N個Tclk時鐘周期,否則按鍵操作也沒有輸出。

vhdl按鍵消抖程序四:計數器型消抖電路(二)

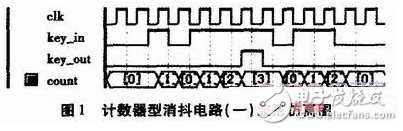

計數器型消抖電路(二)是控制計數器工作一個循環周期(N+1個狀態),且僅在計數器為0時輸出為“1”。電路設計了連鎖控制設施。在計數器處于狀態0時,此時若有按鍵操作,則計數器進入狀態1,同時輸出單脈沖(其寬度等于時鐘周期)。計數器處于其他狀態,都沒有單脈沖輸出。計數器處于狀態N時,控制en=‘0’,導致計數器退出狀態N,進入狀態0。計數器能否保持狀態0,取決于人工按鍵操作,若按鍵key_in=‘1’,控制en=‘1’(計數器能正常工作),key_in=‘0’,計數器狀態保持。顯見計數器處于狀態0,人工不按鍵,則計數器保持狀態0。

主要程序結構如下:

圖2是N為7的波形仿真圖。在計數器狀態為0時,key_in有按鍵操作,計數器開始連續計數直到計數器狀態為0;計數器狀態為1-7時,key_in任何操作對計數器工作無影響,計數器在狀態為1時,輸出一個單脈沖,脈沖寬度為1個時鐘周期。

該設計方案的特點是能很好消除按鍵抖動產生的連續脈沖,對按鍵時間沒有要求,缺點是在計數器狀態為0時,遇到干擾、噪音等時會有輸出,從而產生誤操作。

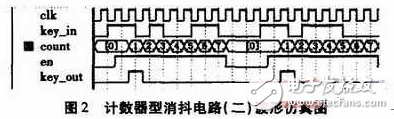

vhdl按鍵消抖程序五:D觸發器型消抖電路

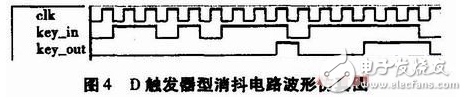

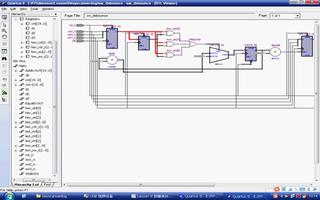

D觸發器型消抖電路設計了三個D觸發器與一個三輸入與門。三個D觸發器串行連接,其Q輸出端分別與三輸入與門的輸入端連接,D觸發器型消抖電路RTL電路如圖3所示。

主要程序結構如下:

圖4為D觸發器型消抖電路波形仿真圖,由圖可見,當按鍵操作時間大于或等于clk時鐘周期的3倍時,輸出一個正脈沖,正脈沖的寬度比key_in少2個clk時鐘周期。

D觸發器型消抖電路與計數器型消抖電路(一)相似,計數器型消抖電路(一)輸出脈沖寬度是固定的,D觸發器型消抖電路輸出脈沖寬度隨著按鍵操作時間長短變化。

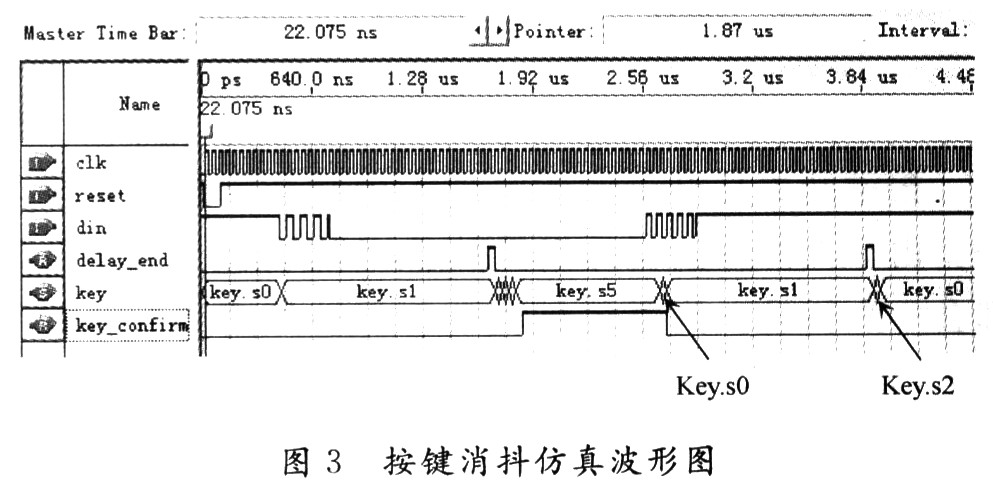

vhdl按鍵消抖程序六:狀態機型消抖電路

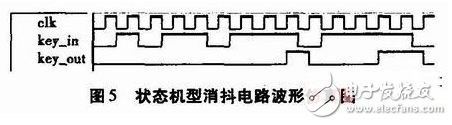

狀態機型消抖電路采用有限狀態機的設計方法來描述與實現,狀態機有S0,S1,S2三種狀態,在S0狀態下key_out輸出為低電平,并以clk時鐘信號的頻率采樣按鍵輸入信號,如果key_in=‘0’,則保持在S0狀態,并繼續采樣按鍵輸入信號的狀態,如果key_in=‘1’,則轉入S1狀態;在S1狀態下key_out輸出仍為低電平,繼續采樣按鍵輸入信號的狀態,如果key_in=‘1’,則轉入S2狀態,如果key_in=‘0’則轉入S0狀態;在S2狀態下繼續采樣按鍵輸入信號的狀態,如果key_in=‘1’,則保持在S2狀態,key_out輸出正脈沖,如果key_in=‘0’,則轉入S0狀態,key_out輸出低電平。

主要程序結構如下:

圖5為狀態機型消抖電路波形仿真圖,由圖可見,該狀態機型消抖電路與D觸發器型消抖電路仿真結果一致。

vhdl按鍵消抖程序七

assign key_done = (dout1 | dout2 | dout3); //按鍵消抖輸出

always @(posedge count[17])

begin

dout1 <= key_in;

dout2 <= dout1;

dout3 <= dout2;

end

always @(negedge key_done[0])

begin

keyen = ~keyen; //將琴鍵開關轉換為乒乓開關

end程序中所用的方法是不斷檢測按鍵值。每當Count[17]上升沿到來,就進行檢測輸入信號。其中dout1,dout2,dout3分別為當前、上個Count[17]上升沿、上上個Count[17]上升沿輸入數值。正常情況下為1,假如連續三次為0,三個信號作或運算,使得key_done信號為0,出現下降沿,這樣就認為是有按鍵。

電子發燒友App

電子發燒友App

評論