據(jù)說SpinalHDL相比chisel更具優(yōu)勢,這讓我有了興趣,今天開始安裝搭建。平常用的linux系統(tǒng)的,但是Intel IDEA安裝在Ubuntu上的時候總是卡的不行,就放棄了,其實

2021-08-24 14:43:09 8188

8188

SpinalHDL是基于Scala全新的硬件描述語言,解決了不少Verilog等傳統(tǒng)HDL語言的痛點,可以快速的完成某些IP的開發(fā),和完美的融入現(xiàn)有的開發(fā)流程。 誠然SpinalHDL的學習路線

2023-07-27 09:29:39 766

766

,這個一步需要勾選紅框中的這一項;

對應的IDEA中的插件安裝Scala和SBT:

Scala插件安裝:

SBT插件安裝

2.2、JDK安裝

直接到JDK官網(wǎng)下載安裝包下載即可:

JDK的安裝沒有

2024-01-21 10:52:10

SpinalHDL中Bundle與SystemVerilog中的packed struct很像,在某些場景下,與普通數(shù)據(jù)類型之間的連接賦值可以通過asBits,assignFromBits來實現(xiàn)

2022-10-18 14:22:42

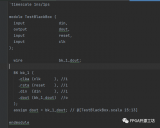

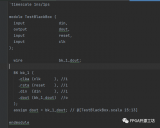

對于仿真信號的驅(qū)動,在SpinalHDL里通過“#=”方法實現(xiàn):值得注意的是當我們的設計里有一個輸入信號為:val a=in UInt(32 bits)在進行仿真信號驅(qū)動時,下面的寫法會報錯的:a#

2022-07-27 14:37:46

的Stream總線最近做系統(tǒng)總線的定義,模塊之間存在著大量的握手交互,在SpinalHDL中這類總線往往繼承于SpinalHDL中的Stream。以下面的總線定義為例:先來說說自己為什么這么來定義總線

2023-01-31 16:38:03

發(fā)送一幀總線的最后一拍時重新拉高waitPacket。可以看出,整體的設計思路并不難,我們用Verilog也可以很容易實現(xiàn),但SpinalHDL好處在于能夠?qū)⒐δ芊庋b抽象成庫函數(shù)供我們快速調(diào)用而不是

2022-07-21 14:31:07

安裝。軟件安裝所有軟件安裝在 X:\\SpinalHDL 目錄下即可所有軟件安裝過程中,把 path 選項都勾選上;使用sbt國內(nèi)鏡像。 在個人用戶目錄下新建.sbt文件夾,在文件夾內(nèi)創(chuàng)建

2022-10-17 15:33:34

在SpinalHDL的測試代碼里也可以起多個,不過其為協(xié)程。SpinalHDL的仿真庫已經(jīng)幫我們封裝好了底層協(xié)程的處理,兩個協(xié)程之間的通信(類似systemVerilog中的mailbox)我們可以

2022-07-25 15:09:03

在Bits的基礎上,SpinalHDL提供了UInt、SInt數(shù)據(jù)類型,從而能夠進行有符號/無符號數(shù)操作。變量定義/初始化UInt/SInt的初始化與Bits類型相似:邏輯操作符UInt/SInt

2022-07-14 14:45:15

設計。以下是SpinalHDL檢查的簡要概括: 重復賦值 時鐘域交叉 層次化違例 組合邏輯環(huán)路 Latch 未驅(qū)動的信號 位寬不匹配 得不到的switch生命 在每個SpinalHDL

2022-10-24 15:37:28

SpinalHDL中的switch在之前的文章中曾提到過SpinalHDL中switch的使用:通常情況下,switch對應著我們?nèi)粘erilog代碼中的case。像下面的代碼:其生成的RTL代碼

2022-07-06 10:59:58

,data1兩個UInt信號以及為該方法定義了一個sum求和函數(shù),文中針對該總線進行功能描述。而就SpinalHDL中關(guān)于代碼描述的一些建議,在之前的文章中也有提及:《SpinalHDL代碼組織結(jié)構(gòu)之

2022-06-28 15:21:19

聲明時,master/slave是另一種選擇,它需要我們在定義類時繼承擴展Bundle及Imaster Slave:這里我們繼承了ImasterSlave,則需要我們在class中實現(xiàn)asMaster

2022-07-21 14:20:23

,在SpinalHDL例例化一個帶層次結(jié)構(gòu)的RTL代碼(RTL代碼本身沒什么意義,主要展示帶層次結(jié)構(gòu)的RTL代碼在SpinalHDL中設計仿真的實現(xiàn))。RTL代碼分兩個文件:SpinalHDL IP

2022-06-22 14:59:25

時會同時生成用于生成相應ILa IP的tcl腳本,從而能夠輕松的在SpinalHDL中實現(xiàn)對待跟蹤波形信號的抓取實現(xiàn)。下面一段代碼展示了如何在SpinalHDL里添加ILA:在上述代碼中。就像聲明一個類對象

2022-06-22 14:37:13

switch方法用于實現(xiàn)Verilog里case語句的實現(xiàn):看起來似乎和Verilog里的差不多,但SpinalHDL基于Scala語言,可借助高級語言進行方便的代碼構(gòu)建:在SpinalHDL里,我們

2022-06-22 14:25:27

下午微信群里有個小伙伴問了這么一道題:將一個為UInt(128 bits)的Stream接口連接到一個UInt(32 bits)的StreamFiFo上,在SpinalHDL里有沒有什么好的方式實現(xiàn)

2022-07-27 14:52:09

快速連接器在液體冷卻中的作用是什么?如何確保連接器穩(wěn)定性?要注意哪些因素?

2021-04-13 06:34:53

快速連接器在液體冷卻中有什么作用?

2021-06-07 06:47:48

快速Gabor濾波算法在虹膜識別系統(tǒng)中的應用是怎樣的?Gabor濾波器的實現(xiàn)

2021-04-07 07:00:17

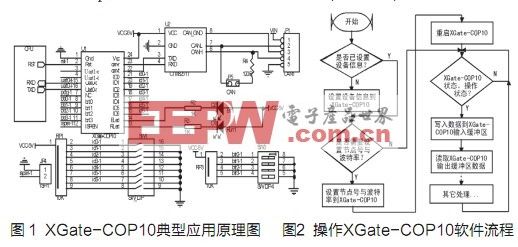

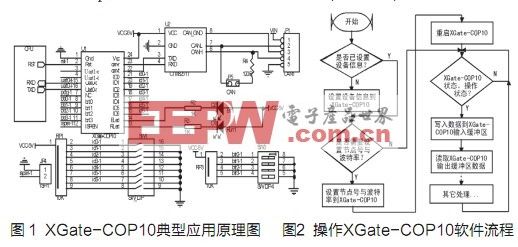

CAN總線快速入門

2012-08-07 16:07:56

CAN總線快速入門

2012-08-20 19:20:24

582M 藍牙鍵盤項目,藍牙處于連接狀態(tài)下,我想快速斷開當前連接,并改地址進入廣播狀態(tài),但藍牙總進入Connected Advertising..,要等好久才會Advertising..。。在不擦除綁定信息的情況,有什么辦法可以快速進入Advertising..嗎??

2022-08-01 07:34:25

在現(xiàn)代電子系統(tǒng)中,有為數(shù)眾多的 IC 需要進行相互之間以及與外界的通信。為了簡化電路的設計,Philips 公司開發(fā)了一種用于內(nèi)部 IC 控制的簡單的雙向兩線串行總線 I2C

2018-09-29 09:37:11

數(shù)據(jù)傳輸是通過ISA總線控制芯片組中的兩個級聯(lián)8237 DMAC來實現(xiàn)的。這種DMA機制也稱為“標準DMA”(standard DMA)。標準DMA有時也稱為“第三方DMA”(third-party

2019-07-01 08:10:07

LabvIEW中如何實現(xiàn)大容量數(shù)據(jù)的快速讀取呢?我試過將數(shù)據(jù)存放在excel表中,然后用讀取電子表格VI去讀取,但是,分析下來,要花1s左右,有沒有更快的方法呢?我想控制在200、300毫秒之內(nèi)

2014-10-08 21:25:42

RS-485總線在工業(yè)設計中的應用485總線的工業(yè)設計應用指南 &

2009-09-04 08:35:45

方便的實現(xiàn)上述電路邏輯:在上面的代碼中,14~18行例化了一個Mem并實現(xiàn)其寫端口邏輯,20行通過Mem提供的streamReadSync函數(shù)實現(xiàn)對Mem的讀操作(接收一個Stream總線作為讀請求

2022-06-22 14:44:29

來源于《SpinalHDL—Area》一文,讀者可參考該篇文章研究該實現(xiàn)方式。SimEnv對于仿真而言,最好的形式便是仿真驅(qū)動與測試case分層設計,在這里,通過采用類繼承的形式定義一個addInstSim的類來實現(xiàn)一個

2022-07-28 15:12:32

1 CHI的片上互聯(lián)總線片上互聯(lián)是將SoC內(nèi)部不同模塊連接起來的結(jié)構(gòu),如前文提到過的硬件系統(tǒng)結(jié)構(gòu)中, Interconnect Bus就是片上互聯(lián)。需要支持模塊之間的高速數(shù)據(jù)傳輸,高效地互聯(lián)互通

2022-06-29 16:28:32

Spinal狀態(tài)機在使用SpinalHDL的狀態(tài)機時,生成的Verilog代碼里狀態(tài)機中狀態(tài)的定義全都是由宏定義來實現(xiàn)的。在真實的工程里,我們很少會講所有的Verilog代碼放在一個文件里。往往是一

2022-07-08 16:13:01

在做RTL仿真驗證時,覆蓋率收集往往是我們在驗證中需要注意的地方,本篇就SpinalHDL中的驗證覆蓋率收集做一個簡單說明。sbt配置在SpinalHDL里進行仿真驗證時,我們的待測試代碼會生

2022-06-24 15:56:45

驅(qū)動 cocotb仿真的實現(xiàn)機制和SpinalHDL原理無差。在cocotb中,對于信號的賦值,也和SystemVerilog提供了兩種類似的方式:sig.value

2022-06-24 16:34:49

SpinalHDL和Chisel都是基于scala來實現(xiàn)的,而在SpinalHDL的example里,偶然看到一個apply的有趣用法。“神奇”的邏輯,"奇葩"的寫法偶然看到一

2022-07-19 15:08:36

至少為1μs(參見下圖五)。 圖五:主控MCU讀時隙 結(jié)語:本文只是通過以MY18E20為例,介紹單總線傳感器在實際應用中,硬件設計和通訊時序的相關(guān)問題。明白了其實現(xiàn)原理,其他的就可以觸類旁通,供讀者參考。

2020-07-08 17:22:05

USB(通用串行總線)是一種新的數(shù)據(jù)通信接口方式,它使得外圍沒備到計算機的連接更加高效、便利。USB接口不僅具有快速、即插即用、支持熱插拔的特點,而且能同時連接多達127個外部設備,可以有效地

2021-01-11 06:56:37

系統(tǒng)中DCS總線接口設備的設計與實現(xiàn)。2 概述MCGS工控組態(tài)軟件開發(fā)工具基于Windows操作平臺,支持快速構(gòu)造、生成工業(yè)設備驅(qū)動,具有良好的擴充能力。具體地說,MCGS用Active DLL構(gòu)件

2018-12-18 10:11:22

)→Turn_ar→Idle,突發(fā)數(shù)據(jù)交易,讀交易則插入讀等待狀態(tài)R_wait.若從設備提出終止,則插入L_data和Backoff狀態(tài)與主設備斷開連接;若是主設備提出終止則正常的結(jié)束總線交易。在設計中,配置

2019-05-29 05:00:02

1 所有軟件安裝在C:\\SpinalHDL根目錄下即可2 所有軟件安裝過程中,把path選項都勾選上3 仿真需要使用GTKWave+Verilator,安裝MSYS2軟件之后,打開用戶終端輸入如下

2022-10-24 15:40:49

如何實現(xiàn)一條can總線上連接許多can設備?

2021-11-15 06:37:44

CANScope分析儀是什么?如何快速判斷CAN總線的故障節(jié)點?

2021-05-20 06:44:41

前言在安裝完成Verilator、GtkWave后,我們即可在IDEA里通過SpinalHDL提供的仿真接口來對我們的設計進行仿真。在《SpinalHDL—仿真環(huán)境》一文中已提到SpinalHDL下

2022-07-26 16:59:25

currentState如果你去看過SpinalHDL中StateMachine,那么你會發(fā)現(xiàn)其實現(xiàn)里通過stateReg來標記當前狀態(tài),而這里通過addPrePopTask中將其賦值到

2022-06-30 15:19:03

打開過Bundle的代碼實現(xiàn),你就會發(fā)現(xiàn)這里面有一個assignAllByName的方法實現(xiàn)很符合我們的需求:我們在Bundle中聲明的信號接口都存儲于elements中,elements的定義形式為

2022-10-11 15:14:37

代碼描述了,SpinalHDL提供對仿真的支持,而基于Scala這門語言,在構(gòu)建仿真環(huán)境時擁有者更絲滑的體驗。這里完整的仿真環(huán)境搭建代碼如如下所示:仿真執(zhí)行搭建完環(huán)境后,仿真的執(zhí)行就很簡單了:讓仿真飛一會兒:仿真波形可以通過gtkwave來觀看:原作者:玉騏

2022-07-20 14:38:07

主站在總線一端點 圖所示的是一般的Profibus總線連接方法,主站位于總線的一端,終端電阻打ON。 然后依次連接后面的站點,中間的站點終端電阻打OFF,最后面的站點終端電阻打

2020-12-02 11:51:20

在航空電子綜合化系統(tǒng)中,快速、有效的數(shù)據(jù)傳輸對整個航空電子系統(tǒng)的性能有很大影響,因此數(shù)據(jù)總線被稱為現(xiàn)代航空電子系統(tǒng)的“骨架”。ARINC429是航空電子系統(tǒng)之間最常用的通信總線之一。要在計算機上實現(xiàn)與機載設備的ARINC429總線數(shù)據(jù)通信,必須實現(xiàn)429總線與計算機總線之間的數(shù)據(jù)傳輸。

2019-08-19 07:24:53

呢?在SpinalHDL中,對于總線連接時位寬的檢查是十分嚴格的,這里直接使用"<>"或者“>>”方法來進行連接顯然是不行

2022-12-12 16:31:03

最新總線技術(shù)在儀器控制與連接方面的遠景簡介過去二十多年間﹐科學家與工程師已在自動化儀器系統(tǒng)中廣泛使用IEEE 488 和通用接口總線GPIB。當大眾化電腦技術(shù)進入測試與測量領域﹐并在連接儀器

2009-10-23 18:35:10

1、基于SpinalHDL的多端口仲裁的設計》最低優(yōu)先級調(diào)度 SpinalHDL中關(guān)于roundRobin的實現(xiàn)背后原理其實一開始困惑挺久,后來方慢慢理解。在講解roundRobin之前,先來

2022-06-10 17:12:07

米)。 (5)傳輸媒介和連接方式 完整的現(xiàn)場總線系統(tǒng),除了構(gòu)成網(wǎng)絡的范圍(即最大距離)是一個重要的指標外,能否在總線系統(tǒng)中實現(xiàn)不同總線段間采用不同的傳輸媒介,也是重要的因素。它使系統(tǒng)的構(gòu)成

2012-02-01 13:48:53

現(xiàn)場總線在自動化系統(tǒng)中的應用 傳統(tǒng)方式現(xiàn)場級設備與控制器之間連接采用一對一所謂I/O接線方式傳遞4-20mA或24VDC信號 現(xiàn)場總線技術(shù)主要特征是采用數(shù)字式通信方式取代設備級的4-20mA(模擬量/24VDC 開關(guān)量信號使用一根電纜連接所有現(xiàn)場設備

2009-11-17 09:31:02

無論是Amba總線還是其他類總線,握手與分發(fā)總是無處不在。在SpinalHDL中,Stream的抽象提取個人認為絕對是一個精彩的操作。SpinalHDL的lib中針對Stream也提供了大量的組件

2022-07-07 17:18:27

; this}對于每個待連接的slave端口,這里轉(zhuǎn)換成列表存放于translatedSlaves中。之所以將slave端口轉(zhuǎn)換成列表的形式,在于當我們傳入的slave端口是axi4時,在

2022-08-09 14:40:34

信號的不同bit賦值給不同的信號,這種拼接方式可以在SpinalHDL中按照如下的形式進行書寫:case class demo() extends Component{val

2022-11-18 15:21:04

不做過多的講解(小伙伴可以自行下載AMBA總線協(xié)議規(guī)范或者翻看網(wǎng)絡上AXI4總線協(xié)議相關(guān)文章)。在SpinalHDL中,關(guān)于Axi4總線,包含了配置和實現(xiàn)兩塊內(nèi)容,其內(nèi)容均在

2022-08-02 14:28:46

UVM里面有前門訪問,后門訪問的概念。前門訪問無非通過總線來實現(xiàn)寄存器/Mem的訪問。而當在一些仿真中為了減少通過總線進行配置下發(fā)所需的時間,那么后門訪問就非常便捷了,它使得無需通過總線即可修改

2022-07-04 15:19:10

BlackBox在之前的文章中,曾介紹過如何封裝兼容別人的RTL代碼:SpinalHDL——集成你的RTL代碼整體的思路還是簡潔明了的,相信讀完后照著做很快就能上手。這對于保持設計的兼容性及混合

2022-06-29 16:02:13

的具備阻塞實現(xiàn)便捷性。正式基于上面的這些思路(這種設計思想也是深得我心),SpinalHDL中的StreamFifo便由此而來:無論是出口(pop)還是入口(push),均抽象為Stream接口,push

2022-06-30 15:28:00

各位大佬好

我想問下,平時我們使用的藍牙遙控器是如何實現(xiàn)打開電視,就能快速連上的,普通的藍牙配對連上至少需要五六秒鐘的,這個只需要點一下就能喚醒馬上能使用了,請問這種一般是如何實現(xiàn)的。

2023-09-19 09:15:51

》踩到的坑在很早之前,曾寫過如何在SpinalHDL中例化之前用Verilog/SystemVerilog所寫的代碼,可參照文章《[SpinalHDL——集成你的RTL代碼]》一文。在

2022-08-31 14:58:31

)及兼顧代碼盡可能復用的準則,SpinalHDL里設計了Area的概念。通過類擴展集成Area,可以有效的避免上述問題。介紹Area之前,先介紹一個概念:在Scala中,參數(shù)的傳遞均為引用類型,而我們定義

2022-07-22 14:22:23

到ack為低電平即可處理新的任務。 寫在最后 關(guān)于跨時鐘域處理在處理上相對來講還是一個易錯點,其處理也是新學者需要好好把握的。SpinalHDL中的源代碼還是很值得一讀的。一方面

2022-06-30 15:11:08

介紹采用Altera 公司的可編程器件實現(xiàn)串口通信的星型連接,扼要地介紹四路UART 串口通信網(wǎng)絡的星型連接的硬件和軟件的實現(xiàn)。在實現(xiàn)多點串口通信時,星型連接比總線型連接具有

2009-05-15 15:24:57 38

38 在VXI總線系統(tǒng)中,為了能夠獲得大量實時數(shù)據(jù),需要利用CAN總線快速可靠的傳輸數(shù)據(jù)的性能,設計一種混合VXI總線和CAN總線的系統(tǒng)。在這種混合系統(tǒng)中要實現(xiàn)CAN總線上各個節(jié)點采集

2009-07-06 16:27:58 13

13 基于CANopen協(xié)議從站設備快速實現(xiàn)方法

CANopen協(xié)議作為CAN總線的應用層協(xié)議,擁有復雜的網(wǎng)絡管理、實時過程數(shù)據(jù)對象、服務數(shù)據(jù)對象、預定義連接和特殊功能對象等基

2010-05-23 12:03:20 1440

1440

Xilinx FPGA工程例子源碼:實現(xiàn)基于spartan3與CAN總線連接后的的汽車時速的模擬仿真

2016-06-07 15:07:45 9

9 CAN總線快速入門

2016-12-13 17:15:19 22

22 進行信息傳送的公共通道,常用外部總線有RS-232C、RS485和IEEE-488、USB、CAN 等現(xiàn)場總線、快速以太網(wǎng)、WIFI總線等。

2017-10-20 17:47:42 2

2 “快速連接器”是一個廣泛的工業(yè)產(chǎn)品配件名詞,分為液壓管道快速連接器和挖掘機快速連接器。這里是指挖掘機快速連接器(也叫快換接頭、快速連接頭),快速連接器能在挖掘機上迅速安裝各種配置件(挖斗、松土器、破碎錘、液壓剪等),能擴大挖掘機使用范圍,能明顯的節(jié)約時間,提高工效。

2018-06-03 18:48:00 1140

1140 廣成科技GCAN-204型號Modbus RTU轉(zhuǎn)CAN模塊可以實現(xiàn)將Modbus主站與CAN總線連接。

2018-10-25 11:29:57 7495

7495 聊一聊在SpinalHDL里時鐘域中時鐘的定制與命名。 相較于Verilog,在SpinalHDL里,其對時鐘域有著更細致的描述,從而也能夠更精細的控制和描述。而對于時鐘域,我們往往關(guān)系的是: 時鐘

2021-03-22 10:14:37 1854

1854 在SpinalHDL里,其Libraries里提供了關(guān)于總線相關(guān)的庫。包含AMBA3、AMBA4、AVALON等總線類型,并提供了bus slave factory工具

2021-04-08 17:28:26 2839

2839

最近偶爾需要用到SPI模塊。正巧看到SpinalHDL中所提供的SPI-Master設計。看完之后尤為佩服如此簡潔而又全面的設計方式。本篇不對SPI協(xié)議進行講解,僅針對SpinalHDL中的SpiMasterCtrl模塊做使用說明。

2021-04-19 09:58:14 3283

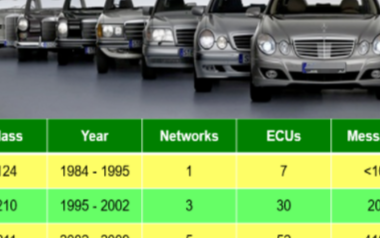

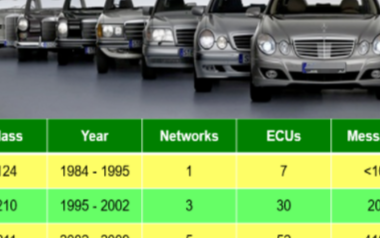

3283 所有控制儀表的相關(guān) CAN 總線,例如:舒適系統(tǒng)數(shù)據(jù)總線,都圍繞在中心點。 插頭連接 CAN 總線中心點。

2021-04-20 09:36:53 22

22 不點藍字,何來故事? 學習SpinalHDL已有近半年,其誠然小眾,但“小家碧玉”未嘗不是絕代佳人。出坑Verilog遙想當年本科之時畫過電路PCB、玩兒過單片機、PLC,亦學...

2021-12-20 18:56:13 3

3 CAN總線的應用越來越廣泛,工程師在不同工況下,如何快速實現(xiàn)故障定位呢?本文將介紹CAN網(wǎng)絡故障帶來的麻煩,以及快速定位故障的幾種方法,可以幫您快速完成判斷并進行選擇。

2022-03-10 09:09:47 3517

3517

針對SpinalHDL中的兩大類型Reg、Wire,來梳理下在SpinalHDL中的對應關(guān)系及聲明形式。

2022-07-03 11:02:05 1096

1096 每一個做數(shù)字邏輯的都繞不開跨時鐘域處理,談一談SpinalHDL里用于跨時鐘域處理的一些手段方法。

2022-07-11 10:51:44 1309

1309 通過bus slave factory,我們可以方便地實現(xiàn)寄存器讀寫,其提供了一系列寄存器讀寫方法。這里列舉幾個常用的方法(完整的方法列表可參照SpinalHDL-Doc):

2022-08-05 09:57:46 776

776 本篇文章來源于微信群中的網(wǎng)友,分享下在SpinalHDL里如何絲滑的運行VCS跑Vivado相關(guān)仿真。自此仿真設計一體化不是問題。

2022-08-10 09:15:17 2038

2038 書接上文,趁著今天休假,采用SpinalHDL做一個小的demo,看看在SpinalHDL里如何優(yōu)雅的實現(xiàn)Sobel邊緣檢測。

2022-08-26 08:59:48 963

963 UVM里面有前門訪問,后門訪問的概念。前門訪問無非通過總線來實現(xiàn)寄存器/Mem的訪問。而當在一些仿真中為了減少通過總線進行配置下發(fā)所需的時間,那么后門訪問就非常便捷了,它使得無需通過總線即可修改寄存器/Mem的值。今天,就來看看在SpinalHDL的仿真中我們可以使用的后門讀寫操作。

2022-09-02 09:29:22 772

772 SpinalHDL中Bundle與SystemVerilog中的packed struct很像,在某些場景下,與普通數(shù)據(jù)類型之間的連接賦值可以通過asBits,assignFromBits來實現(xiàn)。

2022-10-17 09:51:40 947

947 作為SpinalHDL語法篇的第一節(jié),我們也從最簡單的開始。

2022-10-31 10:56:08 903

903 在之前寫Verilog時,位拼接符是一個很常見的東西,今天來看下在SpinalHDL中常見的位拼接符的使用。

2022-11-12 11:34:23 838

838 最近做系統(tǒng)總線的定義,模塊之間存在著大量的握手交互,在SpinalHDL中這類總線往往繼承于SpinalHDL中的Stream。以下面的總線定義為例。

2022-12-07 21:03:02 291

291 在SpinalHDL中使用之前已有的Verilog等代碼的時候需要將這些代碼包在一個BlackBox里面,但是如果這些代碼里面有時鐘和復位,我們需要怎么將時鐘和復位端口和SpinalHDL中已有的時鐘域連接起來呢?

2023-05-04 11:13:14 489

489

作為SpinalHDL語法篇的第一節(jié),我們也從最簡單的開始。

Bool類型定義

2023-05-05 16:01:32 362

362 實現(xiàn)一個在ARM中通過APB總線連接的UART模塊(Universal Asynchronous Receiver/Transmitter),包括設計與驗證兩部分。

2023-06-05 11:48:38 953

953

昨晚看SpinalHDL的Issues,其中有一個關(guān)于性能提升的case 吸引到了我,嘗試實驗到深夜,測試下在SpinalHDL以及cocotb下的性能優(yōu)化手段。

2023-08-06 17:10:34 370

370

快速實現(xiàn)EG網(wǎng)關(guān)串口連接豐煒PLC

2023-11-27 17:28:05 228

228

中扮演著重要的角色。下面將詳細介紹光纖快速連接器的作用、安裝使用以及與冷接子的區(qū)別。 一、光纖快速連接器的作用 光纖快速連接器主要用于連接光纖的兩端,實現(xiàn)光信號的傳輸。連接器的作用是提供機械接合,確保光信號能夠穩(wěn)定

2023-12-27 15:44:46 622

622 CAN總線星型連接器及特點? CAN總線星型連接器是一種用于連接CAN總線網(wǎng)絡的設備,它具有一些獨特的特點和優(yōu)勢。本文將詳細介紹CAN總線星型連接器的工作原理、結(jié)構(gòu)特點、適用范圍以及與其他類型連接

2024-01-04 16:59:25 806

806 之前有系列文章介紹了SpinalHDL中Pipeline的使用,最近在一個功能模塊中真實的使用了這個lib。

2024-03-17 17:31:36 474

474

電子發(fā)燒友App

電子發(fā)燒友App

評論