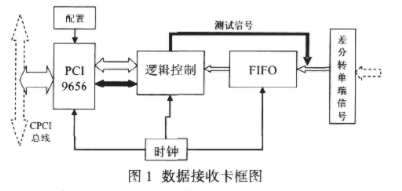

在CompactPCI端,PCI 9656提供了66MHz、64bit總線應用所需信號,可依據CompactPCI規范連接,通過簡單的外部電路,可實現Hot Swa p功能。

2020-12-08 10:49:58 2369

2369

、PCI9050的功能描述 PCI9030為非PCI設備和PCI總線提供數據通道。(1)初始化 在上電時,PCI9050的內部寄存器由PCI總線的RST#信號復位,在局部總線上輸出LRESET#信號并檢查

2018-11-29 14:52:52

。PCI9054工作在初始化器模式時,要求本地端的總線是32位的。在這里,用CPLD實現將80C51單片機的8位數據與16位地址轉換成32位的數據和地址,使用RAM的目的是提高8051的數據傳輸速度和處理復雜

2008-10-09 11:23:38

讀寫信號、BLAST#、READY#、ADS#和8051單片機相連。PCI9054工作在初始化器模式時,要求本地端的總線是32位的。在這里,用CPLD實現將80C51單片機的8位數據與16位地址轉換成

2018-12-05 10:12:42

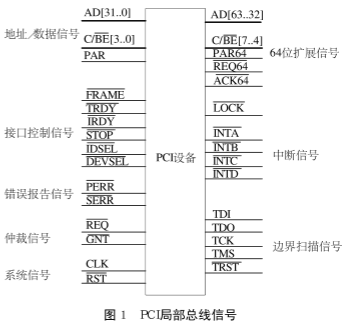

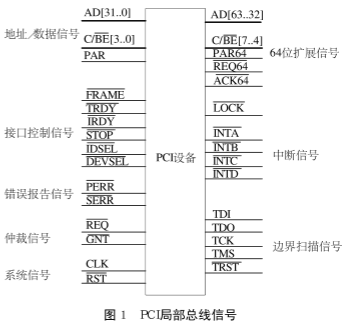

。作為主設備需要49條信號線,若作為目標設備,則需要47條信號線,可選的信號線有51條。利用這些信號線便可以傳輸數據、地址,實現接口控制、仲裁及系統的功能。PCI局部總線信號如下圖所示。下面按功能分組進行

2012-04-06 14:37:24

不同于ISA總線,PCI總線的地址總線與數據總線是分時復用的。這樣做的好處是,一方面可以節省接插件的管腳數,另一方面便于實現突發數據傳輸。在做數據傳輸時,由一個PCI設備做發起者(主控

2019-10-16 09:02:10

PCI總線的信號定義PCI總線是一條共享總線,在一條PCI總線上可以掛接多個PCI設備。這些PCI設備通過一系列信號與PCI總線相連,這些信號由地址/數據信號、控制信號、仲裁信號、中斷信號...

2022-02-16 06:48:12

存儲器讀1 1 1 0 存儲器一行讀0 1 1 1 存儲器寫1 1 1 1 存儲器寫并無效 PCI總線上所有的數據傳輸基本上都由以下三條信號線控制。FRAME:幀周期信號。由主設備驅動,表示一次訪問

2019-04-24 07:00:09

PCI總線是一種不依附于某個具體處理器的局部總線。從結構上看,PCI是在CPU和原來的系統總線之間插入的一級總線,具體由一個橋接電路實現對這一層的管理,并實現上下之間的接口以協調數據的傳送。管理器提供了

2008-12-09 13:46:13

,在這種情況下任然建議主設備繼續維持請求信號,以便仲裁器不會在傳輸過程中將總線使用權分配給另一個優先級更低的主設備。仲裁:如果一個主設備當前被默認分配到了總線使用權,那么它在開始一個非IDLE傳輸之前

2022-06-08 16:20:29

CAN總線的仲裁是基于“線與原理(有一個0則為0,全部為1才為1)”,也即,總線上連接多個設備,只要有一個設備輸出低電平,那么總線上的電平就為低(這一現象在CAN領域稱為“顯性”);只有全部設備均

2022-01-19 06:57:59

。實際上,這意味著沒有發送器應設置該位,而所有接收器均應忽略該位。這樣做的原因是為了防止大量設備因網絡流量泛濫。是的,我知道仲裁方案最終將使所有流量通過,但是我們認為確定性水平更高的網絡將比其他問題少。我認為我們是對的。

2020-10-02 23:00:00

總線上的設備分為主設備(ARM處理器)和從設備兩種,從設備級聯時,從設備的器件地址如何設置?相應的地址碼怎樣設置?

2013-07-11 15:00:20

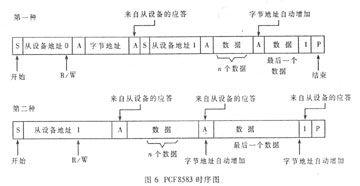

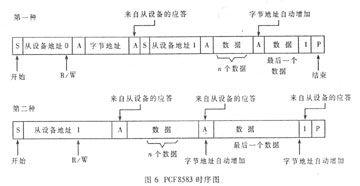

IIC總線通訊接口器件的CPLD實現摘要:介紹了采用ALTERA公司的可編程器件EPF10K10LC84-3實現IIC總線的通訊接口的基本原理,并給出了部分的VHDL語言描述。該通訊接口與專用的接口芯片相比,具有使用靈活、系統配置方便的特點。 [/hide]

2009-10-30 14:57:35

SPI總線(串行外設接口)全雙工通信主設備:設置配置:Arduino中的SPI庫(串行外設接口)全雙工通信SPI是一個主/從協議,一主多從,一次只能和一個設備通信。主設備:MOSI :主輸出,從輸入

2022-02-17 07:44:00

總線矩陣提供從主設備到從設備的訪問,實現并行訪問和高效操作當幾個高速外圍設備同時工作時。

STM32U5 Arm?Cortex?-M33核心針對通過具有直接訪問功能的指令緩存執行通過快速主端口進行

2023-09-08 06:48:06

今天SKYLAB小編給大家帶來一篇WiFi模塊的干貨,WiFi模塊在工作的時候其實是分主設備和從設備的,可能有些WiFi工程師平時不會注意這些細節,感覺實現某一項WiFi功能需要什么樣的WiFi模塊

2018-06-26 11:15:30

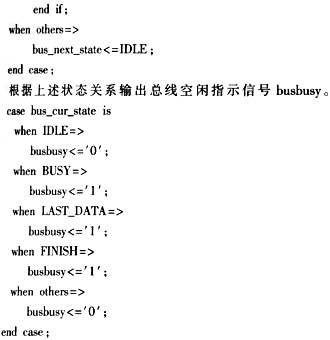

。同時還為DMA引擎提供PCI總線所處的狀態,如總線是否處于數據階段,是否有從設備終止等。 模塊的主要設計思路:當PCI總線仲裁器允許PCI_MT32成為總線主設備時,PCI_MT32功能模塊在本地側輸出

2012-11-28 15:38:05

CPLD技術在PCI總線開關中的應用使用CPLD技術開發PCI板卡有什么優點

2021-04-08 06:47:28

摘要:介紹了PCI總線控制芯片PCI2040的功能及內部結構,分析了基于PCI總線的雙DSP通信的硬件結構及實現方法,并描述了利用Windows2000 DDK開發WDM設備驅動程序的方法及PCI雙

2019-09-24 22:18:02

公司的FLEX10K系列CPLD器件EPF10K10LC84-3可以方便地實現I2C(IIC)總線的通訊接口,且具有高速、易調試、可以靈活地實現地在線配置等優點,同時大大地減少了系統的開發周期。1

2019-05-22 05:00:02

(Peripheral Component Interconnect)總線是當今PC 領域中流行的總線。目前實現PCI 接口一般采用專用器件, 有效方案分為兩種:使用可編程邏輯器件和使用總線專用接口器件

2010-09-22 08:51:09

編制設備驅動程序才能實現對PCI總線設備的完全訪問。 應用程序對設備I/O進行Win32調用,這個調用由I/O系統服務接收。I/O管理器從這個請求構造一個合適的I/O請求包(IRP)。在最簡單

2009-04-20 10:51:10

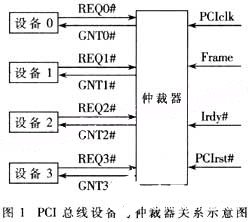

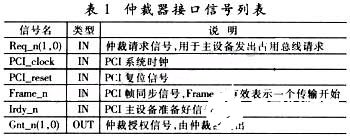

至少需要47條信號線。表1中列出了從設備接口設計必需的接口信號及說明。一個完整的PCI總線交易過程如下:要發起數據交易的設備先置REQ#,在得到仲裁器的許可(GNT#)后,通過拉低FRAME#啟動一個

2019-05-29 05:00:02

。HPI寄存器的選擇由HCNTL[1:0]腳在PCI總線地址有效期實現,說明如表1所示:在主機訪問DSP片內RAM過程中,主機首先根據訪問類型對HPIC寄存器進行初始化操作,然后再對HPIA寄存器進行操作

2018-12-17 11:29:06

,通過可編程器件,可以把PCI9052讀寫控制信號直接傳遞給IDT70V28L,完成時序的匹配。為將PCI9052的局部邏輯轉換為雙口RAM的讀寫控制信號和地址信號,本設計采用了可編程器件來實現它們之間

2018-12-12 10:27:45

PCI總線是高性能的32/64位同步總線,具有嚴格的規范保證數據傳輸的可靠性,微處理器與高集成度的外圍設備提供高速安全的接口,是迄今為止最成功的總線規范之一。由于PCI總線協議非常復雜,目前實現

2018-12-04 10:35:21

一種可行的方案就是利用CPLD作為溝通單片機與PCI設備間的橋梁,充分利用CPLD中I/O資源豐富,用戶可自定制邏輯的優勢,來幫助單片機完成與PCI設備間的通信任務。

2021-04-29 06:28:43

一種可行的方案就是利用CPLD作為溝通單片機與PCI設備間的橋梁,充分利用CPLD中I/O資源豐富、用戶可自定制邏輯的優勢,來幫助單片機完成與PCI設備間的通信任務。

2021-04-30 06:59:19

如何利用雙端口RAM去實現PCI總線接口?

2021-05-06 06:30:53

如何去采用PCI9030芯片實現從ISA總線到PCI總線的轉接卡的設計?有哪些方法?其過程是怎樣的?

2021-07-01 08:00:36

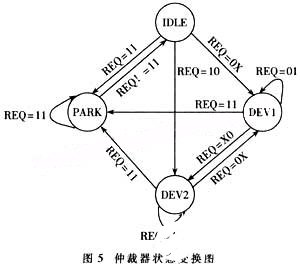

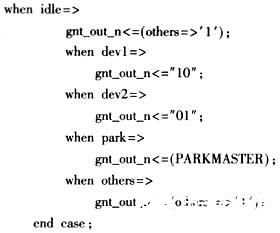

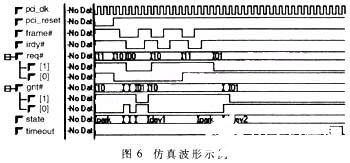

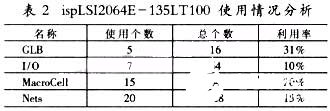

本文著眼于仲裁器的用例和優點,以及在VHDL中實現簡單優先級仲裁器。仲裁是任何現代計算機系統的重要組成部分。從I2C和CAN 等通信協議中的總線仲裁到多處理器系統中的存儲器仲裁,可以在需要共享資源

2021-12-23 06:38:07

,我認為我可以將仲裁器連接到主設備上的PLB,并將我的共享內存連接到接口的從設備端。但在這種情況下,我無法弄清楚PPC如何連接到PLB。如果我在這里正確的話,請評論。謝謝你,Shamanth。

2020-05-28 12:37:54

本設計采用了復雜可編程器件CPLD,用CPLD完成了PC104總線與429總線通訊的主要電路,大大節省了硬件資源,本文著重介紹了CPLD部分的設計。

2021-04-29 06:47:46

Signal Tap硬件調試原理是什么?使用Signal Tap的基本流程有哪些?如何用Signal Tap去調試PCI主設備控制器?

2021-04-29 07:00:53

隨著通用處理器和嵌入式技術的迅猛發展,越來越多的電子設備需要由處理器控制。目前大多數CPU和外部設備都會提供PCI總線的接口,PCI總線已成為計算機系統中一種應用廣泛、通用的總線標準[1

2011-10-08 09:44:30

怎么實現基于IP內核的PCI總線接口設計?

2021-05-27 06:34:05

。為了適應處理器尋址的靈活性,并對地址空問進行保護,VME總線提供6條地址修改線,選擇不同的地址修改碼即可實現16,24,32位的尋址變化,并對地址空間賦予特定的保護權限。控制線和地址線的不同組合可以靈活

2019-04-22 07:00:07

的33MHz時鐘,雙口RAM常常選用高速器件來簡化PCI傳輸的邏輯設計。 2 PCI總線傳輸時序分析PCI總線傳輸至少需要40多條信號線,包括數據/地址線、接口控制線、仲裁、總線命令及系統線等。每次

2019-06-17 05:00:11

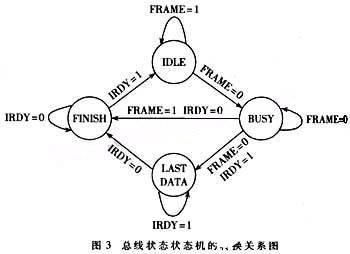

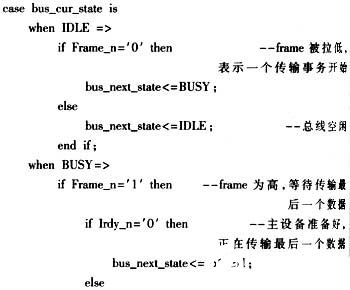

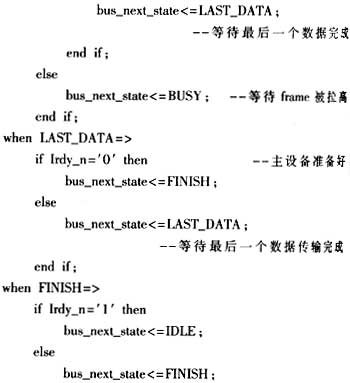

下單周期讀寫時序、1553B 總線控制器HOST 端時序和雙口RAM 時序采 用如圖2 所示的狀態機實現PCI 總線對1553B 總線控制器和雙口RAM 空間的讀寫操作。圖2 狀態轉換圖當9054

2019-05-21 05:00:22

47條信號線。表1中列出了從設備接口設計必需的接口信號及說明。一個完整的PCI總線交易過程如下:要發起數據交易的設備先置REQ#,在得到仲裁器的許可(GNT#)后,通過拉低FRAME#啟動一個傳輸交易

2019-06-20 05:00:03

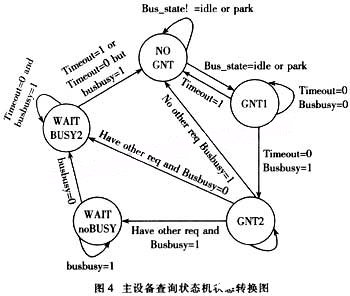

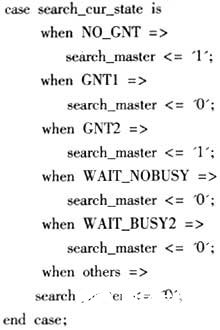

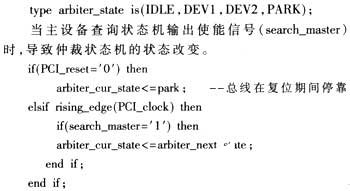

的主要設計思路:當PCI總線仲裁器允許PCI_MT32成為總線主設備時,PCI_MT32功能模塊在本地側輸出lm_adr_ackn信號,表明地址階段開始,此時主控邏輯模塊應在l_adi線提供PCI地址

2019-05-05 09:29:32

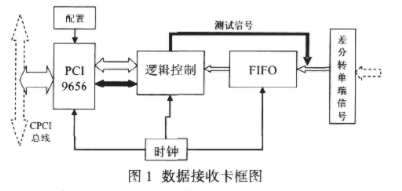

采用PCI總線流水式高速數據采集系統設計摘要:目前基于PCI總線的高速數據采集系統,大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設計,其通用性、靈活性差,不能

2009-10-30 15:09:49

IP核來實現PCI接口,利用基于PCI協議的IP核來實現PCI接口,這種設計開發速度較快,靈活性較好,但是IP核價格昂貴。采用FPGA實現PCI總線協議。采用CPLD/FPGA等可編程邏輯器件實現PCI

2019-05-30 05:00:02

BUSMASTER(DMA)設備; 支持PCI 延遲傳送,RETRY重入功能; 內部PCI讀寫FIFO各為512字節,4個PCI讀寫請求隊列; 內部集成旋轉優先級仲裁結構,公平的PCI主設備優先級設置

2019-06-20 05:00:02

重入功能;內部PCI讀寫FIFO各為512字節,4個PCI讀寫請求隊列;內部集成旋轉優先級仲裁結構,公平的PCI主設備優先級設置;PCI突發方式,133M字節/秒數據峰值傳送;功能1,2 16C950

2019-06-12 05:00:07

就可使用,大大降低了板卡升級的時間周期和開發難度,具有較高的實用價值和推廣價值。2 PCI總線的特點PCI是先進的高性能局部總線,可同時支持多組外圍設備。其特點是:總線操作與處理器一存儲器子系統操作

2019-04-29 07:00:09

核處理器NIOSⅡ作為系統的主控制器,結合ARINC429專用器件和其他外圍設備實現數據的收發功能。 ARI NC429接口板由數據收發、存儲器擴展、監控、PCI總線接口等模塊組成。NIOSⅡ控制

2019-04-26 07:00:08

PCI總線仲裁參考設計,Quicklogic提供

This application note describes a fully PCI-compliant Master/Slaveinterface. It utilizes thePCI burst transfer mode for

2008-05-20 10:48:55 84

84 在總線的主設備上增設了實時操作系統的任務優先級分配機制,基于蒙特卡羅選擇實現總線仲裁器的仲裁策略,建立不同類型的從設備存儲器模型。運用SystemC在交易級實現整個總線

2009-04-11 08:54:10 7

7 詳細闡述一種利用CPLD 實現的8 位單片機與PCI 設備間的通信接口方案,給出用ABEL HDL編寫的主要源程序。該方案在實踐中檢驗通過。

2009-04-14 17:32:19 34

34 采用可編程邏輯器件CPLD,分四個模塊——控制寄存器模塊、PCI控制器狀態機模塊、SRAM 控制器模塊和仲裁器模塊,分別完成通信并解析PCI總線、PCI狀態的控制和翻轉、負責SRAM接口數

2009-06-01 14:25:22 16

16 基于FPGA的PCI總線接口設計::PCI是一種高性能的局部總線規范,可實現各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現PCI總線接

2009-06-25 08:17:18 48

48 PCI總線傳輸的終止方式探析:探討了PCI 總線傳輸的終止方式。PCI 總線的主設備和目標設備都可以終止PCI 傳輸。主設備和目標設備在終止一次傳輸的同時還以信號的電平組合告知主

2009-06-28 19:32:07 22

22 本文根據EPON 系統中OLT 設備的特點以及背板設計的要求,在與傳統仲裁策略比較中提出了基于發送隊列平均長度的動態優先級仲裁策略,并給出了用硬件描述語言實現邏輯功能

2009-08-05 15:26:44 9

9 本文簡要介紹了PCI 總線的仲裁機制, 完成了PCI 總線仲裁器核心的設計、實現。通過ModelSim 進行了軟件仿真,最后在XILINX 公司的FPGA 上加以了驗證。

2009-09-03 08:18:29 27

27 本文重點分析了PCI 總線設備控制器的設計方案。以PCI 總線協議的分析和理解為基礎,對PCI 總線設備控制器進行了功能分析和結構劃分,對PCI 總線從設備控制器的設計思路和各個

2010-01-13 16:57:37 49

49 PCI總線協議的FPGA實現及驅動設計

摘要! 采用FPGA技術! 在公司的flex6000系列芯片上實現了從設備模式pci總線的簡化協議!并給出了WIndowsx 系統下的虛擬設備驅動程序

2010-03-12 14:30:27 36

36 摘要:文章提出了一種新的基于I2c總線的競爭與仲裁電路的結構,不僅簡化了總線競爭的操作,而且也加快了仲裁的速度。采用該結構的電路可以方便地在可編程邏輯器件中實現,

2010-05-06 09:06:33 17

17 集成到SOC中的功能模塊越來越多,對于共享總線的SOC系統,片上仲裁是使得各個模塊有效運作的必要手段。本文論述了SOC仲裁的基本原理,首先從目前SOC系統中常用的仲裁算法入手

2010-07-17 17:07:45 37

37 本文詳細介紹了OPB總線仲裁器的信號和仲裁機理。在QuartusII8.0平臺上,分別用固定優先級算法和LRU算法,用硬件描述語言(verilog HDL)對OPB總線仲裁器進行了RTL硬件建模。并用FPGA進行實現,

2010-07-17 18:10:59 25

25 摘 要: 本文采用Altera的CPLD實現了PCI總線至UTOPIA接口的邏輯轉換控制,為低成本實現ATM終端奠定了基礎。

2006-03-11 13:16:50 864

864

基于DSP與CPLD的I2C總線接口的設計與實現

帶有I2C總線接口的器件可以十分方便地將一個或多個單片機及外圍器件組成單片機系統。盡管這種總線結構沒有并行總線那

2009-03-28 15:07:47 1105

1105

摘 要 :PCI是一種高性能的局部總線規范,可實現各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現PCI總線接口的

2009-06-20 13:13:28 936

936

摘要:詳細闡述一種利用CPLD實現的8位單片機與PCI設備間的通信接口方案,給出用ABEL HDL編寫的主要源程序。該方案在實踐中檢驗通過。

關鍵詞:單片機 CPLD PCI

8位單片

2009-06-20 13:31:29 869

869

摘 要: 以自行研制開發的PCI高速總線背板為背景,系統地論述了PCI總線的仲裁機制、總線的缺省占用、仲裁信號協定及優先級仲裁算法,給出了采用EPLD實現仲裁器功能的編程設計

2009-06-20 13:32:20 961

961

基于CPLD的單片機與PCI接口設計解決方案

8位單片機在嵌入式系統中應用廣泛,然而讓它直接與PCI總線設備打交道卻有其固有缺陷。8位單片機只有16位

2009-09-26 17:41:20 825

825

一種基于CPLD的單片機與PCI接口設計方案

0 引言

8位單片機在嵌入式系統中應用廣泛,然而讓它直接與PCI總線設備打交道卻有其固有缺陷。8

2009-11-12 09:56:50 582

582 提出了一種使用CPLD解決雙端口RAM地址譯碼和PCI接口芯片局部總線仲裁的的硬件設計方案,并給出了PCI總線接口芯片

2011-01-07 12:13:03 1891

1891

探討了PCI 總線傳輸的終止方式。PCI 總線的主設備和目標設備都可以終止PCI 傳輸。主設備和目標設備在終止一次傳輸的同時還以信號的電平組合告知主設備其不同的終止狀態。主設備啟

2011-05-18 16:43:46 28

28 基于CPLD的PWM控制器電路結構簡單,設計方便,簡化了外部線路設計,節省了PCB板空間,解決了機電一體化開發平臺中MCU模塊與功率模塊基于PCI總線的通信

2011-05-24 10:26:47 869

869

出了一種PCI總線從設備的CPLD實現方法。該方法遵從PCI規范2.2版,實現了資源自動配置并且支持數據突發傳輸。試驗證明該方法的有效性,其突發傳輸速率可達20 MBs -1 。

2011-11-30 17:06:11 60

60 文中主要介紹了采用CPLD實現32 bit 33 MHzPCI從設備接口的設計方法,該從設備接口模塊遵從PCI規范2.2版,實現了資源的自動配置,支持突發傳輸,并為用戶提供了一個簡單的接口。設計完成

2012-08-06 15:18:22 1788

1788

基于CPLD的SGPIO總線實現及應用

2017-01-24 16:00:51 75

75 圖1是PCI Express設備和接口的一個典型實現DM6467 PCI總線通過xio2000a轉化的橋接。的xio2000a裝置作為一個橋接上游和下游的PCI Express設備的PCI總線設備

2018-04-18 11:14:53 6

6 本文首先介紹了CAN總線仲裁是什么,其次介紹了CAN總線仲裁的示意圖,最后詳細的闡述了CAN總線位仲裁技術,具體的跟隨小編一起來了解一下吧。

2018-05-07 14:27:26 15850

15850

PCI總線是一種樹型結構,并且獨立于CPU總線,可以和CPU總線并行操作。PCI總線上可以掛接PCI設備和PCI橋片,PCI總線上只允許有一個PCI主設備,其他的均為PCI 從設備,而且讀寫操作只能在主從設備之間進行,從設備之間的數據交換需要通過主設備中轉。

2018-06-07 15:02:00 3581

3581

在一個PCI應用系統中,取得了總線控制權的設備稱為“主設備”,而被主設備選中以進行通信的設備稱為“從設備”或“目標設備”。相應的接口信號線,通常分為必備的和可選的2大類。若只作為目標設備,至少需要

2018-08-07 17:55:30 10288

10288 )的新特性,目前已經成為計算機系統中應用最為廣泛,并且最為通用的總線標準。Linux的內核能較好地支持PCI總線,本文以Intel 386體系結構為主,探討了在Linux下開發PCI設備驅動程序

2019-04-02 14:38:11 267

267 實現PCI總線協議目前主要有專用接口芯片和CPLD實現兩種方式。專用接口芯片使用簡單方便、工作穩定可靠,但往往具體應用中只用到部分功能,并且需要可編程邏輯配合使用,這樣不僅浪費專用芯片的資源,而且

2020-03-20 09:54:04 1268

1268

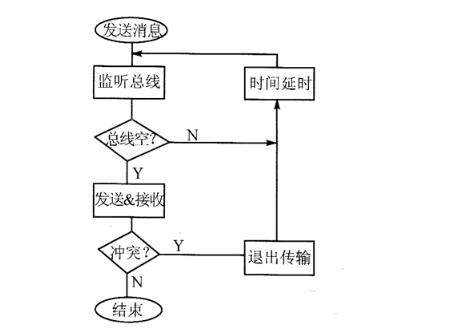

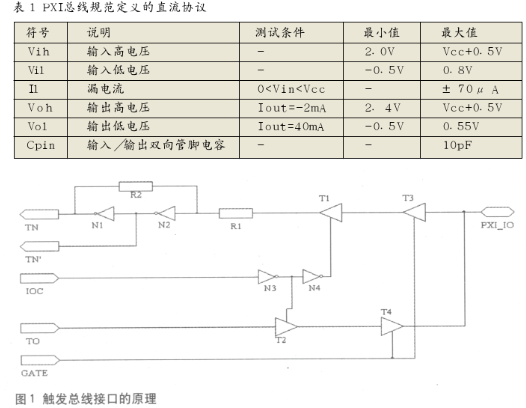

pxi是pci extensiON for inSTrumentation的縮寫,是為了將pci總線擴展到測試儀器領域而推出的以pci計算機局部總線為基礎的模塊儀器結構。pxi相對于cpci系統的一個重要特點是定義了8根觸發總線,這可以實現系統中各模塊間的同步和通信。

2020-04-04 10:36:00 1557

1557

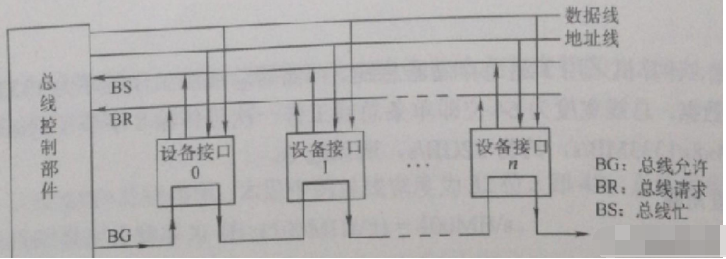

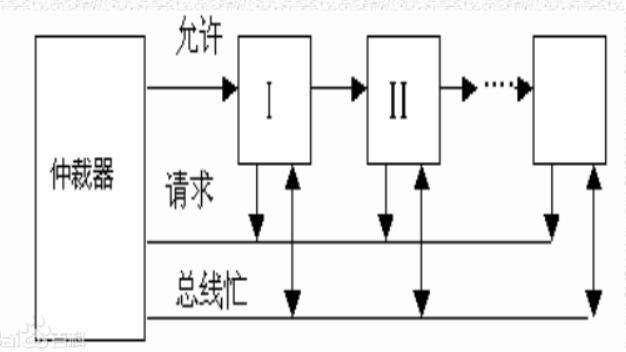

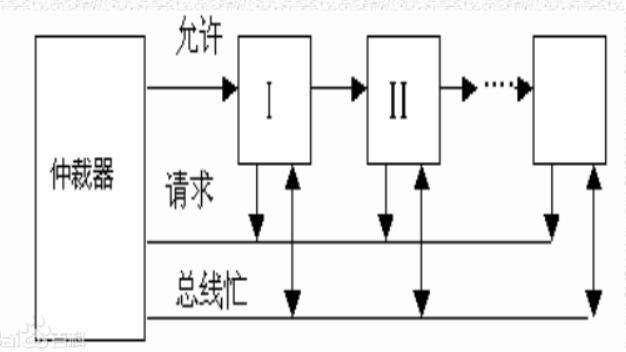

需要使用總線的總線主設備(如CPU、DMA控制器等)向總線仲裁機構提出占用總線的請求,經總線仲裁機構判定,若滿足響應條件,則發出響應信號,并把下一個總線傳送周期的總線控制權授予申請者。

2020-05-20 17:51:27 5334

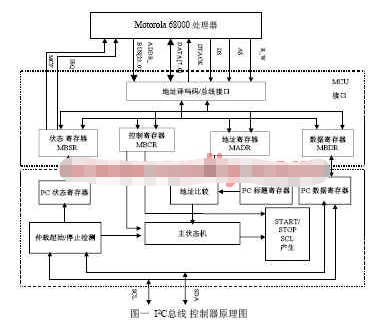

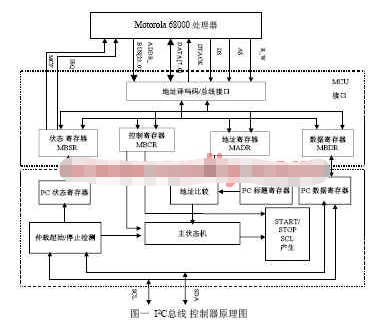

5334 的MCU,可采用軟件模擬,有通用軟件包可以使用,但功能比較簡單。在MCU(以Motorola 68000系列為例)和CPLD電子系統設計中,利用CPLD器件資源,按照I2C總線協議標準模式,設計了功能完善的I2C總線控制器,給出了設計思路和實現方法。

2020-08-11 17:03:55 1508

1508

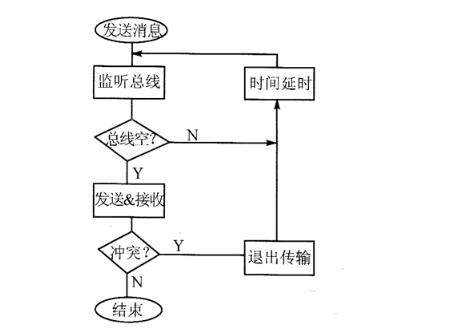

在一個多主控設備的總線中,每個主控設備都能啟動數據傳送。因此必須提供一種機制來決定在某個時刻由哪個設別擁有總線使用權,決定哪個主控設備能的到總線使用權的過程稱為總線仲裁。

2020-10-30 10:40:22 8842

8842

總線仲裁就是在多個總線主設備的環境中提出來的。在多處理機系統中,每個處理機都可以作為總線主設備,都要共享資源,它們都必須通過系統總線才能訪問其它資源,總線也可視為是一種重要的公共資源。由于每個處理機

2020-12-14 15:26:57 4882

4882

是實現電流盡可能小的系統,功耗低。軟件透明,在和PCI設備之間通信時,軟件驅動之間使用相同的命令集和狀態定義。隨著嵌入式計算機的發展,PCI總線也越來越多地被引入到嵌入式系統中。本文介紹在“十五”預研項目中實現嵌入式PCI總線的一些經驗體會,與大家切磋。

2021-03-26 10:31:30 3387

3387

PCI總線的信號定義 PCI總線是一條共享總線,在一條PCI總線上可以掛接多個PCI設備。這些PCI設備通過一系列信號與PCI總線相連,這些信號由地址/數據信號、控制信號、仲裁信號、中斷信號等多種

2021-07-18 09:55:32 1981

1981 PCI總線的信號定義PCI總線是一條共享總線,在一條PCI總線上可以掛接多個PCI設備。這些PCI設備通過一系列信號與PCI總線相連,這些信號由地址/數據信號、控制信號、仲裁信號、中斷信號...

2021-12-17 18:26:06 3

3 電子發燒友網站提供《STM32U5中用于主設備和從設備互連的總線矩陣.pdf》資料免費下載

2023-08-01 15:48:43 0

0 PCI總線協議非常復雜,目前實現PCI接口的有效方案分為兩種:即使用可編程邏輯器件和使用專用總線接口的器件,可編程邏輯器件實現PCI接口比較靈活,可以利用的器件比較多,現在有許多生產可編程邏輯器件的廠商(如Xilinx的Logicore和Alerra的AMPP)都提供經過嚴格測試的PCI接口功能模塊

2023-08-01 14:37:19 553

553

電子發燒友App

電子發燒友App

評論