ASIC和FPGA具有不同的價(jià)值主張,在作出選擇前必須仔細(xì)評估。兩種種技術(shù)對比。這里介紹了ASIC和FPGA 的優(yōu)勢與劣勢。

2011-03-31 17:30:09 5382

5382

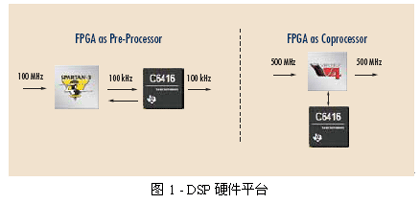

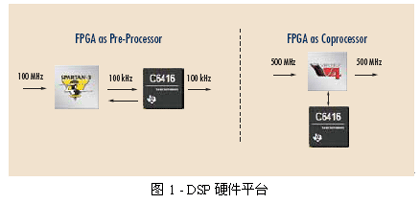

傳統(tǒng)的、基于通用DSP處理器并運(yùn)行由C語言開發(fā)的算法的高性能DSP平臺,正在朝著使用FPGA預(yù)處理器和/或協(xié)處理器的方向發(fā)展。這一最新發(fā)展能夠?yàn)楫a(chǎn)品提供巨大的性能、功耗和成本優(yōu)勢。 盡管優(yōu)勢如此明顯

2023-10-21 16:55:02 1498

1498

嗨,我使用的是virtex 5 FPGA。我正在運(yùn)行外部10Mhz時(shí)鐘信號來運(yùn)行二進(jìn)制計(jì)數(shù)器。當(dāng)我嘗試使用DCM時(shí),它表示最低頻率為32MHz。可以將此信號運(yùn)行到FPGA的i / o輸入并通過全局

2019-02-21 10:32:51

的設(shè)計(jì)者面臨著一個(gè)不同以往的挑戰(zhàn):提供一個(gè)不僅能滿足這些集成電路對互連帶寬的要求,而且還能支持不同接口協(xié)議的可編程接口。解決方案是可編程硬件I/O模塊。這些可編程硬件模塊位于FPGA的I/O路徑內(nèi)。硬件模塊

2018-11-26 11:17:24

FPGA中的I_O時(shí)序優(yōu)化設(shè)計(jì)在數(shù)字系統(tǒng)的同步接口設(shè)計(jì)中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時(shí)IPO接口的時(shí)序問題顯得尤為重要。介紹了幾種FPGA中的IPO時(shí)序優(yōu)化設(shè)計(jì)的方案, 切實(shí)有效的解決了IPO接口中的時(shí)序同步問題。

2012-08-12 11:57:59

有誰來闡述一下FPGA協(xié)處理的優(yōu)勢有哪些?如何去使用FPGA協(xié)處理?怎樣借助FPGA協(xié)處理去提升性能?怎樣借助FPGA嵌入式處理去降低成本?從C程序到系統(tǒng)門指的是什么?采用FPGA協(xié)處理的障礙是什么?

2021-04-14 06:07:36

更快、更大,每比特的功耗也更低,但是如何實(shí)現(xiàn)FPGA和DDR3 SDRAM DIMM條的接口設(shè)計(jì)呢? 關(guān)鍵字:均衡(leveling)如果FPGA I/O結(jié)構(gòu)中沒有包含均衡功能,那么它與DDR3

2019-04-22 07:00:08

可編程邏輯作為圖像傳感器和ASSP之間的橋接面臨三個(gè)方面的挑戰(zhàn)。首先,FPGA必須為接口信號提供電信號支持。第二,FPGA的I/O必須有足夠的gearing邏輯來支持快速串行傳感器接口。第三

2011-05-24 14:17:00

的FPGA,始終引領(lǐng)先進(jìn)的工藝。 fpga的優(yōu)勢 1)通信高速接口設(shè)計(jì)。FPGA可以用來做高速信號處理,一般如果AD采樣率高,數(shù)據(jù)速率高,這時(shí)就需要FPGA對數(shù)據(jù)進(jìn)行處理,比如對數(shù)據(jù)進(jìn)行抽取濾波

2020-10-26 14:35:32

同學(xué),版權(quán)所有)圖3.14 CycloneIII系列器件的供電標(biāo)準(zhǔn)說到I/O電壓,我們不得不多提兩句,畢竟可以兼容非常多的I/O電壓標(biāo)準(zhǔn)是FPGA的一大優(yōu)勢,尤其是各種高速差分信號的支持。圖3.15中

2015-04-22 12:06:21

Analyzer Interface,即邏輯分析儀接口。這里的邏輯分析儀接口是針對于外部邏輯分析儀的。調(diào)試者可以設(shè)置FPGA器件內(nèi)部多個(gè)信號映射到一個(gè)預(yù)先保留或者暫時(shí)不使用的I/O接口上,從而通過較少的I

2015-09-02 18:39:49

的數(shù)字邏輯資源可以替代各種分立的數(shù)字芯片;豐富的I/O引腳支持各種常見協(xié)議,這也能夠免去很多外圍接口芯片;器件內(nèi)部大都能夠很好的支持可編程的端接匹配元件,這也能夠降低BOM成本,減少元器件數(shù)量;而如今正時(shí)

2015-03-26 11:00:19

概覽高端設(shè)計(jì)工具為少有甚是沒有硬件設(shè)計(jì)技術(shù)的工程師和科學(xué)家提供現(xiàn)場可編程門陣列(FPGA)。無論你使用圖形化設(shè)計(jì)程序,ANSI C語言還是VHDL語言,如此復(fù)雜的合成工藝會(huì)不禁讓人去想FPGA真實(shí)

2019-07-29 08:12:26

FPGA的基本特點(diǎn)是什么?FPGA有什么優(yōu)勢?FPGA的應(yīng)用方向是什么?

2021-10-08 06:43:45

最后芯片的制作。? 電路設(shè)計(jì)人員使用 FPGA 進(jìn)行電路設(shè)計(jì)時(shí),不需要具備專門的 IC(集成電路)深層次的知識,FPGA 軟件易學(xué)易用。

2018-09-05 09:32:29

規(guī)模時(shí)設(shè)計(jì)成本低以及設(shè)計(jì)周期短等優(yōu)勢。簡單地比較了現(xiàn)在市場上的電子器件之后,我們來詳細(xì)地分析一下MCU與FPGA之間的區(qū)別:MCU又稱為單片機(jī),它為8位的微控制器,主要用在工業(yè)控制,FPGA則為

2020-06-23 15:04:14

外設(shè)電路(I/O應(yīng)用)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCttFPGA器件擁有著豐富的I/O資源,它

2019-04-12 06:35:33

FPGA的I/O結(jié)構(gòu)的發(fā)展的怎么樣了?

2021-04-29 06:12:52

各種應(yīng)用的推動(dòng),使FPGA發(fā)展到了一個(gè)關(guān)鍵點(diǎn),它正在逐步取代其他技術(shù),進(jìn)入新的市場領(lǐng)域,因此,我們面臨的挑戰(zhàn)是不斷創(chuàng)新,提供功能最合適的產(chǎn)品和解決方案。在我們規(guī)劃第三代產(chǎn)品時(shí),目的就是要提高客戶各種應(yīng)用軟件和市場的效用,發(fā)揮可編程解決方案的巨大潛力。

2019-07-16 07:29:27

實(shí)現(xiàn)就會(huì)有很大的優(yōu)勢。在考慮是否使用FPGA技術(shù)來實(shí)現(xiàn)目標(biāo)產(chǎn)品時(shí),我們需要重點(diǎn)從以下幾個(gè)方面進(jìn)行評估。●可升級性——產(chǎn)生在設(shè)計(jì)過程中,甚至將來產(chǎn)品發(fā)布后,是否有較大的功能升級需求?是否應(yīng)該選擇具有易于

2017-12-20 10:07:44

PCI Express的高級特性包括哪些?實(shí)現(xiàn)PCI Express接口的難點(diǎn)有哪些?FPGA的PCI Express接口有哪些優(yōu)勢?

2021-05-26 06:52:48

邏輯資源可以替代各種分立的數(shù)字芯片;豐富的I/O引腳支持各種常見協(xié)議,這也能夠免去很多外圍接口芯片;器件內(nèi)部大都能夠很好的支持可編程的端接匹配元件,這也能夠降低BOM成本,減少元器件數(shù)量;而如今正時(shí)

2019-04-12 00:25:04

FPGA取代標(biāo)準(zhǔn)的微控制器不能夠產(chǎn)生一個(gè)節(jié)約成本的替代方案。只有不能通過在微控制器內(nèi)集成外設(shè)來滿足設(shè)計(jì)的邊 界條件情況下,FPGA的解決方案才變得更加具有吸引力,例如PWM通道的數(shù)量,計(jì)數(shù)器/定時(shí)器或I/O

2012-08-11 11:27:45

時(shí)鐘管理單元DCM/PLL也是必不可少的內(nèi)部部件。除此之外,FPGA內(nèi)部還包括接口I/O,I/O分為普通I/O和高速I/O,高速I/O支持例如高速的SERDES,用于實(shí)現(xiàn)XAUI,PCIE等高速接口

2018-08-06 11:44:25

設(shè)計(jì)12021.12.5 FPGA SRIO接口設(shè)計(jì)12021.12.5 設(shè)計(jì)案例分析-萬兆網(wǎng)卡設(shè)計(jì)實(shí)例72021.12.10課程鏈接:騰訊課堂:https://ke.qq.com/course/4093287

2021-11-17 23:12:06

行,速度快。Xilinx Spartan-7 FPGA器件適用于那些成本敏感型應(yīng)用。它采用小型封裝卻擁有高比例的I/O數(shù)量,單位功耗性價(jià)比相較前代產(chǎn)品提升多達(dá)四倍,可提供靈活的連接能力、接口橋接和輔助芯片

2018-08-02 09:37:08

基于SRAM的FPGA結(jié)構(gòu)是怎樣構(gòu)成的?FPGA連線資源的優(yōu)勢有哪些?

2021-05-06 07:04:23

嗨, 我想把晶體振蕩器的CLK帶到FPGA里面的數(shù)字設(shè)計(jì)。該CLK連接到FPGA的I / O引腳。如果我在映射中運(yùn)行Impliment設(shè)計(jì),我將得到錯(cuò)誤。所以我將在UCF文件中將網(wǎng)名命名如下。NET

2019-01-29 10:05:43

MODULE USB-TO-FPGA SPARTAN3

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN 3A

2023-04-06 11:27:11

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

` 本帖最后由 海中央 于 2013-8-31 09:59 編輯

由于自己的FPGA開發(fā)板上的 VGA 只能顯示8中顏色,所以為了顯示更多的顏色,我參考了網(wǎng)上的一些擴(kuò)展RGB位寬的設(shè)計(jì)方案

2013-08-31 09:41:01

按照Bank進(jìn)行劃分,每個(gè)Bank獨(dú)立供電,以使FPGA I/O適應(yīng)不用電壓標(biāo)準(zhǔn),增強(qiáng)I/O設(shè)計(jì)的靈活性。每個(gè)用戶Bank包括50個(gè)I/O管腳或者24對差分對管腳(48個(gè)差分信號),Top

2021-05-28 09:23:25

受到影響。2. FPGA技術(shù)的五大優(yōu)勢性能-利用硬件并行的優(yōu)勢,FPGA打破了順序執(zhí)行的模式,在每個(gè)時(shí)鐘周期內(nèi)完成更多的處理任務(wù),超越了數(shù)字信號處理器(DSP)的運(yùn)算能力。 著名的分析與基準(zhǔn)測試公司BDTI

2019-04-28 10:04:13

模擬 I2C 接口程序的基本框架如圖 4-4 所示。1.程序接口用于和應(yīng)用程序連接的接口,將應(yīng)用程序的數(shù)據(jù)按照 I2C 協(xié)議的方式通過 SDA 傳遞給外部器件。包括下列內(nèi)容:? clk_I FPGA

2018-10-09 11:28:28

- 2.5VVCCO_35 - 2.5V連接到I / O bank的一些外部電路在2.5V FPGA電源軌之前上電(這超出了我的控制范圍)。這會(huì)以奇怪的方式導(dǎo)致2.5V FPGA電源軌斜坡,請參考附圖。基本上2.5VFPGA

2020-07-30 09:51:29

你好,我想和FPGA接口,想聽聽我有什么選擇。我正在查看數(shù)據(jù)表頁21中的外部存儲器接口部分5.6,我看到它有一個(gè)并行數(shù)據(jù)總線、并行地址總線和一些控制信號。我需要更多地了解這個(gè)問題,但是有人能告訴我

2018-11-15 14:08:43

I/O進(jìn)行測試。但是外部的測試設(shè)備在測試FPGA系統(tǒng)時(shí),常會(huì)遇到這樣的情況:FPGA的I/O引腳數(shù)量不夠豐富,PCB布線和封裝丁藝復(fù)雜導(dǎo)致I/O引腳引出困難,外部測試探頭有影響FPGA信號時(shí)序和完整性的可能。

2019-08-19 08:03:56

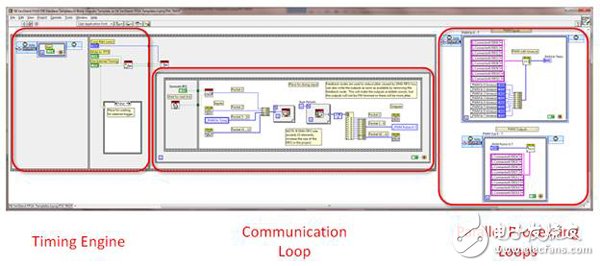

美國國家儀器有限公司(National Instruments,簡稱NI)近日針對PXI平臺,推出了一個(gè)全新的、開放式的、基于FPGA的產(chǎn)品系列。NI FlexRIO系列產(chǎn)品是工業(yè)領(lǐng)域首款成熟商用現(xiàn)成產(chǎn)品,它為工程師們提供了同時(shí)結(jié)合高速、工業(yè)級I/O和NI LabVIEW FPGA技術(shù)的解決方案。

2019-10-29 07:03:11

產(chǎn)品的生命周期中,使用FPGA技術(shù)實(shí)現(xiàn)所能夠帶來的潛在優(yōu)勢。● 靈活性:可重編程,可定制。易于維護(hù),方便移植、升級或擴(kuò)展。降低NRE成本,加速產(chǎn)品上市時(shí)間。支持豐富的外設(shè)接口,可根據(jù)需求配置。● 并行性

2016-06-29 09:37:38

`再談設(shè)計(jì)工具FPGA的優(yōu)勢FPGA最大的優(yōu)勢特點(diǎn)就是能夠縮短開發(fā)所需時(shí)間。 換句話說,通過使用FPGA,設(shè)計(jì)人員可以有效地利用每一分鐘進(jìn)行開發(fā)。例如,在開發(fā)過程中使用FPGA與否,可以導(dǎo)致開發(fā)時(shí)間

2012-02-24 17:26:23

,那么這種FPGA將不能滿足系統(tǒng)速度的要求。2. FPGA設(shè)計(jì)時(shí)序收斂。進(jìn)行足夠的靜態(tài)時(shí)序分析和時(shí)序仿真以確保HDL設(shè)計(jì)滿足硬件的時(shí)序要求。擁有已經(jīng)過實(shí)踐驗(yàn)證的硬件模塊,例如DDR存儲器I/O接口和串行

2012-02-27 15:18:09

在芯片設(shè)計(jì)中FPGA的優(yōu)勢是什么?基于FPGA的芯片設(shè)計(jì)方法及流程是怎樣的?

2021-05-10 07:06:05

基于FPGA和AD1836的I2S接口該如何去設(shè)計(jì)?

2021-05-26 06:45:37

進(jìn)行管腳連接。 圖1 接口總框圖 EP3C16只有TOP和BOTTOM邊的BANK支持200MHz DDR2接口(因?yàn)镈DR2管腳的特殊要求,DQS、DQ、DM管腳在FPGA上都需要專用管腳

2011-05-03 11:31:09

集成了1個(gè)增強(qiáng)型的8051,1個(gè)智能USB串行接口引擎,1個(gè)USB數(shù)據(jù)收發(fā)器,3個(gè)8位I/O口,16位地址線,8.5 KB RAM和4 KBFIFO等。增強(qiáng)性8051內(nèi)核完全與標(biāo)準(zhǔn)8051兼容,而性能

2021-06-24 07:00:00

如何克服FPGA I/O引腳分配挑戰(zhàn)?

2021-05-06 08:57:22

嵌入式測試是什么?如何用FPGA技術(shù)去實(shí)現(xiàn)嵌入式設(shè)計(jì)?如何測試FPGA中的高速串行I/O?

2021-04-13 07:03:58

嗨專家,我正在使用Spartan3AN(XC3S50AN)FPGA板和平臺線USB II。你能告訴我如何通過JTAG監(jiān)控PC中FPGA I / O的狀態(tài)嗎?謝謝,V。Prakash以上來自于谷歌翻譯

2019-06-18 09:05:14

小編科普工業(yè)無線技術(shù)的五大考慮因素

2021-05-26 07:08:12

設(shè)備來實(shí)現(xiàn),前者被稱為I/O接口,而后者則被稱為存儲器接口。存儲器通常在CPU的同步控制下工作,其接口電路比較簡單;而I/O設(shè)備品種繁多,其相應(yīng)的接口電路也各不相同,因此,習(xí)慣上說到接口只是指I/O

2017-06-27 11:55:50

一定能夠滿足特殊 I/O 的需要。 近期最值得一提的技術(shù)躍進(jìn),即為適用于 PXI 的 NI FlexRIO 硬體;不僅整合了其他 NI 系統(tǒng)中的 LabVIEW FPGA 技術(shù),并具有開放式的使用者客

2019-04-28 10:04:14

隨著現(xiàn)代技術(shù)的發(fā)展,SPI接口總線已經(jīng)成為了一種標(biāo)準(zhǔn)的接口,由于協(xié)議實(shí)現(xiàn)簡單,并且I/O資源占用少,為此SPI總線的應(yīng)用十分廣泛。目前,SPI接口的軟件擴(kuò)展方法雖然簡單方便,但若用來通信,則速度

2019-08-09 08:14:34

你好我試圖將1PPS從GPS接收器連接到FPGA I / O引腳之一。我希望FPGA在I / O引腳上看到1pps的上升沿時(shí)執(zhí)行一些任務(wù)。我正在使用verilog進(jìn)行hdl。我沒有在代碼中指出這一點(diǎn)

2019-05-24 08:02:28

圖片一是我需要110個(gè)I/O接口,圖片二是板子的所有接口,問一下我該如何分配接口?????

2016-10-25 15:05:04

大家好,我想檢查FPGA功能和I / O引腳功能在我的主板上使用“Selftest application”。在我的Selftest應(yīng)用程序中,我可以使用哪些方法來檢查這些?請?zhí)峁┮恍┫敕āVx謝

2019-04-01 12:33:26

VIRTEX-6 FPGA的I / O支持的最大數(shù)據(jù)速率是多少?我想在Virtex-6的I / O接收625MSPS的數(shù)據(jù)。這可以實(shí)現(xiàn)嗎?

2020-07-13 09:45:20

輕松實(shí)現(xiàn)高速串行I/OFPGA應(yīng)用設(shè)計(jì)者指南輸入/輸出(I/O)在計(jì)算機(jī)和工業(yè)應(yīng)用中一直扮演著關(guān)鍵角色。但是,隨著信號處理越來越復(fù)雜,I/O通信會(huì)變得不可靠。在早期的并行I/O總線中,接口的數(shù)據(jù)對齊

2020-01-02 12:12:28

使用LabVIEW FPGA 模塊和可重新配置I/O 設(shè)備開發(fā)測量與控制應(yīng)用通過使用LabVIEW FPGA 模塊和可重新配置I/O(RIO)硬件,NI 為您提供了一種直觀可用的解決方案,它可以將

2009-07-23 08:15:57

FPGA怎么選擇?針對功耗和I/O而優(yōu)化的FPGA介紹

2021-05-06 09:20:34

什么是陶瓷傳感器?陶瓷傳感器的五大應(yīng)用分別是什么?

2021-05-12 07:08:09

數(shù)784邏輯元件/單元數(shù)1862總 RAM 位數(shù)25088I/O 數(shù)192柵極數(shù)40000電壓 - 電源3V ~ 3.6V安裝類型表面貼裝型工作溫度0°C ~ 8

2022-04-19 09:45:33

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎(chǔ)的函數(shù)庫以及常用的控制函數(shù)模塊,配合

2022-05-19 09:16:05

概述EasyGo FPGA Solver是EasyGo開發(fā)的專門部署在FPGA 硬件上的解算器軟件。根據(jù)不同的應(yīng)用需求,會(huì)有不同的FPGA Solver 選擇

2022-05-19 09:21:43

嵌入式IC - FPGA(現(xiàn)場可編程門陣列), 197 I/O 256CABGA

2022-06-16 14:09:08

FBGA-672 FPGA - 現(xiàn)場可編程門陣列 , 206 I/O FPGA - 現(xiàn)場可編程門陣列 , Virtex-5 FPGA - 現(xiàn)場可編程門陣列 , - 40 C FPGA - 現(xiàn)場可編程

2022-08-04 11:25:44

去偏移和包重組是在FPGA中實(shí)現(xiàn)SPI-4.2接口的核心難點(diǎn),在分析偏移和包重組原理的基礎(chǔ)上,給出基于FPGA的SPI-4.2接口的設(shè)計(jì)與實(shí)現(xiàn)方案,并對關(guān)鍵部分給出了硬件原理圖,在線測試結(jié)

2009-04-10 09:43:35 32

32 EP4CE10F17I7N,Cyclone IV FPGA設(shè)備,INTEL/ALTERAEP4CE10F17I7N,Cyclone IV FPGA設(shè)備,INTEL

2023-02-20 17:03:19

FPGA, Artix-7, MMCM, PLL, 285 I/O, 628 MHz, 101440單元, 950 mV至1.05 V, FBGA-484Xilinx Artix?-7 FPGA系列

2023-05-10 16:03:24

中級篇 II什么是Real-time(實(shí)時(shí)) 1-4選擇合適的LabVIEW實(shí)時(shí)開収平臺 5-20FPGA深層解析 21-23FPGA技術(shù)介紹:五大優(yōu)勢 24-34基于FPGA的控制:數(shù)百萬個(gè)供您遣用的晶體管——FP

2010-07-01 09:04:32 20

20 本文的方案采用FPGA取代計(jì)算機(jī),作為腦機(jī)接口的控制和信息處理器。主要包括腦電采集電路、基于FPGA的VGA視覺刺激器和FPGA開發(fā)板三部分

2011-12-09 15:25:37 1837

1837

基于FPGA的SDI接口設(shè)計(jì),學(xué)習(xí)FPGA的好資料!!!!

2016-06-06 10:00:46 29

29 本內(nèi)容主要分析了基于FPGA的系統(tǒng)需求,賽靈思UltraScale FPGA DDR4和其他并行接口分析以及針對高性能高度靈活方案的PHY解決方案介紹。

2016-08-03 19:37:24 190

190 所屬選板: FPGA接口VI和函數(shù) 必需: FPGA接口 關(guān)閉FPGA VI的引用并可選擇重置該VI的執(zhí)行。默認(rèn)情況下,“關(guān)閉FPGA VI引用”函數(shù)可關(guān)閉FPGA VI的引用并重置FPGA VI

2017-11-18 05:02:19 1856

1856

現(xiàn)場可編程門陣列(FPGA)技術(shù)不斷呈現(xiàn)增長勢頭,預(yù)計(jì)到2013年1全球FPGA市場將增長至35億美元。 1984年Xilinx剛剛創(chuàng)造出FPGA時(shí),它還是簡單的膠合邏輯芯片,而如今在信號處理和控制應(yīng)用中,它已經(jīng)取代了自定制專用集成電路(ASIC)和處理器。

2018-04-11 14:41:00 26641

26641 學(xué)習(xí)FPGA五大忌:急于求成(一兩天就想著要學(xué)習(xí)完所有知識)2:沒耐心和毅力(遇到不懂不理解就想放棄)3:想法太多

2018-09-15 09:34:22 3466

3466 現(xiàn)場可編程門陣列(FPGA)技術(shù)不斷呈現(xiàn)增長勢頭。 1984年Xilinx剛剛創(chuàng)造出FPGA時(shí),它還是簡單的膠合邏輯芯片,而如今在信號處理和控制應(yīng)用中,它已經(jīng)取代了自定制專用集成電路(ASIC)和處理器。 這項(xiàng)技術(shù)的成功之處到底在哪里? 本文將主要介紹FPGA,并著重描述FPGA的獨(dú)特優(yōu)勢。

2020-01-25 11:54:00 5229

5229 FPGA的優(yōu)勢有三個(gè)方面:1)通信高速接口設(shè)計(jì)。FPGA可以用來做高速信號處理,一般如果AD采樣率高,數(shù)據(jù)速率高,這時(shí)就需要FPGA對數(shù)據(jù)進(jìn)行處理。

2020-01-10 15:46:21 1073

1073 偏移和包重組是在FPGA中實(shí)現(xiàn)SPI一4.2接口的核心難點(diǎn),在分析偏移和包重組原理的基礎(chǔ)E,給出基于FPGA的SPI一4.2接口的設(shè)計(jì)與實(shí)現(xiàn)方案,并對關(guān)鍵部分給出r硬件原理圖,在線測試結(jié)果證明該方案可以實(shí)現(xiàn)SPI一4.2接口的功能。

2021-01-25 14:51:21 13

13 1)靈活性:通過對 FPGA 編程,FPGA 能夠執(zhí)行 ASIC 能夠執(zhí)行的任何邏輯功能。FPGA 的獨(dú)特優(yōu)勢在于其靈活性,即隨時(shí)可以改變芯片功能,在技術(shù)還未成熟的階段,這種特性能夠降低產(chǎn)品的成本與風(fēng)險(xiǎn),在 5G 初期這種特性尤為重要。

2022-11-25 09:31:25 2446

2446 中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。那么這項(xiàng)技術(shù)的獨(dú)特的優(yōu)勢在哪里?下面我們就來介紹FPGA,一起了解FPGA的優(yōu)勢。

2023-03-21 11:08:14 3774

3774 FPGA和外圍接口-基礎(chǔ)版

2023-05-22 10:57:24 568

568

電子發(fā)燒友App

電子發(fā)燒友App

評論