在數(shù)字系統(tǒng)設(shè)計中,我們傳統(tǒng)上都認(rèn)為,應(yīng)該對所有的觸發(fā)器設(shè)置一個主復(fù)位,這樣將大大方便后續(xù)的測試工作。所以,在所有的程序中,我往往都在端口定義中使用同一個reset信號(其實好多時候根本就沒有用到)。所以,當(dāng)看到文檔中提到,“不建議在FPGA設(shè)計中使用全局復(fù)位,或者說應(yīng)該努力避免這種設(shè)計方式”時,許多設(shè)計人員(包括我)都會覺得非常難以理解,這種設(shè)計思想跟我們通常的認(rèn)識是相沖突的!

繼續(xù)讀下去,不知不覺發(fā)現(xiàn)這個白皮書講的還真是在理。接下來把我的個人理解講述一下。

1.全局復(fù)位是不是關(guān)鍵時序?

全局復(fù)位信號一般由以下三種途徑獲得:

1. 第一種,最常見的,就是用一個復(fù)位按鈕產(chǎn)生一個復(fù)位信號接到FPGA的全局復(fù)位管腳上。它的速度顯然是非常慢的(因為是機(jī)械結(jié)構(gòu)),而且存在抖動的問題。

2. 第二種是上電的時候由電源芯片產(chǎn)生的,如TI的TPS76x系列的電源系統(tǒng)一般都可以產(chǎn)生復(fù)位信號,供主芯片上電復(fù)位使用。

3. 第三種是由控制芯片產(chǎn)生的復(fù)位脈沖,這個是我們設(shè)計人員可以方便使用程序控制的。

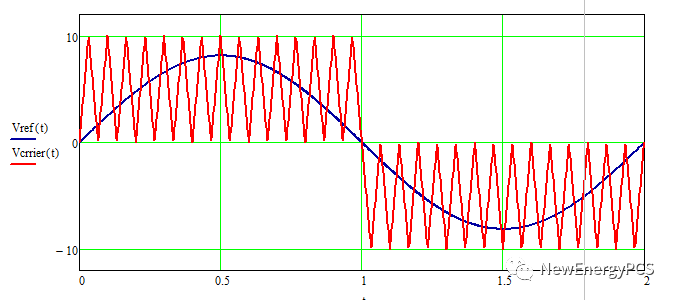

在這些情況下,復(fù)位信號的變化與FGPA芯片內(nèi)部信號相比看起來是及其緩慢的,例如,復(fù)位按鈕產(chǎn)生的復(fù)位信號的周期至少是在毫秒級別的,而我們FPGA內(nèi)部信號往往是納米或者微秒級別的。復(fù)位信號的頻率是如此之低,以至于我們?nèi)蝿?wù)它不屬于關(guān)鍵時序(not timing-critical)。即使是對此類信號進(jìn)行時序約束,約束的周期也是非常長的。全局復(fù)位脈沖的周期遠(yuǎn)大于時鐘周期,所以傳統(tǒng)意義上假設(shè)FPGA芯片中所有的觸發(fā)器都能夠得到有效的復(fù)位。

然而,隨著FPGA性能和工作頻率的快速提高,這種假設(shè)開始不再成立。此時,全局復(fù)位信號的產(chǎn)生開始成為時序關(guān)鍵的問題。

在Xilinx 的FPGA器件中,全局的復(fù)位/置位信號(Global Set/Reset (GSR))(可以通過全局復(fù)位管腳引入)是幾乎絕對可靠的,因為它是芯片內(nèi)部的信號。如果所有的觸發(fā)器都使用這一全局復(fù)位信號,則GSR信號將形成一個高扇出的網(wǎng)絡(luò)(有興趣的朋友可以在綜合工具中查看)。雖然在啟動順序中,它可以與一個用戶自定義的時鐘進(jìn)行同步,但是想讓它與設(shè)計中的所有時鐘信號進(jìn)行同步是不可能的;比如,一個Xilinx FPGA中可能含有多個DLL/DCM/PLL時鐘處理模塊,每個模塊又可以產(chǎn)生多個時鐘信號,在各個模塊內(nèi)部進(jìn)行時鐘信號的同步是可行的,然而想讓所有時鐘信號同步是完全不可行的——從DCM的分布上就可以看出來:中間相隔的長距離布線對高頻時鐘信號的延時顯著增大,進(jìn)行同步自然無法做到。于是,在時鐘信號頻率越來越高的情況下,全局復(fù)位信號便開始成為時序關(guān)鍵。解釋如下:

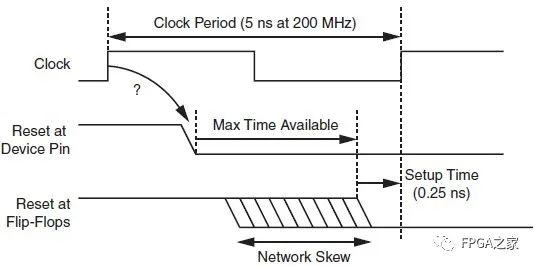

圖1被兩個時鐘信號的邊沿截斷的復(fù)位信號的時序圖

圖1 給出了被兩個時鐘信號的邊沿截斷的復(fù)位信號的時序圖,第一行是時鐘信號,第二行是器件復(fù)位管腳上的信號,第三行是到達(dá)觸發(fā)器復(fù)位端的復(fù)位信號。為了使觸發(fā)器進(jìn)行有效的復(fù)位,在有效的時鐘邊沿到來之前,復(fù)位信號應(yīng)該被保持至少一個建立時間(時鐘信號的簡歷時間)。可以看出,時鐘信號的頻率越高,用來分配復(fù)位信號的可用時間就越少。而且考慮到全局復(fù)位信號往往是高扇出的的網(wǎng)絡(luò),想在這個龐大的網(wǎng)絡(luò)中滿足苛刻的時序要求是非常困難的。在經(jīng)常使用的異步復(fù)位的設(shè)計中,更沒有辦法來保證所有的觸發(fā)器都可以在同一個時鐘邊沿被釋放,即使存在用來分配復(fù)位信號的可用時間。這一點從圖2中可以看出。

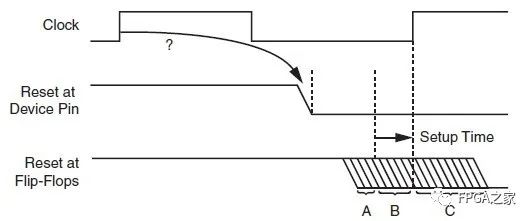

圖2 異步設(shè)計中復(fù)位信號的時序圖

圖2給出了異步設(shè)計中復(fù)位信號的時序圖。可以看出,在A時刻產(chǎn)生的復(fù)位信號,將在第一個時鐘信號的有效邊沿產(chǎn)生,而在C時刻產(chǎn)生的復(fù)位信號將在第二個有效的時鐘信號邊沿產(chǎn)生。在B時刻,觸發(fā)器很難有效定義哪一個復(fù)位信號是有效的,這將導(dǎo)致亞穩(wěn)態(tài)的產(chǎn)生。

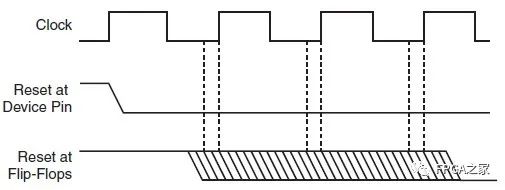

隨著時鐘信號頻率的增高和器件規(guī)模增大帶來的潛在的時鐘偏移,在同一個時鐘邊沿對所有的觸發(fā)器進(jìn)行是否已經(jīng)幾乎是不可能的了。圖3顯示了高時鐘頻率下的復(fù)位時序圖。

圖3 高時鐘頻率下的復(fù)位時序

全局復(fù)位對時序的要求真的很關(guān)鍵嗎?

好消息是,在絕大多數(shù)設(shè)計中(白皮書說是超過99.99%?應(yīng)該是老外寫文檔的習(xí)慣吧),復(fù)位信號的時序是無關(guān)緊要的——通常情況下,大部分電路都能夠正常工作。然而,只要你曾經(jīng)遇到過復(fù)位信號不正常導(dǎo)致電路無法正確工作的情況,那么可以說你“幸運”地遇到了那0.01%的復(fù)位信號異常的情況。圖4給出了一個流水線復(fù)位的情況。

圖4 流水線的復(fù)位

在流水線中,假如數(shù)據(jù)都是完全順序處理的(即不存在反饋、環(huán)路等情況),則主復(fù)位信號是何時產(chǎn)生的是完全無關(guān)緊要的。經(jīng)過幾個周期的流水線操作,任何不正常的數(shù)據(jù)狀態(tài)都將被從系統(tǒng)中“沖出”流水線,這是很容易理解的。事實上,在正常的流水線操作中,我們也很少會用到復(fù)位操作的,因為這是完全沒有必要的。即使是在仿真環(huán)境中,我們也往往會在測試程序中對初始狀態(tài)進(jìn)行配置,從而將所有的未知狀態(tài)從系統(tǒng)中清除出去,使得系統(tǒng)中的所有輸入都變?yōu)橛行У臄?shù)據(jù)。

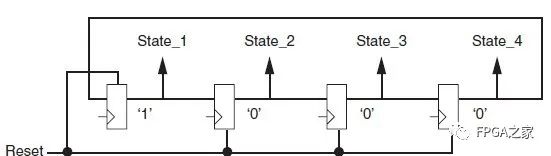

然而,在圖5所示的獨熱碼狀態(tài)機(jī)的情況下,復(fù)位信號的時序卻的的確確成為了系統(tǒng)正常工作的關(guān)鍵因素之一。

圖5 獨熱碼狀態(tài)機(jī)的復(fù)位

圖5 的例子中演示了一個簡單的的獨熱碼狀態(tài)機(jī)的復(fù)位示意圖。圖中清晰地顯示了復(fù)位失敗的潛在可能性。如果第一個含有獨熱碼的觸發(fā)器比第二個觸發(fā)器提前釋放一個時鐘周期,則其含有的獨熱碼將丟失,整個狀態(tài)機(jī)將永遠(yuǎn)進(jìn)入無效狀態(tài)(cold)。減小這種情況發(fā)生的概率往往可以通過使用相鄰的觸發(fā)器構(gòu)成狀態(tài)機(jī)來解決(使用本地復(fù)位網(wǎng)絡(luò),則信號的失真度較低),但前提是時序約束中的建立時間必須滿足。此外,如果所有的觸發(fā)器無法在同一個時鐘信號的有效邊沿被釋放,,則一個已經(jīng)編碼的狀態(tài)機(jī)可能會調(diào)變進(jìn)入未知狀態(tài),包括非法狀態(tài),造成電路無法正確工作。所以,在包含反饋通路的電路設(shè)計者,需要對復(fù)位信號的時序要求進(jìn)行仔細(xì)考慮。

事實上,不存在反饋通路的電路是完全不需要使用復(fù)位信號的。例如,在數(shù)字信號處理應(yīng)用中,有限脈沖響應(yīng)濾波器(FIR)就不存在反饋通路:只有在有效數(shù)據(jù)填滿所有節(jié)拍時,濾波器才會輸出采樣值,否則不輸出任何數(shù)據(jù);所以對節(jié)拍寄存器進(jìn)行復(fù)位是毫無意義的。然而,在有限脈沖響應(yīng)濾波器(IIR)中,存在反饋通路,如果在一個不可靠的復(fù)位信號下對節(jié)拍寄存器進(jìn)行復(fù)位并產(chǎn)生一個偽信號輸出,則濾波器輸出會受到顯著的影響。最壞的情況下,偽信號帶來的不穩(wěn)定將導(dǎo)致整個濾波器陷入崩潰狀態(tài)。

如何自動覆蓋99.99%的情況

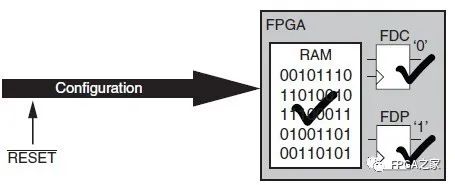

圖6 FPGA配置

當(dāng)一個Xilinx的FPGA芯片被重新配置時,每一個單元都將被初始化,如圖6所示。在某種意義上講,這是一個上電之后的“終極的”全局復(fù)位操作,因為它不僅僅是對所有的觸發(fā)器進(jìn)行了復(fù)位操作,還初始化了所有的RAM單元。隨著Xilinx FPGA芯片內(nèi)部的嵌入式RAM資源越來越多,這種“終極的”全局復(fù)位操作越來越有意義。對所有的RAM單元進(jìn)行預(yù)定義,在軟件仿真和實際操作中都是非常有幫助的,因為這樣避免了在上電時采用復(fù)雜的啟動順序來清除存儲單元內(nèi)容的操作。

隨著Xilinx的FPGA芯片越來越多的嵌入處理器內(nèi)核,比如MicroBlaze軟核、ARM和PowerPC硬核等,這種特性使得所有的程序和數(shù)據(jù)空間在處理器內(nèi)核執(zhí)行第一條指令之前都已經(jīng)被預(yù)定義,則原來那種靠燒寫昂貴的可編程資源來僅僅復(fù)位觸發(fā)器的操作變得毫無意義了。開發(fā)過程中所使用的仿真工具也應(yīng)當(dāng)具有模擬此操作的能力(即我們通常所說的“上電復(fù)位”),這樣在后續(xù)的設(shè)計中就可以避免使用可有可無的復(fù)位操作了。

其余0.01% 情況的設(shè)計準(zhǔn)則

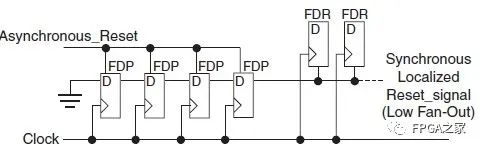

最重要的事情是使用某些準(zhǔn)則來處理設(shè)計中的復(fù)位操作,并且這些準(zhǔn)則在設(shè)計審查階段就應(yīng)該被完全考慮到。可以使用一個局部的高性能的復(fù)位網(wǎng)絡(luò)來控制僅僅需要局部復(fù)位的觸發(fā)器。圖7給出了一個這種局部復(fù)位的示意圖。這種電路的優(yōu)點在于,它所提供的復(fù)位效果與外接全局復(fù)位信號的效果是一致的。

圖7 局部復(fù)位示意圖

在器件配置或者異步復(fù)位時,鏈中的所有觸發(fā)器都被預(yù)設(shè)為1。幾乎在這同時,鏈中的最后一個觸發(fā)器驅(qū)動局部復(fù)位網(wǎng)絡(luò)并向其發(fā)送一個有效復(fù)位信號。隨著全局復(fù)位/置位信號或異步復(fù)位信號的釋放,整個移位寄存器鏈開始在每個時鐘周期被填充為0。

鏈中觸發(fā)器的數(shù)目決定了局部復(fù)位網(wǎng)絡(luò)所需要的復(fù)位脈沖的最小寬度。最后的結(jié)果是,鏈中最后一個觸發(fā)器從高跳變到低,而局部復(fù)位信號的釋放與時鐘周期同步。被復(fù)位的觸發(fā)器可以采用同步置位(synchronous set (FDS))或者同步復(fù)位(synchronous reset (FDR)),即構(gòu)成了完整的同步設(shè)計,而接下來的時序規(guī)范和分析也將容易得多。

復(fù)位操作消耗的資源遠(yuǎn)比你想象的要多

在FPGA設(shè)計中,我們往往習(xí)慣在HDL文件的端口聲明中加入一個reset信號,卻忽略了它所帶來的資源消耗。仔細(xì)分析一下,竟會有如此之多的影響:

? 復(fù)位網(wǎng)絡(luò)需要占用布線資源

導(dǎo)致其余信號的布線信號受到影響,降低了它們布線的自由度。

增加的布線網(wǎng)絡(luò)往往需要使用更高速率的芯片。

復(fù)位網(wǎng)絡(luò)占用大量布線資源,使得Place&Route的時間大大增加,如果電腦是老爺機(jī)則讓人十分痛苦。

? 復(fù)位信號需要占用大量的邏輯資源

復(fù)位信號需要使用觸發(fā)器的專用復(fù)位管腳。

可操作的復(fù)位信號往往導(dǎo)致D觸發(fā)器的輸入前增加額外的門操作或?qū)S玫膹?fù)位信號輸入。

增大整個設(shè)計 的尺寸。

額外的邏輯消耗降低了系統(tǒng)的性能。

? 阻止了使用高效特征,如Xilinx FPGA特有的SRL16E 移位寄存器。

SRL16E可以在一個LUT中實現(xiàn)多達(dá)16個觸發(fā)器。

SRL16E 實現(xiàn)的虛擬觸發(fā)器不支持復(fù)位操作,這使得HDL設(shè)計中帶有復(fù)位操作時,綜合工具無法有效利用SRL16E 資源。有可能增加多達(dá)16倍的資源消耗。

在Xilinx網(wǎng)站的白皮書 WP275 .pdf:《Get your Priorities Right - Make your Design Up to 50% Smaller》中提到了復(fù)位信號是如何影響FPGA資源利用率的,有興趣的朋友可以去讀一下。

? ? ? 總結(jié)一下,Xilinx FPGA設(shè)計中一般不需要插入全局復(fù)位網(wǎng)絡(luò),這樣我們在寫程序的時候就不必每個模塊都加入reset端口了,既方便了程序書寫,又減小了編譯時間,還減少了資源占用。絕大多數(shù)情況下,重配置或者上電過程中,所有的觸發(fā)器和RAM等都可以被預(yù)設(shè)初始狀態(tài),所以全局復(fù)位是完全沒有必要的,因為所有的信號都已經(jīng)具有明確的初值!Xilinx FPGA都已經(jīng)經(jīng)過充分驗證,所以掃描邏輯和運行測試向量都不再是必須的操作,全局復(fù)位作為這些操作的一部分自然也不再需要。

電子發(fā)燒友App

電子發(fā)燒友App

評論