杯賽題目:基于蜂鳥E203 RISC-V處理器內核的SoC設計

參賽要求:研究生組/本科生組

賽題內容:

基于芯來科技的開源蜂鳥E203 Demo SoC進行擴展,在限定的可編程邏輯平臺上構建面向專用應用領域(譬如人工智能、信息安全、工業控制等)的SoC,進而完成一定實際應用。要求在所搭建的SoC中實現專門的硬件加速器以提高系統整體性能,所實現的系統具有創新性、實用性以及市場應用前景。

團隊介紹

參賽單位:電子科技大學

隊伍名稱:第N隊

指導老師:路志剛

參賽隊員:朱俊宛、羅揚、岳修立

總決賽獎項:三等獎

1. 項目簡介

隨著信息化和數字化社會的發展,人們對信息安全和保密的重要性認識不斷提高,信息加密算法也在不斷的發展進步之中。SM4密碼算法是國家密碼管理局正式的《祖沖之序列密碼算法》等6項密碼行業標準之一。本項目基于開源E203處理器在FPGA開發板上對國產密碼算法SM4算法進行實現和優化,并實現了對字符串的加密與解密。

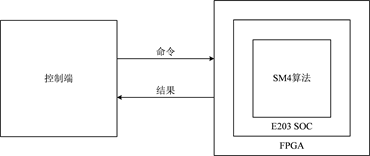

1.1 系統框架

系統控制端通過串口通信FPGA開發板發送命令:操作類型(加密解密)、操作數據(明文密文)、密鑰。FPGA上的E203 SoC接收來自控制端的命令并運行硬件加速后的SM4算法程序進行處理,處理后的結果通過串口通信返回給控制端,如下圖所示。

1.2 SM4算法原理

1.2.1 概述

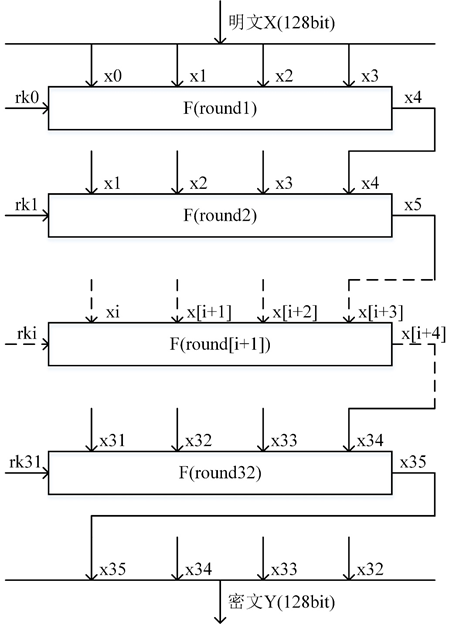

SM4算法是一種分組密碼算法。其分組長度為128bit,密鑰長度也為128bit。加密算法與密鑰擴展算法均采用32輪非線性迭代結構,以字(32位)為單位進行加密運算,每一次迭代運算均為一輪變換函數F。SM4算法加/解密算法的結構相同,只是使用輪密鑰相反,其中解密輪密鑰是加密輪密鑰的逆序。

SM4算法的整體結構如圖:

1.2.2 輪函數

整體的加密函數F為:

x(i+4)=F(x(i),x(i+1),x(i+2),x(i+3),rk(i))=x(i)?T(x(i+1)?x(i+1)?x(i+2)?x(i+3)?rk(i))

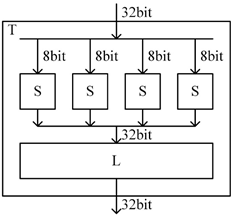

其中T為一個合成置換,由非線性變換S和線性變換L復合而成,如下圖。

非線性變換S由具有256個固定的8bit數據的S盒構成,S盒的數據均采用16進制。輸入的8bit數據作為S盒中地址的索引,地址中所包含的8bit數據即為S盒的輸出。非線性變換S函數表達式可以表示為:

B=(b1,b2,b3,b4)=S(A)=(sbox(a1),sbox(a2),sbox(a2),sbox(a2))

線性變換L的公式如下:

C=L(B)=B?(B?2)?(B?10)?(B?18)?(B?24)

其中B為非線性變換得到的字。

1.2.3 輪密鑰

已知加密密鑰:MK=(MK0,MK1,MK2,MK3),系統參數:FK=(FK0,FK1,FK2,FK3) ,固定參數:CK=(CK0,CK1,??,CK31) 。

輪密鑰rki即為密鑰擴展的結果,由加密密鑰擴展生成,過程如下:

首先:

(K(0),K(1),K(2),K(3))=(MK0?FK0,MK1?FK1,MK2?FK2,MK3?FK3)

然后對于i=0,1,??,31:

rk(i)=K(i+4)=K(i)?T'(K(i+1)?K(i+1)?K(i+2)?K(i+3)?CK(i))

其中變換T'與輪函數的T變換基本相同,只是將其中的線性變換L改為:

L'(B)=B?(B?13)?(B?23)

1.3 協處理器加速設計

1.3.1 軟硬件功能劃分

硬件功能:利用協處理器實現SM4算法中的密鑰拓展過程與加解密過程。

軟件功能:調用協處理器實現密鑰拓展過程與加解密過程,并對過程進行控制。

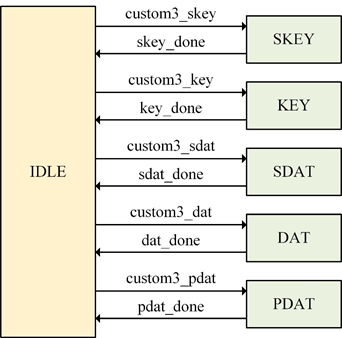

1.3.2 狀態轉換

根據SM4算法原理及軟硬件功能劃分,六個狀態,分別為初始狀態(IDLE)、密鑰加載狀態(SKEY)、密鑰拓展狀態(KEY)、輸入加載狀態(SDAT)、加解密運算狀態(DAT)、輸出返回狀態(PDAT)。

當有相應的指令標識位置1時,狀態機將從初始狀態進入相應的指令狀態。當相應的狀態完成標識位置1后,狀態機將從相應的指令執行狀態進入初始狀態。狀態轉換單元示意圖如下。

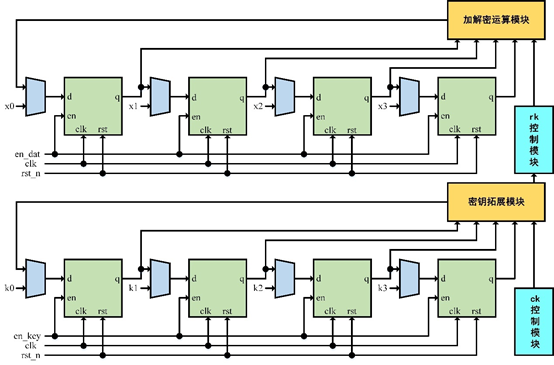

1.3.3 數據運算

數據運算部分主要是在根據協處理器當前的狀態進行相應的運算操作以實現SM4算法。數據運算單元示意圖如下。

1. 當處于密鑰加載狀態(SKEY)時,協處理器會將CPU送過來的與系統參數FK異或過的初始密鑰k0、k1、k2、k3加載到下方4個寄存器中。

2. 當處于密鑰拓展狀態(KEY)時,k0、k1、k2、k3會進行32輪非線性迭代運算,在迭代過程中生成k4-k35,即輪密鑰rk0-rk31,并存儲到rk控制模塊之中。

3. 當處于輸入加載狀態(SDAT)時,協處理器會將CPU送過來的初始輸入x0、x1、x2、x3加載到上方4個寄存器中。

4. 當處于加解密運算狀態(DAT)時,x0、x1、x2、x3會進行32輪非線性迭代運算,會根據此時源操作數1的值決定輪密鑰rki的使用順序,為0對應于加密操作,為1對應于解密操作。迭代過程完成后將得到x31、x32、x33、x34,即運算結果。

5. 當處于輸出返回狀態(PDAT)時,協處理器會通過結果反饋通道nice_rsp_rdat將運算結果返回給CPU。

2. 仿真與測試

2.1 功能仿真

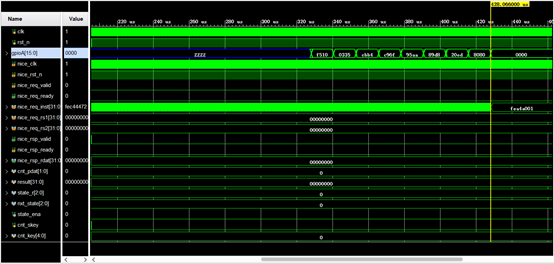

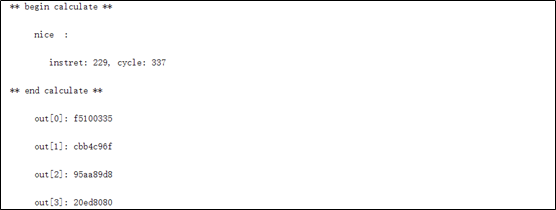

2.1.1 SM4算法純軟件實現功能仿真

vivado仿真波形:

Tcl控制臺結果:

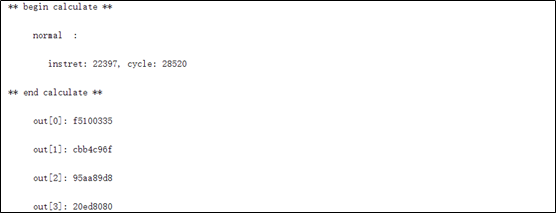

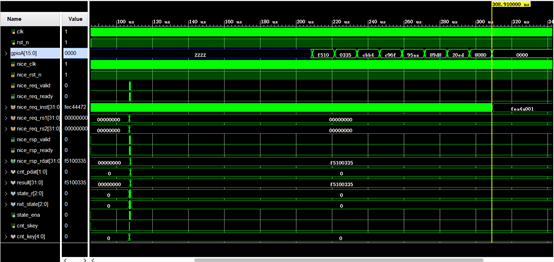

2.1.2 SM4算法協處理器加速實現功能仿真

vivado仿真波形:

Tcl控制臺結果:

2.1.3 協處理器加速效果

對比兩次仿真結果得到,協處理器對SM4算法的加速效果為:28520 / 337 = 84.6(倍)

2.2 整體測試

整體測試的實物連接如圖

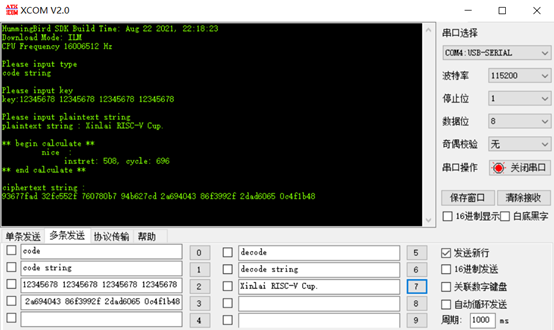

2.2.1 字符串加密

對字符串“Xinlai RISC-V Cup”進行加密,密鑰為:0x1234578 1234578 1234578 1234578。結果如圖。

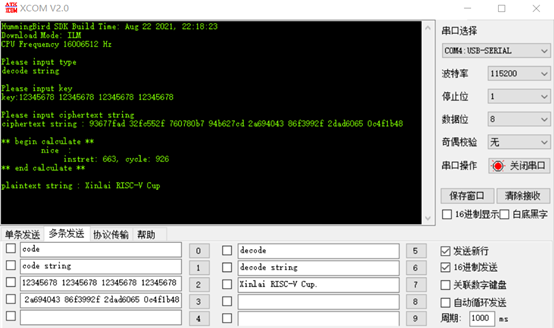

2.2.2 字符串解密

將加密得到的密文 0x93677fad 32fc552f 760780b7 94b627cd 2a694043 86f3992f 2dad6065 0c4f1b48 進行解密操作,結果如圖。得到解密結果為:“Xinlai RISC-V Cup”。驗證了加密結果的正確性,完成了對字符串的加密解密,實現系統的預設功能。

3. 參賽體會

3.1 參賽感受

在三個多月的學習與實踐之中,經過VERLIOG的學習、VIVADO的使用、FPGA開發板的學習、RISK_V的學習、E203 SoC的移植、SM4算法的學習、協處理器的學習與應用等過程,基本完成了基于E203 處理器內核的SM4算法硬件加速。從一個剛開始學習的小白,一步步摸索前進。在不斷遇到問題,解決問題的過程中,加深了對集成電路行業的理解,提升我們的軟件設計能力。

集創賽作為全國性的頂尖賽事,匯集了來自全國各地各高校的優秀大學生。讓我們在比賽過程中能夠與如此多優秀的同齡人同臺競技,相互交流,極大拓展了自己的視野與能力。非常感謝集創賽賽事組委會的工作人員和老師們的組織與付出,讓我們有機會參與到這樣一個充分展示風采的平臺。

3.2 后續計劃

1.加入其他算法(例如SM3算法)進行交互,進一步提升其加密效果。

2.對輸入,輸出及控制系統進行進一步的優化與拓展,使用上位機來傳輸數據流和控制。

審核編輯 :李倩

?

電子發燒友App

電子發燒友App

評論