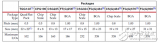

Critical Link公司的某客戶需要針對多個應用開發一個擴頻無線電收發器。該客戶已經開發出一套算法,準備用于對信號進行調制和解調,但他們卻缺少構建完整系統的資源和專業知識。客戶希望利用軟件定義無線電(SDR)系統的靈活性優勢。本文將探討如何基于德州儀器(TI)的OMAP-L138 DSP+ARM處理器與FPGA來實現該系統。平臺Critical Link選擇其MityDSP-L138F嵌入式系統模塊作為SDR的基礎,因為該模塊不僅具有很強的處理能力,而且可以為客戶節省大量的預先設計成本。MityDSP-L138F模塊具有一個TI的OMAP-L138DSP+ARM處理器,該處理器集成了一個456MHz ARM9處理內核和一個456MHz TMS320C674x DSP內核。此外,該模塊還包含了Xilinx公司的Spartan-6 LX16 FPGA、NAND和NOR閃存以及DDR2存儲器。出于原型考慮,該設計使用了TI針對無線電的高速ADC與DAC評估套件。此外,它還需要能夠在60MHz采樣頻率轉換的數據轉換器。針對A/D轉換器,該設計選用了TI的ADS5562。該轉換器具有16位精度,可以以80Msps采樣速率進行轉換。因為擴頻無線電需要將信號從背景噪聲中抽離,所以高動態范圍對于這種無線電來說非常重要。對于DAC,該平臺選用了TI的THS5671。這是一款14位125Msps差分電流輸出DAC。負責本項目的客戶為該系統提供的前端設計如圖所示。?[[wysiwyg_imageupload:454:]]圖:客戶提供的前端設計。數據傳送問題許多基于DSP的應用要求具有高速數據傳輸功能,以使系統能夠采集和處理數據,或者將數據傳送到外設。通常,數字信號處理器都包含了異步地址/數據總線,以使處理器能夠讀寫外設。這些接口可以滿足低速傳送數據的要求,但是在高速情況下卻會成為瓶頸。OMAP-L138 DSP+ARM處理器具有一個稱為外部存儲器接口A(EMIFA)的地址/數據總線。EMIFA允許對外部存儲器或設備進行異步尋址,并含有若干控制引腳,以滿足不同等待狀態和傳輸寬度等等要求。因為該接口具有很強的通用性,所以每次事務處理都可以利用多個時鐘周期來完成。例如,最小的讀取周期需要每16位3個周期。在100MHz下運行EMIFA,假設總線上沒有其他數據,可得到的數據傳輸速率最大為66MB/s。在總線上進行交錯讀寫會顯著地降低傳輸速率,因為這必須增加額外的轉換周期。OMAP-L138處理器還包括了一個更為專用的接口,即通用并行端口(uPP)。該接口專門用來將大量數據連續送入處理器內存或從其中讀出。uPP的傳輸速率為每時鐘周期1個數據字(8位或16位);或者針對雙數據速率為每時鐘周期2個數據字,但是時鐘速率必須減半。uPP時鐘速率可以高達處理器時鐘速率的一半。對于在300MHz下運行的OMAP-L138處理器,uPP時鐘可以達到75MHz。這使吞吐量可以達到150MB/s。OMAP-L138處理器實際包括2個uPP接口,每個都可以單獨配置。這允許我們為應用建立一個傳輸端口和一個接收端口,從而消除單一總線上的資源爭用問題。從硬件角度看,uPP接口是一種非常簡單的同步數據接口。它包含一個時鐘引腳、數據引腳和若干控制引腳,用于指明有效數據和起始/等待條件。事實上,該接口可以與一些并行ADC和DAC實現無縫連接。架構因為我們的SDR需要與DSP之間進行高速數據傳送,所以我們選擇使用uPP端口來實現FPGA接口。我們使用一個端口作為接口的發送端,使用另一端口作為接收端。事實上,該處理系統可以同時進行發送和接收,盡管這并非系統要求。這個功能的優勢在于,它允許我們在發送器和接收器之間建立循環,以進行大量的測試和調試工作。對于一個10MHz載波來說,這種調制所需的處理特性,使系統過多地將全部處理任務在OMAP-L138處理器的DSP中完成。在速度較慢的應用中,DSP可以單獨滿足數據速率的要求,但由于客戶要求以更高的速率發送數據,所以我們需要使用FPGA來執行部分處理任務。FPGA尤其擅長以非常高的頻率執行重復任務,因此,我們選擇在FPGA中執行初始解調和基帶處理。這樣,我們就可以大量減少DSP中的數據并降低DSP的數據速率。在發送側,DSP可以預先計算最終的射頻信號,以便將有效負載數據的編碼時間降至最短。因此,FPGA僅僅將發送波形數據從uPP端口發送到DAC。事實上,不使用FPGA也可以完成這項工作,但是我們在設計系統時仍將FPGA加入,以便在需要時使用。FPGA的雙端口RAM中包含一個正弦或余弦查找表,用于合成接收機的本機振蕩器信號。FPGA中的乘法器/累加器用于根據要求解調信號。發送處理鏈當ARM微處理器上的軟件向DSP發出傳輸消息包時,發送過程將會啟動。DSP對數據進行編碼,使其成為擴頻調制序列,并將其編入一個預先計算的已調制正弦波查找表。然后,DSP使用uPP的內置DMA引擎建立一個DMA傳輸,用以將數據從DSP存儲器傳送到DAC。FPGA則起到中間調解作用,負責向DAC和uPP提供可編程時鐘,用于設置發送采樣率。接收處理鏈接收流程連續運行。ADC樣本被同步送入FPGA——通過將輸入樣本與正交正弦和余弦波形相乘并積分,對數據進行基帶處理,從而以較低的數據速率向DSP提供同相和正交樣本。這些樣本被uPP DMA引擎以DMA方式送入DSP存儲器,再由DSP處理剩余的擴頻解調處理步驟。一旦信號被解調,得到的數據包將使用TI的DSPLink處理器之間通信庫傳送回ARM處理器。ARM軟件接收解碼數據,并通過命令接口將數據呈現給用戶。使用FPGA執行接收器初始基帶處理能夠釋放足夠的DSP處理能力,從而輕松完成剩余的解調和解碼工作。如果系統中的輸入信號采樣率顯著低于60MHz,則DSP可不借助FPGA的力量,獨自執行基帶處理任務。該系統的初始工作使用了一個低頻段(幾十或幾百kHz)的載頻。在初始實施過程中,FPGA僅負責將數據發送至DSP,由DSP執行所有的解調功能。這種方式很奏效,但是無法達到更高采樣率應用的要求。通過在FPGA中實施基帶處理,我們可以在全采樣率下進行數字基帶處理和濾波,從而改善系統的噪聲性能:這在欠采樣下是無法做到的。本文小結該項目實現的原型系統已經為多個應用實施過概念驗證。與理想擴頻無線電的理論性能相比,該系統的性能非常優異。TI OMAP-L138 DSP+ARM處理器與FPGA的結合,實現了具有出色性能的高性價比解決方案。將DSP的部分處理負載分配給FPGA,使系統可以使用低成本、低功耗的處理器來構建,而不是由GHz級的DSP處理所有工作。uPP接口支持簡單的FPGA接口功能,并且與其他可用的DSP接口相比,具有明顯的性能優勢。使用uPP中的DMA進行數據傳送,可以進一步釋放DSP資源,將DSP周期用于更加重要的工作。在OMAP-L1x平臺中加入ARM處理器后,便可使用嵌入式Linux提供通信基礎設施,來管理系統中的用戶界面和所有的內務處理功能。此外,使用SD卡、USB驅動器或者以太網連接,可以對系統軟件(ARM、DSP和FPGA)進行現場升級。因此,SDR系統的靈活性可以充分滿足處理算法的發展要求。David A. Rice技術總監Critical LinkJoseph Coombs應用工程師德州儀器

基于DSP和賽靈思Spartan-6的SDR系統設計與實現

- dsp(343841)

- SDR(50129)

相關推薦

Spartan-6 FPGA是否需要設計中的上電復位電路

您好Xilinx社區,有人能否就Spartan-6 FPGA是否需要設計中的上電復位電路給出明確的答案?在附圖中,我們的設計中有這個上電復位電路。然而,我們遇到了電路問題,并決定在我們的設計中將

2019-04-18 10:15:45

Spartan-6 XC6SLX25 FTG256A和Spartan-6 XC6SLX25 FTG256B的差異是什么

嗨,我想知道是否有關于它們之間[fly]的差異的[/fly]技術文檔Spartan-6 XC6SLX25 FTG256A和Spartan-6 XC6SLX25 FTG256B看起來,差異是芯片修訂版

2019-07-02 10:45:31

Spartan-6器件的可用性

有誰知道更多關于Spartan-6 XC6SLX150的可用性?我知道周圍有工程樣品,但我無法獲得最終商業版的任何交貨時間。謝謝,羅伯特以上來自于谷歌翻譯以下為原文Anyone knows more

2019-05-24 13:15:09

Spartan-6的QDR接口能連接到MCB引腳嗎

親愛的論壇,我正在處理將** II SRAM連接到Spartan-6 FPGA的問題。我不是斯巴達IP核的專家,但我意識到Spartan-6沒有預見到的QDR接口。但是我確信它可以做到。我遇到的唯一

2019-05-22 07:16:30

Spartan 6是否支持SDR SDRAM?

嗨,Spartan 6是否支持SDR SDRAM(單數據輻射SDRAM)?在ISE存儲器接口生成器中,沒有選擇SDR SDRAM的選項。有沒有辦法在斯巴達6中使用SDR SDRAM

2019-04-16 09:33:03

Spartan-3A與Spartan-3AN 低成本誰更有優勢?

設計的CCD線陣相機,基于FPGA的,現在選用一款低成本的賽靈思的FPGA芯片,Spartan-3A與Spartan-3AN到底用哪款好呢?

2014-04-02 11:23:40

賽靈思7系列采用FPGA電源模塊

。ROHM與安富利公司共同開發賽靈思7系列FPGA及Zynq?–7000 All Programmable SoC的評估套件Mini-Module Plus 用的電源模塊。安富利公司已經開發出多款賽靈思

2018-12-04 10:02:08

賽靈思Spartan開發板使用困境記錄 精選資料分享

賽靈思Spartan開發板使用困境記錄原理圖和接口主要是對照核心板的原理圖,一般的接法就是賽靈思系列的單片機,連接好電源和下載器,記得預先安好驅動,驅動安裝成功與否能夠在設備管理器處查看。作者困境

2021-07-13 08:42:10

賽靈思FPGA原理圖例子之s3astarter

`賽靈思FPGA原理圖例子之s3astarter 賽靈思一向是FPGA領域里的領先者,運用FPGA需要深入的理解它的工作原理,小編親子整理了s3astarter 的經典fpga原理圖分享給電子工程師們。賽靈思FPGA原理圖例子之s3astarter [hide][/hide]`

2012-03-16 10:41:19

賽靈思FPGA對DLP數字影院投影儀產生了哪些影響?

賽靈思公司(Xilinx)日前宣布NEC子公司NEC Display Solutions有限公司的三款DLP數字影院投影儀產品,均采用了賽靈思Virtex?-5 FPGA系列產品。

2019-08-19 07:12:03

賽靈思FPGA該怎么應對內窺鏡系統架構的挑戰?

什么是賽靈思FPGA?如何幫助內窺鏡制造商克服復雜的設計約束,生產出極具競爭優勢的產品?如何幫助他們成功構建外形小巧的低功耗內窺鏡攝像頭、高性價比的攝像機控制單元(CCU),以及多功能、低成本的圖像管理設備?

2019-09-17 06:31:55

賽靈思Virtex-6 HXT FPGA ML630提供參考時鐘電路圖

賽靈思Virtex-6 HXT FPGA ML630評估套件采用SiTime電子發燒友振具體型號為:SIT9102AI-243N25E200.0000,而目前針對這一型號sitime推出了抖動更低

2014-11-17 15:07:35

賽靈思公司亞太區銷售與市場副總裁給XILINX客戶的信

推向一個又一個新的高度。與此同時,賽靈思還將一如既往地不斷為您提供最好的產品、技術和支持,期待著在激烈的市場競爭中與您密切合作,借助賽靈思成功的28nm產品和技術優勢, 強強聯手,實現雙方的共贏!順祝商祺!楊飛 賽靈思公司亞太區銷售與市場副總裁

2012-03-22 15:17:12

FPGA LX9 MicroBoard成為學習FPGA的另一低成本方法

發行很久了,現在機會來了。對你來說,使用Spartan-6 MicroBoard是一個完整的低成本的方法,可以熟悉賽靈思Spartan-6 FPGA的開發。它使用同一個USB端口作為電源和JTAG編程

2017-02-10 17:12:21

FPGA設計之浮點DSP算法實現【賽靈思工程師作品】

FPGA設計之浮點DSP算法實現,DSP算法是很多工程師在設計過程中都會遇到的問題,本文將從FPGA設計的角度來講解浮點DSP算法的實現。FPGA設計之浮點DSP算法實現是賽靈思工程師最新力作,資料不可多得,大家珍惜啊1FPGA設計之浮點DSP算法實現[hide][/hide]

2012-03-01 15:23:56

FPGA設計大賽獎品介紹.iPad2+Xilinx Spartan-6開發板

`FPGA設計大賽獎品.蘋果iPad2+賽靈思Xilinx Spartan-6開發板 等你拿,FPGA發燒友、工程師們,心動了么,那就趕快猛戳這里報名吧一等獎獎品:iPad2+Xilinx

2012-04-25 09:32:46

XMC4300從控制器與Spartan-6 FPGA兼容嗎?

我目前正在探索將英飛凌 XMC4300 從控制器與 Xilinx Spartan-6 FPGA 集成到我們項目中的兼容性和通信協議選項。 具體來說,我想了解 XMC4300 是否適用于促進我們在

2024-03-06 07:47:12

Xilinx Spartan-6哦中multiboot的問題

各位道友好,能不能給我講講關于spartan-6如何配置,以此實現多boot的加載?具體想了解如何使用ISE軟件來設置相關選項實現 謝謝了

2013-01-28 10:08:14

Xilinx Vertex-4 DSP應用程序xapp706是否可在Spartan-6上移植

Xilinx Vertex-4 DSP應用程序xapp706是否可在Spartan-6上移植,DSP切片接口已發生變化,我相信樣本中可能需要進行一些代碼更改 - 您是否有這些特定的更改?我是否需要

2019-07-04 15:36:07

Xilinx賽靈思FPGA技術及應用線上公開課

` 本帖最后由 MGJOY 于 2017-4-10 15:07 編輯

本周三,4月12日,賽靈思FPGA技術及應用線上公開課。歡迎大家觀看、學習交流~分享主題【賽靈思FPGA人工智能領域技術及應用】嵌入式視覺領域技術和解決方案機器學習方面的技術和解決方案ADAS/自動駕駛方面的應用`

2017-04-10 15:06:16

Xilinx公司產品導購手冊

Xilinx公司產品導購手冊Xilinx(賽靈思)相關產品介紹? Virtex-6 FPGA(XC6V)? Virtex-5 FPGA(XC5V)? Virtex-II FPGA(XC2V

2012-02-28 16:43:31

“賽靈思”搶樓活動第二輪,中獎樓層公布!

`{:4_122:}{:4_122:}搶樓啦!!“賽靈思”搶樓活動第二輪中獎樓層公布號外號外{:4_104:}:為了答謝各位壇友們的大力支持,我和我的小伙伴們決定在增加5個中獎樓層,讓各位中獎的幾率

2013-10-11 10:40:34

【AD新聞】賽靈思新CEO訪華繪藍圖,7nm ACAP平臺要讓CPU/GPU難企及

的規劃者。”個人資料顯示,Victor Peng于2008年加入賽靈思,在公司產品線和服務方面引領了行業領先的戰略和技術轉型,實現了從28nm,20nm到16nm連續三代核心產品的領導地位,并在集成度

2018-03-23 14:31:40

【PYNQ-Z2申請】基于賽靈思PYNQ-Z2平臺的圖像實時力學測量

PYNQ-Z2平臺完善該項目的開源設計,并進一步提升性能。項目計劃①根據文檔,對賽靈思PYNQ-Z2快速入門②通過學習賽靈思PYNQ-Z2的軟件和系統,了解實際應用案例,熟悉開發過程③基于賽靈思PYNQ-Z2

2019-01-09 14:49:25

為Altium Designer新增Xilinx Spartan-6 FPGA支持

【摘要】:<正>Altium繼續為電子產品設計人員擴大器件選項。目前,最新版Altium Designer可提供Xilinx Spartan-6器件系列的全面支持

2010-04-24 10:07:11

為什么說賽靈思已經遠遠領先于Altera?

Altera和賽靈思20年來都在FPGA這個窄眾市場激烈的競爭者,然而Peter Larson基于對兩個公司現金流折現法的研究表明,賽靈思是目前FPGA市場的絕對領先者。

2019-09-02 06:04:21

什么是賽靈思豐富目標設計平臺?

今年年初,賽靈思率先在FPGA領域提出目標設計平臺概念,旨在通過選用開放的標準、通用的開發流程以及類似的設計環境,減少通用工作對設計人員時間的占用,確保他們能集中精力從事創新性的開發工作。

2019-08-13 07:27:15

使用賽靈思MATLAB & Simulink Add-on插件面向Versal AI引擎設計

賽靈思 MATLAB & Simulink Add-on插件是將 ModelComposer 和 System Generator forDSP完美結合的統一工具。

2021-01-28 06:33:40

回收Xilinx芯片 收購賽靈思芯片

回收Xilinx帶板芯片, 回收工廠賽靈思XILINX系列IC:XC3S1500FGG676EGQ、XC5VLX50-1FFG676、XC5VLX110-1FFG676C

2021-12-17 10:02:19

在spartan-6 GTP中RXRECCLK的抖動是多少

我想知道在spartan-6 GTP中RXRECCLK的抖動是多少。有沒有文件描述這個問題?我打算分發系統時鐘,但我不知道從GTP的RX恢復時鐘的性能。我的想法是:我使用系統時鐘(相當不錯,抖動以下

2019-07-01 13:31:36

在賽靈思FPGA中使用ARM及AMBA總線

國外的融合技術專家展示了一項基于FPGA的數據采集系統,用于合成孔徑成像技術。采用了Xilinx ISE設計軟件,支持ARM AMBA AXI4接口。文風犀利,觀點新穎,FPGA中使用ARM及AMBA總線中不可多得的資料在賽靈思FPGA中使用ARM及AMBA總線[hide][/hide]

2012-03-01 15:48:17

基于賽靈思FPGA的EtherCAT主站運動控制

基于賽靈思的FPGA的EtherCAT主站總線控制 ,論壇有做運動控制這方面的技術嗎?目前我已實現帶32軸同步運行,同步抖動±75ns,控制精度125us。感興趣的可以一起探討下

2018-07-23 12:00:39

基于賽靈思FPGA的卷積神經網絡實現設計

作者:Nagesh Gupta 創始人兼 CEOAuviz Systems Nagesh@auvizsystems.com憑借出色的性能和功耗指標,賽靈思 FPGA 成為設計人員構建卷積神經網絡

2019-06-19 07:24:41

如何實現用于Spartan-6中時鐘選擇的MUX?

你好,我正在使用Spartan-6進行設計。我有一個輸入系統時鐘(UCLK),我將輸入發送到PLL以生成5個不同的輸出:UCLK_IBUFG_inst:IBUFG端口映射(O => iUCLK

2019-11-04 09:11:08

如何利用賽靈思28納米工藝加速平臺開發?

全球可編程邏輯解決方案領導廠商賽靈思公司 (Xilinx Inc.) 宣布,為推進可編程勢在必行之必然趨勢,正對系統工程師在全球發布賽靈思新一代可編程FPGA平臺。和前代產品相比,全新的平臺功耗降低

2019-08-09 07:27:00

如何替換Spartan-6代碼中的BUFGDLL?

嗨!我有一個用于Spartan-3(帶有Opal Kelly XEM3001板)的項目,并嘗試將其移植到Spartan-6(Opal Kelly XEM6001)。大多數事情似乎都有效,除了這部

2019-06-26 08:56:45

開發一個基于Spartan-6的定制FPGA板

嗨, 我想開發一個基于Spartan-6的定制FPGA板,只需FPGA,DDR2 RAM,JTAG和GPIO。稍后我想添加一個RF前端來實現軟件定義的無線電。Xilinx是否有一個程序來幫助個人

2019-05-21 14:03:21

怎么編程atlys Spartan-6?

最近,我再見了Spartan-6。我想要編程。首先,我決定使用它的網站演示,但當我下載,我找不到任何程序文件。我應該怎么編程呢?程序文件是什么類型的?我的意思是我應該在ise中編寫vhdl代碼然后

2019-08-30 08:34:53

推薦用于Spartan-6的SPI Flash

我花了兩個小時為Spartan-6設備尋找支持/推薦的SPI閃存。誰能指出我正確的文件?謝謝以上來自于谷歌翻譯以下為原文I have spent two hours looking

2019-05-29 09:30:32

提交FPGA設計方案,贏取賽靈思FPGA開發板

/activities/fpga/全程參與比賽還有更多獎品等你來拿:一等獎獎品:iPad2+Xilinx Spartan-6開發板 二等獎獎品:Xilinx Spartan-6開發板 三等獎獎品:電子發燒友T恤+賽靈思FPGA雜志/其他小獎品

2012-07-06 17:24:41

玩轉FPGA 賽靈思(xilinx)FPGA設計大賽圓滿結束

三等獎獎品: 電子發燒友T恤+賽靈思小禮品 大賽獲獎名單 一等獎 姚佳毅(yjysdu)——車牌定位號與識別系統 二等獎 馬崇鶴(lerking) ——基于FPGA

2012-09-06 11:52:48

玩轉FPGA 賽靈思(xilinx)FPGA設計大賽獲獎名單!!!

Spartan-6開發板 二等獎獎品: Xilinx Spartan-6開發板 三等獎獎品: 電子發燒友T恤+賽靈思小禮品 大賽獲獎名單 一等獎 姚佳毅(yjysdu)——車牌

2012-09-06 11:54:16

玩轉FPGA,賽靈思FPGA設計大賽開賽啦

與技術學院教授史治國:浙江大學信息與電子工程學系副教授徐文波:畢業于北京郵電大學碩士研究生,FPGA圖書作者活動獎品一等獎二等獎三等獎幸運獎1名5名10名若干iPad2+Xilins Spartan-6開發板Xilins Spartan-6開發板電子發燒友T恤賽靈思官方期刊雜志`

2012-04-23 09:31:16

玩轉FPGA,賽靈思FPGA設計大賽活動細則,參賽必看

)二等獎:Xilinx Spartan-6開發板(5名)三等獎:電子發燒友T恤(10名)小獎品:賽靈思官方期刊雜志【活動時間及流程】4月23日—7月31日報名階段:4月23日至7月20日期間,參賽者報名

2012-04-24 14:40:58

請教一個SPARTAN-6的問題。

我用的FPGA是SPARTAN-6,將ADC的輸出引進FPGA中,在FPGA中通過chipscope可以看到ADC的數據。我的問題是:我將同一個程序燒兩次,在chipscope中看同一個數據,發現第一次和第二次的值不一樣。但是理論上是一樣的才正確,為什么會不一樣呢?

2014-12-08 19:42:01

請問SPARTAN-6的平臺電纜USB是否支持?

我已經設計了一個基于SPARTAN 6XC6SLX150-CSG484器件的定制FPGA板。我正在使用USB平臺電纜對設備進行編程。 JTAG連接是正確的,并使用spartan-6的JTAG配置指南

2019-08-08 09:40:56

請問Spartan-6 IO引腳允許的最大電流是多少?

嗨,大家好!當我查看Spartan-6數據表時,我看到了繪制電流的幾個定義。根據數據表終止,有ICICQ,ICCOQ和ICCAUXQ。有人知道每個symnbols是什么意思嗎?以及它們是否與主題相關

2019-07-02 07:50:01

請問spartan-6芯片運行arm軟核是否有Xilinx的許可?

我想在spartan-6芯片上運行arm軟核,是否有Xilinx的許可?以上來自于谷歌翻譯以下為原文I'd like to run arm soft core on a spartan-6 chip, is there a license from Xilinx for this?

2019-07-11 09:09:59

請問哪里可以找到顯示Spartan-6器件所需配置位數的表?

我正在尋找一個顯示Spartan-6器件所需配置位數的表,我找到了Spartan-3和Virtex但不是Spartan-6的表。有誰知道我在哪里可以找到這個?

2019-08-01 07:53:05

選擇賽靈思(Xilinx)FPGA 7系列芯片的N個理由

電子發燒友網訊:賽靈思FPGA 7系列芯片正以燎原之勢席卷整個行業。在本文,電子發燒友網小編將帶領大家一起走近Xilinx的FPGA 7系列芯片,從全新FPGA 7系列芯片的介紹、芯片優點、芯片

2012-09-06 16:24:35

采用FPGA實現DisplayPort詳細教程【賽靈思內部資料】

思公司高級產品營銷經理 Neal KendallQuantum Data市場營銷經理采用FPGA實現DisplayPort詳細教程【賽靈思內部資料】[hide][/hide]

2012-03-01 11:10:18

高價回收賽靈思系列IC

高價回收賽靈思系列IC長期回收賽靈思系列IC,高價求購賽靈思系列IC。深圳帝歐長期回收ic電子料,帝歐趙生***QQ1816233102/879821252郵箱dealic@163.com。帝歐回收

2021-04-06 18:07:50

:“玩轉FPGA 賽靈思(xilinx)FPGA設計大賽”獲獎獎品展示

Spartan-6開發板 三等獎獎品: 電子發燒友網T恤+賽靈思小禮品 那接下來我們就展示一下獎品陣容吧!先給大家看看我們的iPad 2吧。圖 一等獎獎品之iPad 2#p#賽靈思Spartan-6開發板

2012-09-06 14:33:50

用Spartan-6和Virtex-6設計——賽靈思培訓課程

此課程將教會你:1)描述Spartan-6 和Virtex-6 FPGA的6輸入LUT和CLB建設的所有功能;2)指定Spartan-6 和Virtex-6的CLB資源和可用的Slice配置;3)定義可用的RAM和DSP資源塊;4)正確設計I/O塊和S

2010-12-14 15:09:48 0

0

0

0賽靈思推出最新Virtex-6/Spartan-6 FPGA

賽靈思推出最新Virtex-6/Spartan-6 FPGA 連接開發套件

近日,賽靈思公司(Xilinx, Inc. )宣布推出最新Virtex-6 和 Spartan-6 FPGA連接開發套件,該套件將為客戶提供一個綜合的、易用的

2009-12-15 08:42:01 978

978

978

978Spartan-6 FPGA工業影像目標設計平臺(Xilin

Spartan-6 FPGA工業影像目標設計平臺(Xilinx推出)

Xilinx推出賽靈思Spartan-6 FPGA工業影像目標設計平臺,為低成本、低功耗的工業影像系

2010-03-23 11:35:43 809

809

809

809基于Spartan-6 FPGA的SP605開發板解決文案

Xilinx 公司的Spartan-6 FPGA是目標設計平臺,提供集成的軟件和硬件,有利于設計集中力量進行新產品創新. Spartan-6 FPGA包括LX 和LXT等13個系列, 邏輯單元從3,840 到147,443, 而功耗比以前的Spartan

2010-05-31 14:35:13 3640

3640

3640

3640

高清開箱圖賞析:揭秘賽靈思Spartan-6 LX9開發板

電子發燒友網訊:本內容介紹了安富利Spartan-6 LX9開發板的高清開箱圖,Spartan-6 LX9開發板是基于賽靈思Spartan-6 FPGA的一款開發板,低價位的Spartan-6 LX9 MicroBoard 對于那些專注于Microblaze嵌入

2012-09-06 14:23:32 9051

9051

9051

9051一文詳解Spartan-6系列IO Tile結構

對Spartan-6系列FPGA來說,一個IO Tile包括2個IOB、2個ILOGIC、2個OLOGIC、2個IODELAY。 圖 1Spartan-6系列IO Tile結構圖 圖 2Spartan-6 FPGA I/O Banks。

2018-07-14 06:50:00 7731

7731

7731

7731

安富利Spartan-6 LX9 Microboard開發教程

低價位的Spartan-6 LX9 MicroBoard對于那些專注于Microblaze嵌入式應用和Spartan-6器件的工程師來說是一個很好的解決方案。這個套件提供了幾個預建好的Microblaze嵌入式系統,客戶可以像使用其他標準微處理器一樣開始軟件開發工作。

2018-06-06 02:45:00 3209

3209

3209

3209Xilinx Spartan-6系列封裝概述和管腳分配

Spartan-6系列具有低成本、省空間的封裝形式,能使用戶引腳密度最大化。所有Spartan-6 LX器件之間的引腳分配是兼容的,所有Spartan-6 LXT器件之間的引腳分配是兼容的,但是Spartan-6 LX和Spartan-6 LXT器件之間的引腳分配是不兼容的。

2018-07-01 10:48:00 8824

8824

8824

8824

如何使用Xilinx Spartan-6的物流解決方案

該演示展示了Prodrive引導的vechile如何使用Xilinx Spartan-6為倉庫和生產提供靈活的物流解決方案,從而實現功能安全。

2018-11-27 06:23:00 2206

2206

2206

2206ISE 14.7 for Spartan-6 FPGA的使用

了解如何輕松地開始在Windows10上使用ISE 14.7 for Spartan-6 FPGA。

只需單擊幾下即可安裝并啟動。

2018-11-26 06:09:00 4386

4386

4386

4386Avnet Spartan-6 FPGA DSP開發套件的性能特點與應用介紹

Xilinx Spartan-6 FPGA DSP套件支持所有主流DSP設計輸入方法,加速有經驗用戶的開發,同時通過利用可重復使用的設計基礎設施(包括......)簡化新用戶對FPGA的采用。

2018-11-22 06:40:00 3490

3490

3490

3490Spartan-6 FPGA中的DCM功能介紹

了解如何描述Spartan-6 FPGA中的全局和I / O時鐘網絡,描述時鐘緩沖器及其與I / O資源的關系,描述Spartan-6 FPGA中的DCM功能。

2018-11-22 06:10:00 4862

4862

4862

4862spartan-6 FPGA DSP48A1芯片的詳細資料介紹

本用戶指南詳細介紹了Spartan?6 FPGA中DSP48A1芯片的功能。

本章提供了Spartan-6 FPGA(DSP48A1芯片)中數字信號處理(DSP)元件的技術細節。每個DSP

2019-02-15 14:42:38 31

31

31

31Spartan-6 FPGA的配置教程說明

Spartan-6 FPGA 利用CCL 支持布線線路與邏輯單元之間的可配置互聯功能。Spartan-6 FPGA 是易失性器件- 電源移除時,不能保留原有配置。為了配置Spartan-6

2020-01-10 15:28:51 25

25

25

25從Spartan-6到Spartan-7 FPGA的遷移過程

電子發燒友網站提供《從Spartan-6到Spartan-7 FPGA的遷移過程.pdf》資料免費下載

2023-09-14 15:15:36 4

4

4

4 電子發燒友App

電子發燒友App

評論