本實(shí)驗(yàn)練習(xí)使用的設(shè)計是實(shí)驗(yàn)1并對它進(jìn)行優(yōu)化。

步驟1:創(chuàng)建新項目

1.打開Vivado HLS 命令提示符

a.在windows系統(tǒng)中,采用Start>All Programs>Xilinx Design Tools>Vivado2014.2>Vivado HLS>Vivado HLS 2014.2 Command Prompt

b. 在linux系統(tǒng)下,打開新的shell

2.變更到lab3路徑:cdc:\Vivado_HLS_Tutorial\Introduction\lab3.

3.在命令提示符窗口中,鍵入:vivado_hls -f run_hls.tcl建立工程

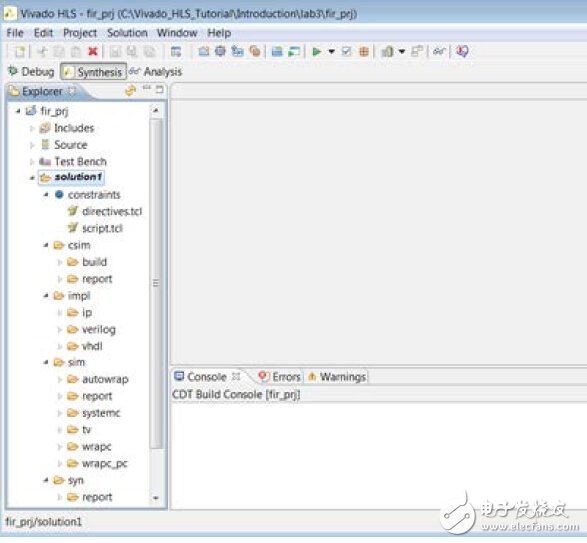

4.在命令提示符窗口中,鍵入:vivado_hls -p fir_prj在vivado用戶界面打開工程,Vivado HLS打開,如下圖所示。方案1的綜合已經(jīng)完成

如前面所述,本設(shè)計的目標(biāo)是:

?為這個設(shè)計創(chuàng)建一個的最高吞吐量的版本

?最終的設(shè)計應(yīng)該能夠處理一個伴隨輸入有效信號的輸入數(shù)據(jù)。

?伴隨著一個輸出有效信號的輸出數(shù)據(jù)。

?為了FIR設(shè)計,此濾波器系數(shù)存儲在外部的一個單端口的ram中。

步驟2:優(yōu)化I/O接口

因?yàn)樵O(shè)計規(guī)范中包含了I/O協(xié)議,所以首先你對創(chuàng)建正確的I/O協(xié)議和端口執(zhí)行優(yōu)化。I/O協(xié)議類型的選擇可能會影響設(shè)計優(yōu)化的可能性。如果有I / O協(xié)議的規(guī)定,應(yīng)在設(shè)計周期的早期設(shè)置I/O協(xié)議。

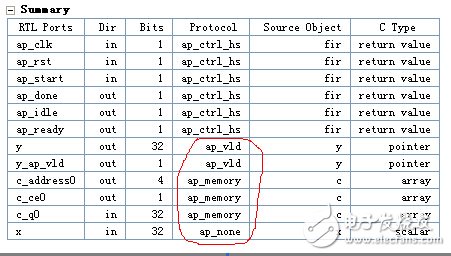

在lab1中,查看一下設(shè)計中的I/O協(xié)議,您可以通過導(dǎo)航找到在solution1\syn文件夾下的報告文件夾中綜合報告,可以重看一遍綜合報告,會發(fā)現(xiàn)I/O要求是:

?端口C必須有一個單端口的RAM訪問

?端口X必須有一個指示輸入數(shù)據(jù)是有效的信號

?端口Y必須有一個指示輸出數(shù)據(jù)是有效的信號

(重看了綜合報告,看見了Interface里面x,y,c等RTL 端口,但是這樣的具體要求不知道在什么地方體現(xiàn)出來,就是I/O協(xié)議方面的要求,應(yīng)該是下面紅色的圈起來的)

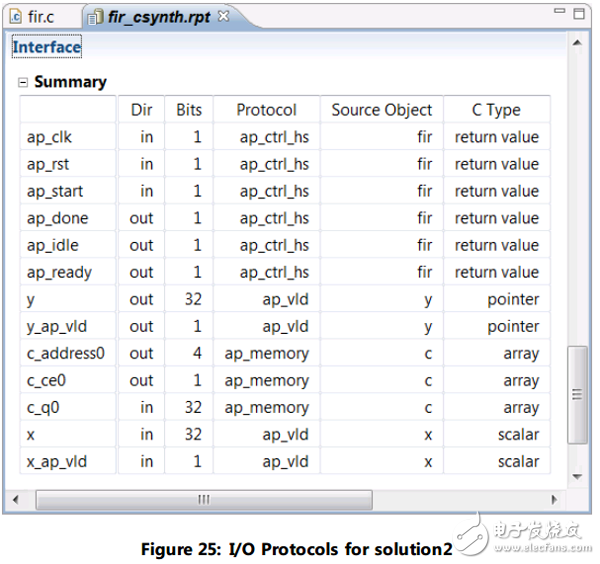

端口C已經(jīng)是一個單端口RAM的訪問。但是,如果你沒有明確指定的RAM訪問類型,高層次綜合可能會使用雙端口接口的RAM。HLS如果為了創(chuàng)建一個具有更高的吞吐量設(shè)計可以這樣做。如果要求是單端口的,你應(yīng)該明確地添加要求到設(shè)計的I / O協(xié)議中,要求使用單端口RAM。

輸入端口x在默認(rèn)情況下是一個簡單的32位數(shù)據(jù)口。您可以通過指定的I / O協(xié)議ap_vld實(shí)現(xiàn)它與相關(guān)的數(shù)據(jù)有效信號的輸入數(shù)據(jù)端口。

輸出Y口已經(jīng)有一個相關(guān)聯(lián)的輸出有效信號。這是默認(rèn)的指針參數(shù)。你沒有對這個端口指定明確的端口協(xié)議,因此就按照默認(rèn)要求去實(shí)現(xiàn),但如果要求了,那就按照要求去實(shí)現(xiàn)。

為了保存已經(jīng)存在的結(jié)果,創(chuàng)建一個新的解決方案,命名為solution2

1. 點(diǎn)擊New Solution工具欄按鈕,創(chuàng)建一個新的解決方案

2. 保存默認(rèn)的solution2名字,不要更改任何技術(shù)或時鐘設(shè)定

3. 點(diǎn)擊完成

創(chuàng)建solution2,并將其設(shè)置為默認(rèn)的解決方案 - 確認(rèn)solution2是在資源管理器窗格中突出顯示,表示它是當(dāng)前的解決方案。

要添加優(yōu)化指令來定義所需的I / O接口的解決方案,請執(zhí)行以下步驟。

4. 在資源管理器窗口中,打開Source包含項(見圖22)

5. 雙擊fir.c ,在信息窗口中打開文件

6. 激活輔助窗格中的指令選項卡(Directives tab),選擇頂層函數(shù)中fir跳轉(zhuǎn)到源代碼視圖中fir函數(shù)的頂部(圖22)。

指令選項卡在圖22右邊展示,列出了在設(shè)計中的所有可以被優(yōu)化的對象。在指令選項卡中,你可以為設(shè)計添加優(yōu)化指令。只有當(dāng)源代碼是在信息窗格中打開時您才可以查看指令選項卡。

7. 在指令選項卡中,選擇C的參數(shù)/端口(綠點(diǎn))。

8. 右擊并選擇插入指令(Insert Directives)

9. 實(shí)現(xiàn)單端口ram接口須按以下操作

a. 從該指令的下拉菜單中選擇源(RESOURCE)(為什么要選擇RESOURCE,這個下拉框中其他選項有什么意義,在什么情況下用,有待研究)

b. 點(diǎn)擊core框

c. 選擇RAM_1P_BRAM, 如圖23所示(這個下拉菜單中也有很多選項,每個選項在什么情況下用有待研究,不知道從什么地方可以找到相關(guān)資料)

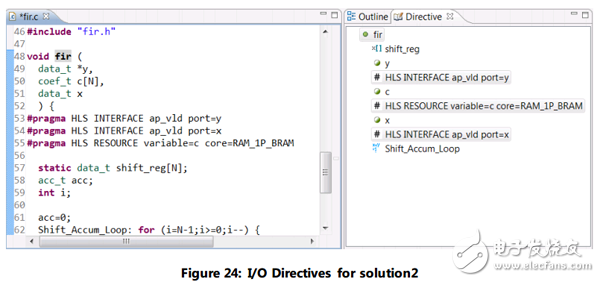

上述步驟指定數(shù)組c是使用單端口塊RAM資源來實(shí)現(xiàn)。由于數(shù)組c是函數(shù)的參數(shù)列表,因此是函數(shù)之外。自動創(chuàng)建一組數(shù)據(jù)端口來訪問單端口RAM塊的RTL實(shí)現(xiàn)之外。

由于I / O協(xié)議是不可能改變的,你可以將這些指令優(yōu)化添加到源代碼里,作為編譯指示,以確保正確的I/ O協(xié)議嵌入到設(shè)計中。

10. 在指令編輯器(Directive Editor)中的Destination中選擇源文件(source file)。

11. 要應(yīng)用指令,單擊OK。

提示:如果你想改變?nèi)魏沃噶畹哪康模驮谥噶钸x項卡中的指令雙擊并修改目標(biāo)。

12. 接下來,指定端口X要有相關(guān)的有效信號/端口

a. 在指令選項卡中,選擇輸入端口x(綠色點(diǎn))

b. 右擊,并選擇Insert Directives

c. 從指令編譯下拉菜單中選擇接口(Interface )

d. 從對話框的Destination中選擇Source File

e. 在mode中選擇ap_vld模式

f. 單擊OK應(yīng)用指令

13. 最后,明確指定端口Y,有一個相關(guān)聯(lián)的有效信號/端口。

a. 在指令(Directive)選項卡中,選擇輸入端口y(綠色點(diǎn))

b. 右擊,并選擇Insert Directives

c. 從指令編譯下拉菜單中選擇接口(Interface )

d. 從對話框的Destination中選擇Source File

e. 選擇ap_vld的模式

f. 單擊確定應(yīng)用指令

完成后,驗(yàn)證源代碼和指令選項卡,如圖24所示。對任何不正確的指令,用鼠標(biāo)右鍵單擊要修改它。

14. 點(diǎn)擊Run C Synthesis 工具欄按鈕,并綜合設(shè)計

15. 出現(xiàn)提示時,單擊Yes保存在C源文件中的內(nèi)容。添加指令作為編譯指示修改源代碼。

當(dāng)綜合完成后,報告文件會自動打開。

16. 單擊多級選項卡,查看接口的結(jié)果,或者干脆向下滾動到報告文件的底部。

圖25展示了擁有正確I/O協(xié)議的端口

步驟3:分析結(jié)果

在優(yōu)化設(shè)計前,最重要的是理解當(dāng)前的設(shè)計,結(jié)果顯示:在實(shí)驗(yàn)1中如何使用綜合報告來理解實(shí)現(xiàn)功能,然而,分析視窗提供一個互動式的方式更加詳細(xì)。

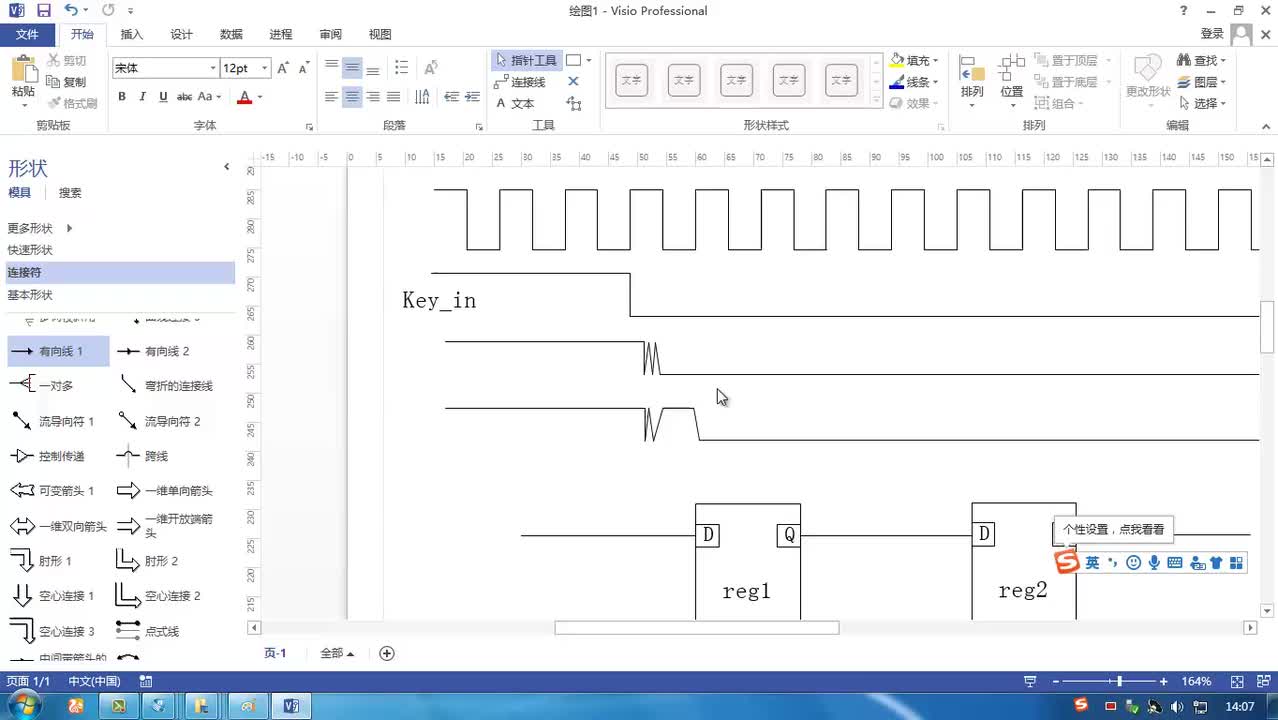

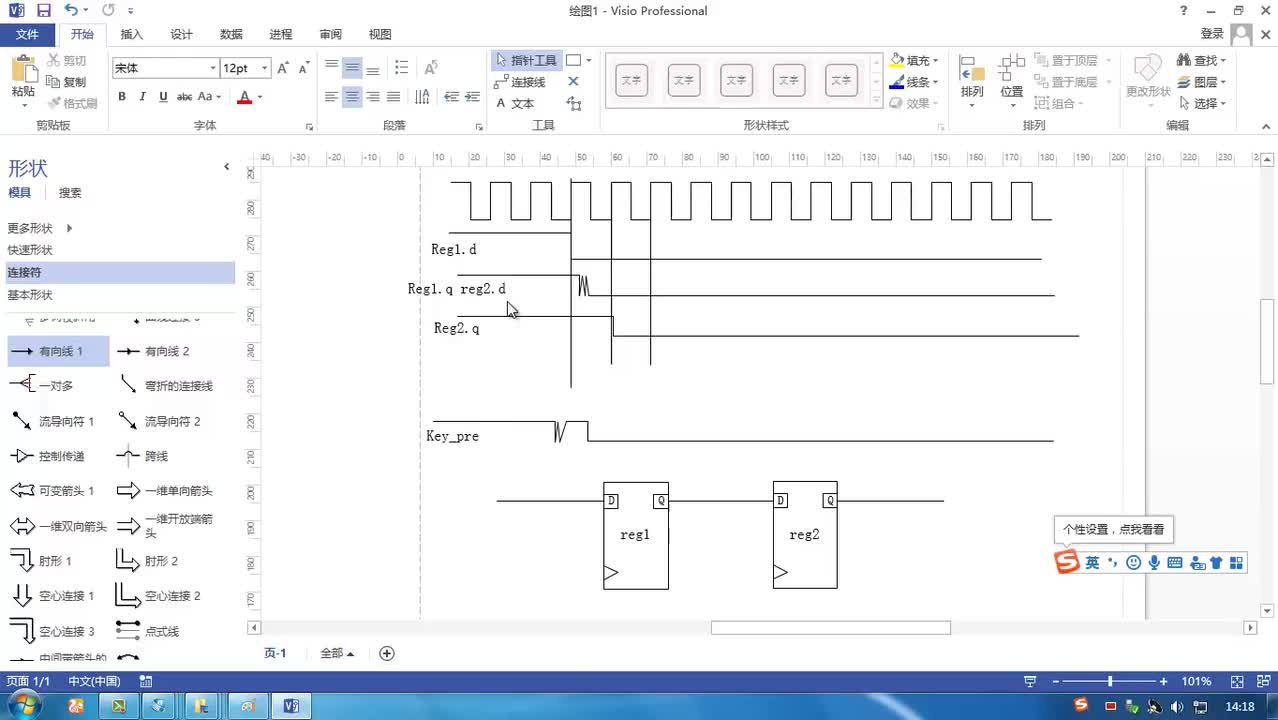

任然以solution2為例,在圖26所示

1. 點(diǎn)擊分析按鈕(Analysis perspective button)

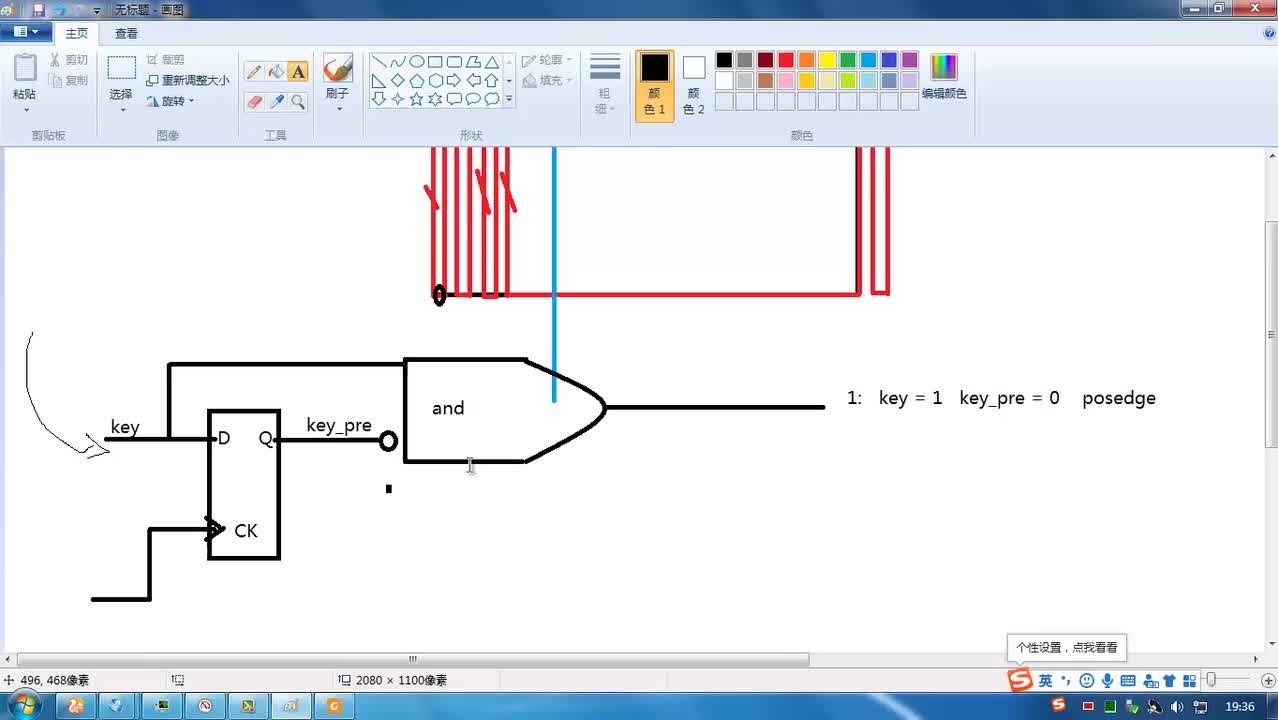

2. 點(diǎn)擊Shift_Accum_Loop在性能(Performance)窗口中進(jìn)行打開

?在圖26中紅色虛線的使用說明;它不是視圖的一部分

?本教程的設(shè)計分析(Design Analysis)提供了更全面的對分析觀點(diǎn)理解,但下面解釋了什么要求可以從源代碼中創(chuàng)建面積最小,速度最快的RTL設(shè)計。

?性能窗格視圖左欄顯示的RTL層級在此模塊中的操作。

?最上面一行列出了設(shè)計中的控制狀態(tài)。控制狀態(tài)是指高層次綜合的內(nèi)部狀態(tài)使用的計劃表操作成時鐘周期。RTL有限狀態(tài)機(jī)(FSM)的控制狀態(tài)和最終狀態(tài)之間有密切的關(guān)系,但并不是一對一的映射。

這里給出的解釋如下紅色虛線在圖26的路徑,某些對象的位置直接相關(guān)的C源代碼。用鼠標(biāo)右鍵單擊該對象交叉引用的C代碼。

?設(shè)計開始時,在第一狀態(tài)下讀取端口x

?在下一狀態(tài)中,開始執(zhí)行由for循環(huán)Shift_Accum_Loop創(chuàng)建的邏輯。循環(huán)顯示為黃色,你可以展開或折疊它們。握住鼠標(biāo)移到該視圖中的黃體循環(huán)顯示循環(huán)細(xì)節(jié):8個周期,11次迭代,總的延遲為88周期。

?在第一狀態(tài)中,循環(huán)迭代計數(shù)檢查:添加,比較,和退出潛在的循環(huán)。

?在操作由數(shù)組綜合成的塊RAM時,讀取內(nèi)存要花費(fèi)兩個周期。(一個周期產(chǎn)生地址,一個周期讀取數(shù)據(jù))

?把從C端口讀取的數(shù)據(jù)放到memory里

?乘法運(yùn)算需要3個周期來完成。

?一個for循環(huán)需要執(zhí)行11次

?在最后一次迭代結(jié)束時,在狀態(tài)C1退出循環(huán)并向端口Y寫入數(shù)據(jù)。您還可以使用分析器來分析在設(shè)計中使用的資源。

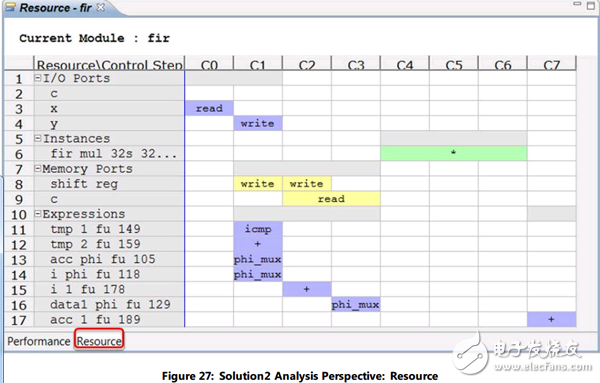

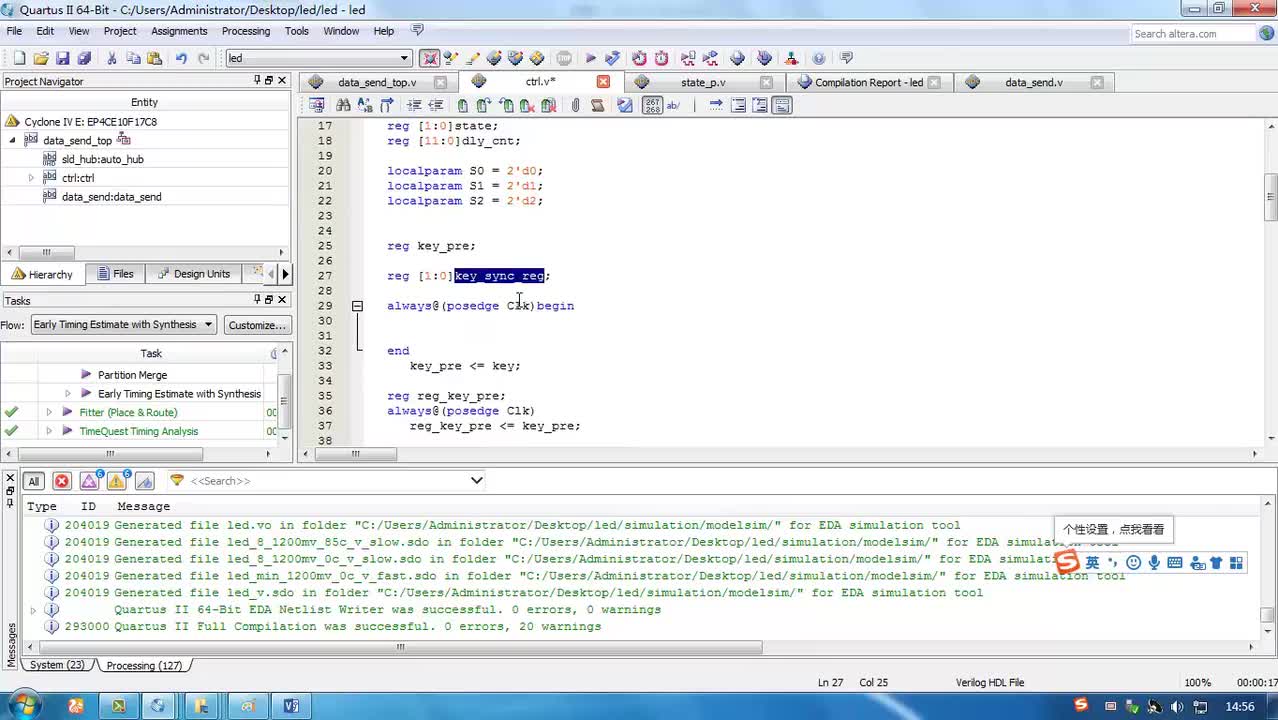

3. 點(diǎn)擊Resource,如圖27

4. 打開所有的資源組如圖27

圖27展示了:

?x和y是I/O端口。在報告中可以看出端口c在memory部分,因?yàn)閏是內(nèi)存接口。

?在設(shè)計中用到了兩個乘法器

?在memory shift_reg中進(jìn)行了讀寫操作

?沒有其它資源被共享,因?yàn)樵诿啃谢蛎總€時鐘周期內(nèi)每次僅操作一個實(shí)例。

有敏銳的洞察力,通過分析得到,可以繼續(xù)進(jìn)行優(yōu)化設(shè)計。

?在結(jié)束之前的分析,這是值得評論的多周期乘法運(yùn)算,這需要多個DSP48s實(shí)現(xiàn)。源代碼使用int數(shù)據(jù)類型。這是一個32位的數(shù)據(jù)類型,它導(dǎo)致大的乘法器。一個DSP48乘數(shù)是18位的,它需要多個DSP48s乘法器來實(shí)現(xiàn)數(shù)據(jù)寬度大于18位的乘法。

本教程任意精度類型顯示了如何創(chuàng)建一個硬件更合適的數(shù)據(jù)類型的設(shè)計。使用任意精度的類型,可以定義任意位大小的數(shù)據(jù)類型。(超過標(biāo)準(zhǔn)的C / C+ +8位,16位,32位或64位的數(shù)據(jù)類型)。

步驟4:優(yōu)化最高吞吐量(最低間隔)

在本設(shè)計中有兩個問題限制了吞吐量,主要有:

?for循環(huán)。默認(rèn)情況下,循環(huán)保持rolled:循環(huán)體的一個副本被綜合和用于每次迭代中。這確保了在循環(huán)的每次迭代中被順序地執(zhí)行。你可以展開for循環(huán),讓所有操作并行發(fā)生。

?塊RAM用于shift_reg。因?yàn)樽兞縮hift_reg在C源代碼中是數(shù)組,綜合實(shí)現(xiàn)的是為一個默認(rèn)的RAM塊。然而,這可以防止其實(shí)現(xiàn)為移位寄存器。因此,您應(yīng)分區(qū)此塊內(nèi)存到單個寄存器。

開始創(chuàng)建一個新的解決方案

1. 點(diǎn)擊New Solution按鈕

2. 保存解決方案的名稱為solution3

3. 點(diǎn)擊Finish來創(chuàng)建新的解決方案

4. 在工程菜單(project)中,選擇Close Inactive Solution Tabs 來關(guān)閉先前解決方案中的打開的標(biāo)簽頁。

以下步驟,圖28中概述解釋了展開循環(huán)體

5. 在指令選項卡中選擇循環(huán)Shift_Accum_Loop.(提醒:源代碼必須在信息窗格中打開,就會看到在指令標(biāo)簽的所有代碼對象)

6. 右擊并選擇Insert Directives

7. 在指令下拉菜單中選擇Unroll, 保留目標(biāo)作為優(yōu)化文件。

當(dāng)優(yōu)化設(shè)計時,必須經(jīng)常進(jìn)行多次迭代的優(yōu)化,確定最終應(yīng)該優(yōu)化的。通過添加優(yōu)化指令文件,可以保證它們不會自動結(jié)轉(zhuǎn)到下一個解決方案。

存儲解決方案中指令文件的優(yōu)化,讓不同的解決方案有不同的優(yōu)化。已添加的優(yōu)化代碼中的編譯指示,他們會自動結(jié)轉(zhuǎn)到新的解決方案,你將不得不修改代碼回去,然后重新運(yùn)行以前的解決方案。

保留其他選項的指令窗口選中空白,以確保循環(huán)完全展開。

8. 點(diǎn)擊OK應(yīng)用指令

9. 應(yīng)用指令把數(shù)組分割成單個元素

a. 在在指令選項卡中,選擇數(shù)組shift_reg

b. 右擊,并選擇Insert Directives

c. 從指令下拉菜單中選擇Array_Partition

d. 在type(optional)中選擇complete

e. 點(diǎn)擊OK應(yīng)用指令

嵌入在solution2代碼中的指令和增加的兩個新指令,solution3的指令窗格出現(xiàn)如圖29所示。

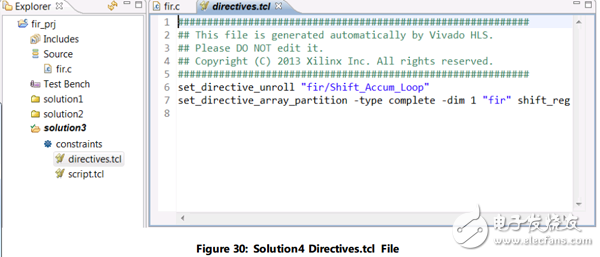

在圖29中,注意,在solution2里應(yīng)用的指令對編譯的指示相比較那些剛剛應(yīng)用并保存到指令文件的指令有不同的注解。您可以在Tcl文件中查看新增加的指令。

10. 在資源管理窗口,展開Solution3中的Constraint文件夾,如圖30

11. 雙擊solution3directives.tcl文件,并在信息窗口中打開

12. 點(diǎn)擊Synthesis工具欄按鈕,綜合設(shè)計。當(dāng)綜合完成,綜合報告自動打開

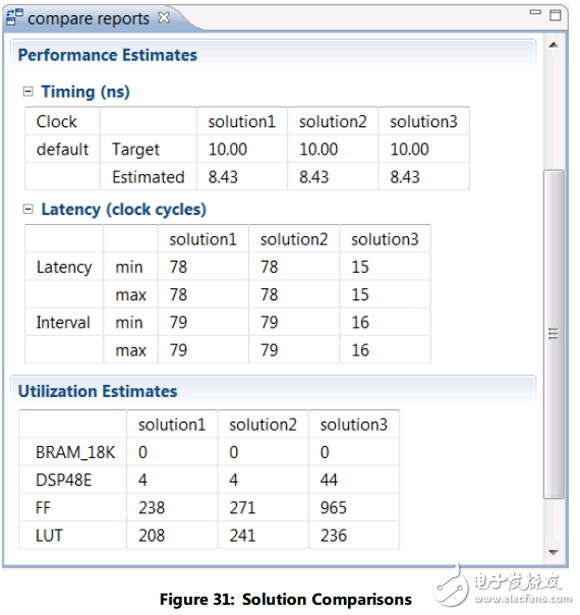

13. 比較不同方案的結(jié)果

14. 點(diǎn)擊Compare Reports工具欄按鈕。或者用Project>Compare Reports

15. 添加solution1、solution2、solution3進(jìn)行比較

16. 點(diǎn)擊OK

圖31示出的報告進(jìn)行比較。solution3具有最小的啟動間隔和可以更快處理數(shù)據(jù)。作為間隔僅為16,它開始處理一個新的輸入集需要16個時鐘周期。

能夠在此設(shè)計執(zhí)行額外的優(yōu)化。例如,您可以使用流水線操作,以進(jìn)一步提高吞吐量和降低的時間間隔。本教程的設(shè)計優(yōu)化提供了有關(guān)使用流水線來提高間隔的細(xì)節(jié)。

正如前面提到的,你可以修改代碼本身使用任意精度的類型。例如,如果數(shù)據(jù)類型是不要求為32位int類型,可以使用位精確類型(例如,6位,14位或22位的類型),只要它們滿足所要求的精度。有關(guān)使用任意精度類型的更多詳細(xì)信息,請參閱教程任意精度類型。

結(jié)論

在本教程中,您學(xué)習(xí)了如何:

?創(chuàng)建的GUI和Tcl的環(huán)境中Vivado高層次綜合項目。

?執(zhí)行中的HLS設(shè)計流程的主要步驟。

?創(chuàng)建和使用一個Tcl文件運(yùn)行VivadoHLS。

?創(chuàng)建新的解決方案,加上優(yōu)化的指令,并比較不同解決方案的結(jié)果。

電子發(fā)燒友App

電子發(fā)燒友App

評論