做了三年四個(gè)項(xiàng)目最近才第一次需要深入的搞一下FPGA 燒寫。在這里簡(jiǎn)單總結(jié)一下FPGA燒寫的具體過(guò)程和玩的花樣

大家常用的辦法

對(duì)于大部分人來(lái)說(shuō),至少入門時(shí)會(huì)用到的燒寫方式就兩種:

① 通過(guò)JTAG直接將bitsteam 燒錄到FPGA。 斷電后信息丟失。這種方式多用于發(fā)開(kāi)調(diào)試階段,板子一直連著電腦。通過(guò)ISE 或者 Vivado (2020年開(kāi)始估計(jì)還有Vitis)使用JTAG接口燒錄。

② 在設(shè)計(jì)release以后,到產(chǎn)品上一般都是把配置文件通過(guò)IDE工具保存存在Nor Flash里。上電后自動(dòng)編程FPGA。

較為進(jìn)階的一種方法

通常情況下這兩種方式也就可以滿足大部分需求了。開(kāi)發(fā)調(diào)試直接JTAG。產(chǎn)品出貨前,配置文件通過(guò)JTAG接口,用VIVADO或者SDK等工具燒進(jìn)Flash。之后把接口封起來(lái)。產(chǎn)品需要更新的時(shí)候,派技術(shù)支持去,重新打開(kāi)接口,插上JTAG,把新的配置文件燒入Flash。

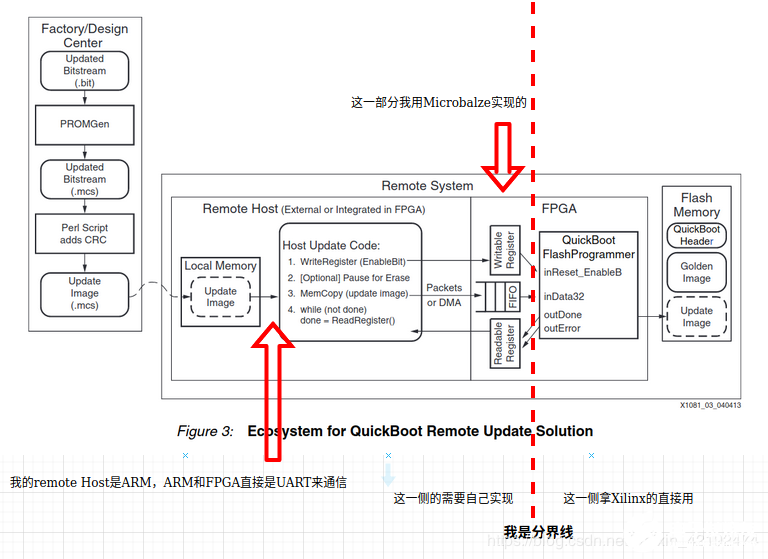

但是這次項(xiàng)目是個(gè)小型手持測(cè)量設(shè)備,JTAG接口只有在設(shè)備拆散狀態(tài)下通過(guò)擴(kuò)展板才能使用。組裝好后FPGA只能通過(guò)Flash來(lái)編程。由于是個(gè)精密儀器,每次拆開(kāi)再組裝,整個(gè)設(shè)備都需要重新校準(zhǔn),非常費(fèi)事費(fèi)力。組裝后更新Flash里面的配置文件只能用別的辦法了。這種情況下常用的方法是通過(guò)一個(gè)和外界有通信能力的微控制器將image發(fā)送給FPGA, 再由FPGA寫入Flash。

這種remote update Xilinx提供了一種解決方案,相對(duì)應(yīng)的Application Note 是 :

QuickBoot Method for FPGA DesignRemote Update (文檔號(hào)碼XAPP1081)

采用這種方案的前提是理解FPGA通過(guò)Flash配置的細(xì)節(jié),所以以7系FPGA為例先需要看一下這個(gè)文檔:

7 Series FPGAsConfiguration (UG470) 主要是看第五章:Chapter 5 Configuration Details

Xilinx 遠(yuǎn)程燒錄FPGA方法

遠(yuǎn)程燒錄一般是為了設(shè)備出廠以后還需對(duì)FPGA進(jìn)行更新或者升級(jí)。為了避免在燒錄過(guò)程中新的配置文件損壞,導(dǎo)致FPGA不能正常啟動(dòng)。通常采取的是雙保險(xiǎn)策略,有個(gè)gold bitstream,是出廠是寫入Flash的,是測(cè)試過(guò)絕對(duì)可以啟動(dòng)FPGA的,還有一個(gè)是update bistream,出廠時(shí)就是一個(gè)gold bitstream的copy,F(xiàn)PGA每次啟動(dòng)都是默認(rèn)寫讀取這個(gè)update bitstream。之后的更新也就是去重寫這個(gè) update bitstream, 一旦在更新過(guò)程出了問(wèn)題,比如突然斷電。update bistream損害或者殘缺,F(xiàn)PGA在嘗試從update bitstream啟動(dòng)失敗后就會(huì)去讀取gold bitstream。這種方法保證了一個(gè)相對(duì)安全的update方法,所以也是一種非常經(jīng)典的方法。

去掉廢話來(lái)概括這種方法

每一個(gè)bitstream都長(zhǎng)這樣:

FPGA會(huì)先去找synchro word (7系列的spi接口的話就是0xAA995566)找到以后讀取首地址,然后跳到首地址,開(kāi)始讀取所有的配置數(shù)據(jù)。

此文介紹的這種雙保險(xiǎn)策略就是在Flash中存入兩個(gè)bitstream。但是精髓所在是這兩個(gè)Bitstream在內(nèi)存中怎么放。

如下圖所示,update的bitstream會(huì)被拆成兩段,synchron word和首地址會(huì)被存在goldbitstream前面,然后其他部分存在goldstream之后。而且update bitsteam尾部還會(huì)人為加入一個(gè)CRC。

這種鬼畜結(jié)構(gòu)的目的

這種結(jié)構(gòu)可以提供一種非常安全可靠的update模式。為什么會(huì)安全可靠。先來(lái)說(shuō)一下這種結(jié)構(gòu)下的update流程:

當(dāng)我們想要update bistream的時(shí)候:

① 首先 update synchro word和首地址所在的sector(Flash里可以擦除的最小單元)會(huì)被擦除。

② 然后開(kāi)始在update所在的地方擦除所有內(nèi)容,寫入新的bitstream。包括CRC。(這個(gè)CRC是生成bitstream的時(shí)候加入的。具體操作看下一章)。

③ 當(dāng)寫入結(jié)束后整個(gè)新寫入的內(nèi)容會(huì)被讀出來(lái)計(jì)算CRC,然后和嵌入的CRC來(lái)做比較。當(dāng)CRC一致時(shí),說(shuō)明在傳輸和寫入過(guò)程沒(méi)有出現(xiàn)問(wèn)題。新寫入的配置內(nèi)容完整,有效。這時(shí)update的synchro word和首地址才會(huì)寫入最開(kāi)始被擦除sector。

這樣一來(lái),如果CRC不一致,說(shuō)明這是個(gè)bad update,新寫入的配置內(nèi)容不可用。那么被擦除的synchro word 和首地址不會(huì)被寫入。第一個(gè)sector是空的。當(dāng)FPGA上電后,它是在這個(gè)sector里找不的update image的同步字和首地址的,繼續(xù)讀下去會(huì)讀到屬于goldbitstream的同步字和首地址。

如下圖所示:

實(shí)際操作步驟和文檔中的坑

首先好消息是,上述的這些Flash擦除,寫入,各種地址,sector,page等等Xilinx已經(jīng)寫好了VHDL的模塊。可以直接拿來(lái)用。自己需要實(shí)現(xiàn)的是remote端往FPGA的數(shù)據(jù)傳輸。具體如下圖:

具體實(shí)現(xiàn)步驟如下:

① 實(shí)現(xiàn)remote端的update程序,該程序需要讀取update image 然后通過(guò)某種接口和通信協(xié)議將image發(fā)送給FPGA。這一步該需求和情況自由發(fā)揮。例如物聯(lián)網(wǎng)的可以用藍(lán)牙或者WIFI。

② 實(shí)現(xiàn)FPGA端的數(shù)據(jù)接收。該模塊將數(shù)據(jù)寫入Xilinx提供的FlashProgrammer

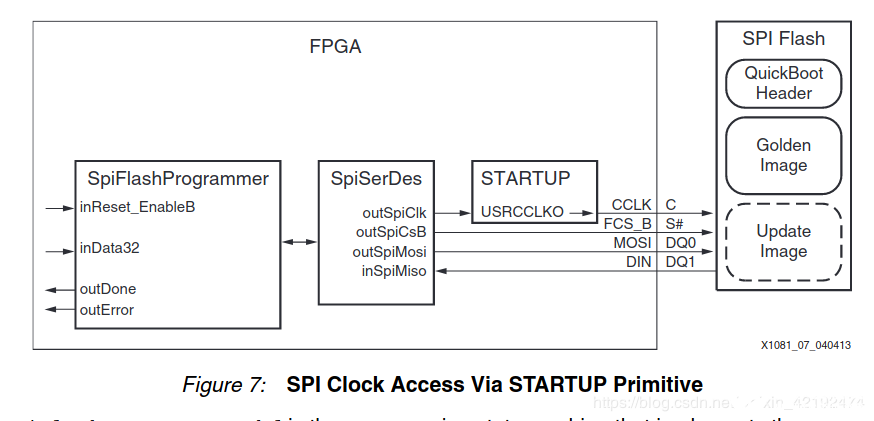

③ 下載XAPP1081文檔中的例子 KC705 Board Demonstrations, page 33。例子中兩個(gè)VHDL模塊按下圖實(shí)例化。注意 這兩個(gè)模塊必須共用一個(gè)時(shí)鐘,而且這個(gè)時(shí)鐘就是SPI的時(shí)鐘,所以注意不要太快。一般20Mhz一下。

④ 集成前三條實(shí)現(xiàn)的模塊,調(diào)試。可以實(shí)現(xiàn)將數(shù)據(jù)從remote端發(fā)送給FPGA,經(jīng)過(guò)SPiFlashProgrammer寫入Flash。

⑤ 把bitstream格式轉(zhuǎn)換成mcs格式。將gold bistream。bit格式轉(zhuǎn)換成mcs格式。VIVADO下使用tcl 命令write_cgfmen -format mcs -interface spix1。一定要加 -interface spix1,不然所有的bits都會(huì)被swap!

⑥ 通過(guò)Xilinx例子中提供的Perl Script生成 gold init image。script的輸入就是剛才轉(zhuǎn)換的mcs格式的goldbitstream.mcs。輸出之一是gold init image這個(gè)image就是圖4中描述的那種鬼畜布局的雙bitstream,只不過(guò)兩個(gè)bitstream是一樣的。update bitstream是gold的copy。

⑦ 將gold inital.mcs通過(guò)VIVADO 或者PROMgen用JTAG直接燒入Flash

⑧ 同樣的方式用Perl Script生成 update image。 輸入是xxx.mcs。輸出之一是xxx_update.mcs。這個(gè)就是上文所屬的加了CRC的update image。生成過(guò)程中perl script會(huì)給出Flash的首地址和結(jié)束地址。將SpiFlashProgrammer中的首尾地址改成這兩個(gè)地址。注意:因?yàn)槭孜驳刂肥菍懺赩HDL里的,也就是說(shuō)Image的大小是固定的。為了防止在未來(lái),update image變大。可以預(yù)留一部分出來(lái)。例如:目前的大小是3.3MB。我們預(yù)留0.7MB給未來(lái)可能出現(xiàn)的更新。那么我們需要生成的image需要4MB大。這是要給perl script一個(gè)附加的agrument: -imagesize 32

⑨ 將xxx_update.mcs轉(zhuǎn)換成.hex文件。網(wǎng)上有不少工具可以。實(shí)在不行谷歌一下mcs格式,自己寫個(gè)script轉(zhuǎn)換一下。

⑩ FPGA上電,取消SpiFlashProgrammer的reset。 remote的軟件讀取xxx_update.hex,傳輸給FPGA,經(jīng)由SpiFlashProgrammer寫入Flash。

? 寫入后,查看Programmer的Status. Done輸出1,所有Error Port輸出是0的話,說(shuō)明update成功!

? FPGA重新上電,檢查FPGA內(nèi)是否是由新的image配置的

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論