編碼不能沒調試,調試不能沒斷點。斷點是仿真器非常重要的功能,用戶在仿真程序過程中幾乎離不開斷點。

2015-10-10 09:30:22 865

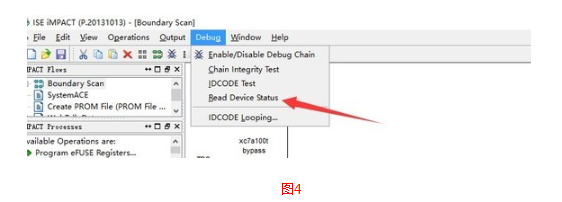

865 你好我最近在2013.4使用Artix7看到了以下錯誤。錯誤:[通用17-69]命令失敗:您的設備許可證'xc7a100t'僅用于評估或試用目的。此許可證禁用比特流創建。請運行Xilinx許可證

2020-07-22 13:08:31

設計的板子是6748+FPGA,兩者通過EMIFA和RESET引腳相連,6748啟動之后,FPGA可以讓其復位。現在問題是6748啟動的時候,電流會達到很到1.5A,此時6748能正常運行,但是發燙

2019-08-14 13:17:13

嗨,我們計劃在我們的設計中使用Artix-7A50T器件,支持1Gb DDR SDRAM內存。你能澄清下面的問題:1.它需要任何內存控制器嗎?2.如果是這樣,軟IP需要購買或免費?3.請告訴我們邏輯資源利用情況等...謝謝Pench

2020-04-03 09:55:20

Avnet 設計的 Artix-7 50T FPGA評估套件是完全可定制的開發工具套件,非常適合嵌入式設計人員對靈活低功耗平臺的需求。Artix–7 50T FPGA評估板是一套完整的系統,它把嵌入式處理器系統所需的所有功能和接口都集成到一個小小的芯片上。相關資料打包下載

2016-08-19 15:32:34

我正面臨著Artix-7的問題。我們的設計采用帶有CMOS(LVCMOS25)輸出的ADC,通過CMOS緩沖器與Artix-7 XC7A200T(FFG1156)連接。我們的ADC為16位,130

2020-04-07 12:26:15

我找不到任何新的Artix7 FPGA的包信息文件(Pinout)目前,帶有4個GTP的XC7A25T CPG236是我更感興趣的設備。但是,XC7A12T設備也沒有包文件。謝謝。

2020-08-14 09:34:14

嗨,我可以在某處找到Artix7 GTP收發器功耗的信息嗎?我知道MGTAVVT和MGTAVCC必須來自單獨的LDO,但每個LDO需要多少電流?我們計劃使用XC7A200T-2FBG484I,我們只

2019-03-12 12:30:08

我們的設計使用Artix7 -2L器件。它從ADC捕獲圖像數據,最后是顯示圖像的應用程序。主時鐘為80MHz,使用PLL生成20,40,80和160Mhz。時序正在使用實現策略(最壞的情況是設置

2020-07-29 10:33:36

大家好,我想使用Artix-7部件(xc7a15tftg256pkg),其引腳命名不正確。https://www.xilinx.com/support/packagefiles/a7

2020-05-12 06:02:45

我目前正致力于在artix 7 FPGA上調出極光8B10B接口。即使我在并行環回模式下操作,我也看到了通道綁定問題。 FPGA是artix 7,fbg676封裝速度等級2器件。我

2020-08-12 08:10:59

大家好,任何人都可以指向一個文檔,我可以看到哪些連接對FPGA上的哪些組件有效?我正在使用Artix 7設備xc7a200t fbg676-2。謝謝,Richa以上來自于谷歌翻譯以下為原文Hi

2018-10-30 11:14:52

Artix 7板上編程SPI Flash(N25Q256 3.3v)時,盡管閃存編程成功,但在Artix 7板上電時,FPGA無法從閃存啟動。我必須按下FPGA_PROG_B按鈕&只有

2020-08-12 09:31:34

我正在使用Artix-7(xc7a15tftg256-1)作為Vivado 2014.1的軟件包。 DONE引腳狀態有問題。編程后DONE引腳應為高電平(3.3V),但我只有680mV。如果我切換I / O引腳,I / O引腳將無法工作。那么,任何人都可以糾正這個問題嗎?

2020-04-08 09:45:56

板子啟動出現這樣的問題,去網上查了下,說重新配置busybox ,然后make, make install 再啟動這個問題就沒了。但是出現了這個不能啟動UBOOT參數

2019-05-23 00:39:52

嗨,我只是想確定......ISE 11.7許可證(完整版,不是webpack)是否支持較小的ARTIX7設備(-25,-35,-50,-75)謝謝你告訴我這件事...以上來自于谷歌翻譯以下為原文

2018-12-25 11:09:18

Spartan 6非常適合我的另一個項目,但是我看到一些團隊成員向Artix 7轉移。由于我們在工業設備上使用FPGA,因此Artix 7上的上/下排序要求和I / O電壓引起了我的關注。此外,我應該花更多

2019-05-06 06:13:35

我試圖將virtex 6中的設計遷移到artix 7 ...在virtex 6中,我曾經在45分鐘內完成設計運行,沒有定時錯誤......但是在artix 7中需要3小時的定時誤差......(在

2019-04-25 07:51:10

深覺若是再花一點氣力,將這些文稿再做一些深加工,確實也可以給很多FPGA初學者一些具體實在的幫助。同時,筆者結合自身的學習經歷,為廣大學習者量身打造了基于目前主流的、高性價比的Xilinx Artix7

2019-03-02 19:37:42

`Xilinx Artix-7 FPGA快速入門、技巧與實例連載8——FPGA進階之路更多資料共享鏈接:https://share.weiyun.com/53UnQasFPGA工程師的成長需要經歷

2019-04-10 15:18:08

Xilinx Artix-7 FPGA快速入門、技巧與實例連載7——FPGA開發技能更多資料共享鏈接:https://share.weiyun.com/53UnQas在FPGA技術的應用領域不斷擴展

2019-04-10 14:58:20

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

The Artix-7 is part of the 7-Sseries of FPGA's from Xilinx. Containing 1,156 pins, creating

2014-02-13 09:24:15

,在此基礎上設計過基于FPGA的電子琴。同時此前在電子發燒友成功申請獲得過云路由和樹莓派的試用,認真對待每次試用機會,認真撰寫心得體會。如果獲得Artix-7 FPGA的試用機會,試用進度如下:1、認真閱讀

2016-11-10 12:34:54

工程時,在器件板卡選型時,可以選擇Boards面板,選擇Artix-7 50T Evaluation Board板卡。無需知道FPGA芯片詳細信息。5、在Block Design設計時,可以直接拖動板卡資源到設計面板中。這就是簡單的LED實例化過程,在嵌入式設計時,相當方便用戶使用。

2016-11-28 15:15:16

[size=22.0000pt]掌握新的一門技術,都先從這是什么開始。Artix-7 50T是什么?首先它在硬件分類上屬于FPGA,是一款xilinx公司推出的FPGA芯片。低功耗和低成本,我們拿到

2016-11-23 22:36:52

。Xilinx在7系列中引進了所有類型的FPGA,包括低端的Artix-7完全可編程FPGA系列、中端的Kintex-7 完全可編程 FPGA系列以及高端的Virtex-7完全可編程系列。 7系列的所有設備均統一

2016-12-21 10:56:25

醫療設備、軍用無線電和小型無線基礎設施等產品提供同類最佳的單位功耗性能。 Artix-7 FPGA 可滿足航空電子和通信等領域的尺寸、重量、功耗和成本 (SWaP-C) 敏感型市場需求。從介紹中可知

2016-11-01 15:52:18

收到一個白色紙箱,作為剁手party,拆快遞箱那快感不用多說了,打開紙箱,一塊板子,幾張說明書,還有數據線等配件 相比其它搭載高端FPGA芯片的開發板,Artix-7 50T開發板算是比較迷你的,當然

2016-11-01 14:40:21

此篇先細致探索一下板卡的硬件資源。 如下圖所示,主要以Artix-7 50T FPGA為核心,外圍有電源管理和時鐘電路,通信、輸入輸出端口,和存儲器。電源管理: 板卡電源輸入有兩種方式1) 由DC

2016-12-12 22:12:39

LwIP以太網調試 第二步,對DDR3 SDRAM進行了研究,對其在xilinx FPGA中的接口做了調試,而且做了上板測試:【Artix-7 50T FPGA試用體驗】DDR3調試 此篇結項報告,融合

2016-12-19 08:12:39

有效;TXD[1:0],輸出數據l參考時鐘:REF_CLK,50MHz,由FPGA輸出給PHY二、環境搭建:開始調試RMII接口,在Vivado中建立工程,編寫代碼,系統結構如下所示,PHY1接收數據

2016-12-13 20:07:58

FPGA bit文件 運行lwip_raw程序,打開串口調試助手,可看到系統啟動信息 根據提示信息,可以開始測試lwIP了Echo server: 在命令行窗口,輸入telnet 192.168.2.10

2016-12-14 15:56:23

【Artix-7 50T FPGA試用體驗】基于7A50T FPGA開發套件的工業通信管理機設計(一)【Artix-7 50T FPGA試用體驗】基于7A50T FPGA開發套件的工業通信管理機設

2016-12-27 10:36:50

1. 拿到板子先研究一下硬件。紅色的板子蠻好看。在底面有一個小模塊,我估計是 JTAG下載模塊。2. 去官網下載資料,地址如下:http://www.em.avnet.com/artix7

2016-11-06 16:54:52

:“\Xilinx\Vivado\2016.2\data\boards\board_parts\artix7”)。點擊下一步,顯示新項目總結。點擊finsh,這樣你個新的工程就建立完成了。這樣就可進行開發了。今天就到

2016-10-22 20:55:58

。 反面二、簡單測試接下來是串口測試,學生party不像老司機拿到板卡就調試串口,測試板卡的資源情況。希望以后養成這種習慣吧!我用的是串口調試助手1.3,測試數據如下:Artix-7 50T - IIC

2016-12-07 08:46:04

無效。忽略電壓設置...在日志消息窗口中,它顯示為:[Designutils 20-266]家庭artix7的無效電壓源VCCINTIO。忽略電壓設置。以下約束(以及其他)在我的xdc文件中,但我不明白

2018-10-30 18:03:48

大家好,我有一個使用Artix7 200部件的大型設計,該設計有超過100個輸入,使用IDELAY2跨越8個庫,根據這里的建議,我只需要為整個設計實例化1個IDELAYCTRL,我已經完成了它工作

2020-08-10 06:36:18

對于artix7系列,通常咱們使用需要使用以下電源軌:參考文檔:DS181 (v1.22) April 13, 2017Artix-7 FPGAs Data Sheet: DC and AC

2021-11-17 08:28:49

我使用ARTIX7固化程序,顯示DONE DID NOT GO HIGH,然后DONE引腳外接3.3V上拉電阻,求大神指點該怎么改?大致是什么問題?

2017-04-07 20:56:38

有著嚴格的浪涌電流和穩態工作電流限值要求,因此由總線供電的器件應用經常忽視FPGA,而是更愿意采用性能和靈活性都不及 FPGA 的微控制器解決方案。隨著賽靈思低功耗系列器件中最新成員Artix-7

2016-07-27 17:14:50

大家好,我在artix7上使用ICAP進行部分比特流編程時遇到問題。我有一個靜態和部分比特流,當用jtag編程時工作正常,所以比特流似乎沒問題。我可以通過icap觸發Multiboot,所以我假設

2020-08-06 09:15:36

。 MicroCore實驗室目前在開發超小型,基于微定序器的嵌入式處理器內核具有非常多的經驗,其處理器內核可以在任何FPGA或ASIC技術中實現。他們最近實現了基于Artix-7 以 MCL51 為內核的同步模塊冗余

2017-10-10 10:28:21

和時序邏輯設計空間。我們選擇的是FPGA技術發明人創立的Xlinx公司生產的Artix7家族性能中等的xc7a35t芯片,但即使是較低性能的它也擁有多達數以萬計的單位。如圖所示,Xlinx采用的架構有

2021-07-23 07:49:55

前言TLA7-EVM開發板是一款由廣州創龍基于Xilinx Artix-7系列FPGA自主研發的核心板+底板方式的開發板,可快速評估FPGA性能。核心板尺寸僅70mm*50mm,底板采用沉金無鉛工藝

2020-09-23 16:27:12

你好,我有興趣使用Artix-7 FPGA進行以太網協同仿真(在Simulink中通過System Generator)。在System Generator中,我看到AC701

2020-07-15 08:45:40

的筆記本電腦我想將一些比特流文件發送到NEXYS 4 Board中的Artix-7 Xilinx FPGA,然后使用這個比特流數據存儲閃光燈。我已經為這塊板提供了Pmod Wifi模塊。可以與我的筆記本電腦

2020-04-30 07:46:17

據我所知,Xilinx建議采用SEM來減輕SEU對7系列FPGA的影響。但Artix-7 FPGA不支持ISE 14.2中的SEM,這與Xilinx的建議(http://www.xilinx.com

2020-07-14 07:01:12

大家好!我在Artix 7- 200T-676-1(如xilix板AC701)上設計了fgpa。我想使用QSPI閃存進行大量工作:多重啟動,Microblaze多用戶軟件,用戶定義等。但是我不能

2020-07-14 16:02:01

嗨,我是一名對FPGA很新的學生。我從大學實驗室借了一臺Artix-7 Nexys 4 DDR板,試圖用它來編寫一個基本的全加器。按照教程后,我意識到我已經刪除了默認配置文件,并將我的全加器程序

2019-10-08 10:29:12

嗨,我正在將我的IP從Spartan 3(ISE)遷移到artix7(VIVADO)。我注意到以下內容為VIVADO中的FIR濾波器設計生成的IP接口與ISE Core gen中生成的IP接口不同。我可以知道背后的原因嗎?是否有解決方法以確保兩個接口都相同。帶著敬意Vintu

2020-07-19 08:13:34

您好,我正在嘗試將adc(AD9287)與我的artix 7設備連接。 Adc提供串行lvds輸出。我正在使用iserdes(selectio)模塊,但問題是我不知道adc輸出的確切開始時間,因此

2020-07-29 07:59:25

問候所有。我是FPGA和HDL世界的新手,現在我正在嘗試從XADC獲取一些樣本后在FPGA Artix7板上實現FFT內核。但我在控制核心方面遇到了一些問題并取得了良好的效果,特別是我在FFT

2020-05-19 08:56:14

我正在設計一個子板,上面有40個Artix 7(AC7A12T)設備。每臺設備都應具有相同的圖像。我不是一次編程鏈1中的每個器件的串行鏈,而是希望并行執行任務,以便所有FPGA同時進行編程。我似乎

2020-05-14 07:01:03

您好,我的名字是JungMin Lee。我正在繪制一個包含Aritx-7的原理圖。我把AC701(artix7評估板)用于我的設計。但我有一個問題。如果我沒有ADC,MGT等......我只想獲得

2019-09-09 08:46:19

基于FPGA Xlinx Artix7平臺的聲源定位裝置設計項目來源:2019年第三屆全國大學生FPGA創新設計競賽一、設計概述 /Design Introduction1.1 設計目的基于麥克風

2021-08-06 09:27:12

大家好,我是Lalith kumar,我們正在使用Artix7 50t FPGA。由于板載空間限制,我們計劃連接512 Mb Quad SPI / BPI閃存,用于FPGA配置以及用戶數據接口。是否

2020-06-09 14:57:11

親愛的先生我嘗試在Artix-7 FPGA之間進行像LVDS這樣的DDR差分信號傳輸。但是我不能在Artix-7中使用SelectIO IP。有人能告訴我示例設計嗎?謝謝。

2020-08-18 09:34:09

嗨, 我想使用MMCM時鐘生成模塊來實時和動態地改變Artix FPGA中的相移。但我見過Xilinx UG472& PG065用戶指南和時鐘設置手冊。我使用PSCLK,PSEN

2020-08-11 10:33:29

嗨,我對AC701板上的SATA主機控制器實現有點困惑。是否可以實施SATA 3或僅限于SATA2。有些信息令人困惑,因為我看到sata 3它需要速度等級3 ARTIX7。有沒有人在ac701中實現SATA3?謝謝

2019-10-08 10:08:15

基于ARM+FPGA架構,高速采集和高清顯示二合一CPU集成i.MX 8M Mini+ARTIX7處理器,二合一成本優勢明顯;高性能的ARM MPU+多媒體能力,良好

2022-11-04 16:12:46

FPGA, Artix-7, MMCM, PLL, 285 I/O, 628 MHz, 101440單元, 950 mV至1.05 V, FBGA-484Xilinx Artix?-7 FPGA系列

2023-05-10 16:03:24

本文是關于賽靈思Artix-7 FPGA 數據手冊:直流及開關特性的詳細介紹。 文章中也討論了以下問題: 1.全新 Artix-7 FPGA 系列有哪些主要功能和特性? Artix-7 系列提供了業界最低功耗、最低成本

2012-06-12 10:24:12 118

118 Nexys?4_Artix-7_FPGA_開發板原理圖。

2016-08-03 19:37:24 129

129 Artix-7是賽靈思28nn FPGA系列之一,它采用采用小型化封裝、統一的 Virtex 系列架構,相對于 Spartan-6系列而言,Artix-7系列功耗降低了一半,成本降低了35

2016-08-04 09:23:11

本來想著把GTX后面兩篇博文找時間寫了,但是最近實在是忙,一直在搭圖像處理的AXI框架和整FPGA-DSP雙平臺的板子,下面先和大家分享一下調試心得。

2017-03-21 10:56:11 3054

3054

Xilin新推出小型產品的Artix-7 FPGA,我們將向大家講解:Artix-7 DSP性能演示。

2018-06-05 07:46:00 3916

3916 Xilinx推出新品小型產品的Artix-7 FPGA,我們將為大家講述:Artix-7 功耗優勢演示。

2018-06-04 13:47:00 4117

4117 Xilinx公司面向大批量應用的的Artix-7 FPGA的能耗優勢演示。

2018-06-04 02:47:00 2852

2852 See why Cobham chose to use the Artix-7 100T FPGA to reduce the size, weight and power consumption of one of their latest products.

2018-11-21 06:14:00 3891

3891 在本視頻中,您將了解Artix-7 FPGA的整體系統功耗和成本。

我們將快速回顧一下Artix-7 FPGA架構,邏輯架構,第四代DSP48E1片,6.6 Gbps GTP收發器,PCIe Gen2硬塊,存儲器接口,模擬..

2018-11-21 06:10:00 3457

3457 該視頻演示了基于Artix-7的低功耗ARTY FPGA評估套件,該套件采用-1LI Artix-7 FPGA。

對于演示,該套件的工作功率不到半瓦,運行真實設計,并配有軟處理器。

2018-11-29 06:23:00 2506

2506 Artix7和Spartan7系列提供低成本、小占地面積的高效FPGA陣列,旨在滿足低端市場的特殊需求。

2019-02-19 11:53:28 16

16 Artix-7 FPGA數據表下載

2021-05-21 14:34:46 8

8 XILINX ARTIX7系列FPGA芯片產品目錄

2021-10-08 17:09:20 26

26 對于artix7系列,通常咱們使用需要使用以下電源軌:參考文檔:DS181 (v1.22) April 13, 2017 Artix-7 FPGAs Data Sheet: DC and AC

2021-11-10 12:06:04 9

9 電子發燒友網站提供《在Artix 7 FPGA上使用Vivado的組合邏輯與順序邏輯.zip》資料免費下載

2023-06-15 09:14:49 0

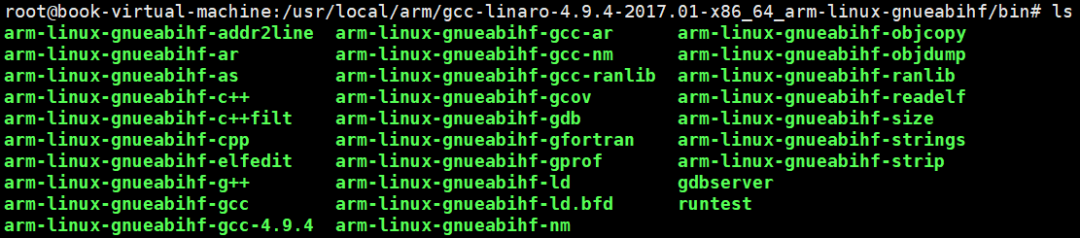

0 在板子中調試 上面的方法是直接在 ubuntu 調試源代碼,只能查看源代碼的錯誤,如果你想要你的應用程序在板子中運行,想打出它在板子上運行的 bug,就要采用下面的方法。 一般的桌面 Linux

2023-07-27 16:37:53 732

732

電子發燒友App

電子發燒友App

評論