利用FPGA實現雙口RAM的設計及應用

概述:為了在高速采集時不丟失數據,在數據采集系統和

2010-04-16 14:08:36 11323

11323

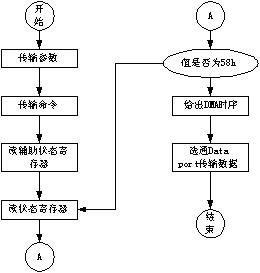

1. 背景 這篇文章主要介紹了DDR3IP核的寫實現。 2. 寫命令和數據總線介紹 DDR3 SDRAM控制器IP核主要預留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 5068

5068

了設計的一大挑戰。FPGA可通過在單個FPGA中實現多個視頻處理器來提供強大的處理能力。那么現在的挑戰就變成了要使數據盡快且高效地從FPGA進出。DDR3存儲器系統在大多數情況下可以為這些基于FPGA的系統

2019-05-24 05:00:34

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

更快、更大,每比特的功耗也更低,但是如何實現FPGA和DDR3 SDRAM DIMM條的接口設計呢? 關鍵字:均衡(leveling)如果FPGA I/O結構中沒有包含均衡功能,那么它與DDR

2019-04-22 07:00:08

各位大神,我最近在做FPGA項目遇到一個問題,我想實現這樣的功能:向RAM里寫一次數據,再多次讀出來,可是我發現IP核里的RAM讀第二次的時候RAM數據就清零了,根本讀不我寫的數據,請問有什么好的解決辦法嗎?謝謝啦!

2015-06-07 20:31:57

和DDR2/DDR3控制器(含DIMM);能夠理解和使用FPGA中關于DDR器件的專用電路;能夠使用和分析FPGA廠家提供的相關IP,以及8層PCB板層設計到BGN封裝;能夠了解高速數據傳輸的必要知識

2015-09-29 16:33:54

SDRAM和DDR2/DDR3控制器(含DIMM);能夠理解和使用FPGA中關于DDR器件的專用電路;能夠使用和分析FPGA廠家提供的相關IP,以及8層PCB板層設計到BGN封裝;能夠了解高速數據傳輸的必要

2015-09-30 10:36:41

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面寫FPGA的BANK1,3連接外部存儲控制器(如下圖,且只有四個BANK),所以要將DDR3連接在BANK3上。所以DDR3如何與FPGA芯片

2021-11-29 16:10:48

的相關內容,學習FPGA設計方法及設計思想的同時,實操結合各類操作軟件,會讓你在技術學習道路上無比的順暢,告別技術學習小BUG卡破腦殼,告別目前忽悠性的培訓誘導,真正的去學習去實戰應用。話不多說,上貨。IP

2023-03-14 17:38:29

實現特權同學的例程 特權FPGA VIP視頻圖像開發套件例程詳解2——DDR2控制器讀寫測試 時,進行IP核配置時,進入下一步配置參數時,變成黑屏重裝軟件也不行

2018-01-24 08:23:17

實現特權同學的例程 特權FPGA VIP視頻圖像開發套件例程詳解2——DDR2控制器讀寫測試 時,進行IP核配置時,進入下一步配置參數時,變成黑屏重裝了軟件也不行,到這個頁面還是黑屏,軟件版本是13.0

2019-05-17 06:35:42

就已經出現,隨著FPGA芯片價格的不斷降低,其在工業領域的應用正在飛速發展,采用FPGA來實現SVPWM調制算法也將層出不窮2. 系統任務分析及實現SVPWM調制算法相對比較復雜,在完成系統控制任務

2022-01-20 09:34:26

集中于非PCI部分,通過將FPGA廠商提供的IP模塊與原理圖、狀態機及HDL語言等設計方法有機的結合,采用層次化結構,在功能強大的EDA軟件環境下,于較短的時間內完成復雜電子系統的設計。來源

2019-05-08 07:00:46

×16bit)的DDR2 SDRAM為存儲器。用一個IP核完成對4片DDR2的控制(帶寬為64bit),且DDR2的最高速率可達200MHz,以此完成對數據的高速大容量存儲。由于采用一個DDR2的IP核進行控制

2019-05-31 05:00:05

章禮宏 范全潤1 引言隨著電路規模不斷擴大,以及競爭帶來的上市時間的壓力,越來越多的電路設計者開始利用設計良好的、經反復驗證的電路功能模塊來加快設計進程。這些電路功能模塊被稱為IP

2019-07-29 08:33:45

該IP核驗證平臺采用ALTERA Cyclone系列FPGA,型號為EP1C12Q240C8,提供超過30萬門系統資源和240k bit的內部高速FIFO, 以及內部兩個高速PLL,可以合成

2019-06-20 05:00:02

該IP核驗證平臺采用ALTERA Cyclone系列FPGA,型號為EP1C12Q240C8,提供超過30萬門系統資源和240kbit的內部高速FIFO, 以及內部兩個高速PLL,可以合成10M到

2019-06-12 05:00:07

和標準化。 在第一個專用 HVL(硬件驗證語言)出現后不久,驗證方法就應運而生。采用方法論(如 UVM)的主要優點是? 通過測試臺重用和驗證 IP 實現即插即用的可重用性? 一種行之有效的方法,具有行業

2022-02-13 17:03:49

...............................................11.2 FPGA 驗證技術...............................................31.3 Altera

2015-09-18 15:26:25

擁有成本,從而帶來可持續的長期盈利能力。美高森美公司(Microsemi)提供具有硬核ARM Cortex-M3微控制器和IP集成的SmartFusion2 SoC FPGA器件,它采用成本優化的封裝

2019-06-24 07:29:33

先進的設計與仿真驗證方法成為SoC設計成功的關鍵。一個簡單可行的SoC驗證平臺,可以加快SoC系統的開發與驗證過程。FPGA器件的主要開發供應商都針對自己的產品推出了SoC系統的開發驗證平臺,如

2019-10-11 07:07:07

你好任何人都可以指導我,Xilinx ISE中的DDR控制器是否有任何IP實現。如果沒有如何實現DDR控制器以上來自于谷歌翻譯以下為原文Hi can any one guide me

2019-02-27 12:13:51

請教各位大神,小弟剛學FPGA,現在在用spartan-3E的板子,想用上面的DDR SDRAM進行簡單的讀寫,用MIG生成DDR核之后出現了很多引腳,看了一些資料也不是很清楚,不知道怎么使用生成的這個IP核控制器來進行讀寫,希望大神們稍作指點

2013-06-20 20:43:56

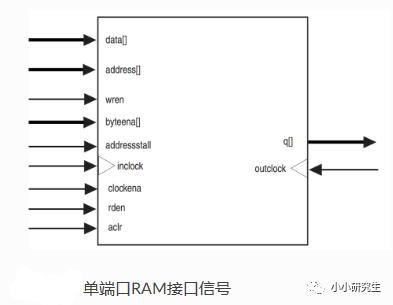

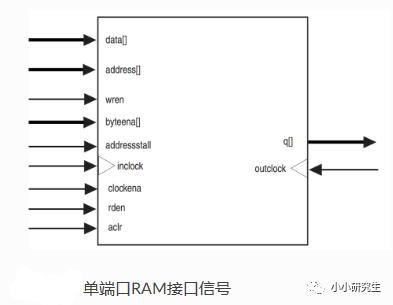

Altera Cyclone 系列FPGA器件的內部結構,然后介紹了RAM IP核的調用方法和配置窗口中的一些參數含義,然后通過仿真的方式對RAM IP核的接口時序進行了分析,為下一節課,RAM IP

2015-10-23 12:47:16

給FPGA,FPGA接收后存儲在RAM中,再在按鍵的控制下,讀取RAM中的數據,通過串口發送出去。來體現模塊化設計的巨大優勢。同時,視頻花了相當的時間來演示使用Visio繪制系統架構圖,一個好的架構圖

2015-10-23 13:01:50

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

設計來增設全新的芯片功能,據此實現了芯片整體構造的簡化與性能提升。下面英尚微電子介紹FPGA開發板內部ram是如何操作的。 除邏輯外,所有新的FPGA都有專用的靜態ram塊,這些塊在邏輯元素之間分布并由

2020-09-10 11:11:57

你好,先生或女士我是中國學生。我已經研究FPGA一段時間了,我正在嘗試使用FPGA來實現FC協議。經過一番研究,我發現GTH可以達到FC1。但是我發現使用7系列FPGA收發器向導IP存在一些問題。我

2020-08-17 10:28:07

采用FPGA來實現,TM的常規結構如圖1所示。圖1TM的常規結構圖 目前主流的TM接口均為SPI4-P2接口形式,SPI4-P2接口信號速率高,TCCS(Channel-to-channel skew

2012-11-09 18:43:41

`例說FPGA連載36:DDR控制器集成與讀寫測試之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實例對Altera提供

2016-10-08 17:05:55

`例說FPGA連載38:DDR控制器集成與讀寫測試之FPGA片內RAM概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 我們所

2016-10-12 17:18:25

`例說FPGA連載39:DDR控制器集成與讀寫測試之FPGA片內RAM設置與集成特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc

2016-10-14 18:07:34

`例說FPGA連載41:DDR控制器集成與讀寫測試之DDR2 IP核接口描述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖

2016-10-27 16:36:58

。● ddr2_controller.v二級子模塊也是一個軟核IP,實現DDR2的時序控制功能,并且通過一個簡單的Avalon接口實現DDR2和FPGA邏輯之間的讀寫數據傳輸。其實該模塊下還有多個子模塊,但由于只是一個IP核,內部代碼不

2016-11-08 18:18:29

利用FPGA自帶的IP核實現雙口RAM用于2片MCU進行數據交換時多次讀數據后RAM中數據變為了0,是什么意思,打什么幫幫忙!!!!!!!!!!!!!!

2018-01-15 16:22:16

。 本手冊以一個經過驗證的可穩定工作的設計為例,來系統介紹高云FPGA連接DDR3的硬件設計方法,FPGA芯片型號采用GW2A-LV18PG256,存儲芯片采用鎂光(Micron)公司生產的單晶粒封裝

2022-09-29 06:15:25

進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行類FIFO接口的封裝,屏蔽掉了DDR3 IP核復雜的用戶接口,為DDR3數據流緩存的實現提供便利。系統測試表明,該

2018-08-02 09:34:58

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核實現高速率DDR3芯片控制的設計思想和設計方案。針對高速實時數字信號處理中大容量采樣數據通過DDR3存儲和讀取的應用背景,設計和實現了

2018-08-30 09:59:01

的應用。采用FPGA技術構造雙口RAM,實現高速信號采集系統中的海量數據存儲和時鐘匹配。功能仿真驗證該設計的正確性,該設計能減小電路設計的復雜性,增強設計的靈活性和資源的可配置性能,降低設計成本,縮短

2010-04-24 09:44:28

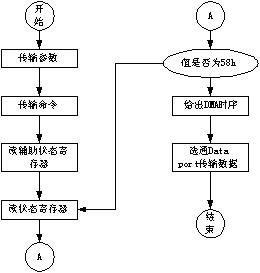

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

2019-07-09 07:23:09

但是,如果FPGA通過接口與DSP核心連接,并且高速視頻數據是通過它來傳輸,那么它根本不是簡單的系統。這種更高的設計復雜度導致了額外的驗證難題,并且如果您在設計階段晚期發現一處重大錯誤,那么這還會導致高成本的系統板重制。為了消除這一隱患,您必須仔細考慮自己采用的驗證方法,以便降低重制風險。

2019-09-19 06:00:59

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

工具,經面向硬件電路的仿真驗證,本文的方法可實現OC-48接口(2.5Gb/s)上線速分組的IP碎片重組,并具有硬件開銷小,可擴展性好的特點。關鍵詞: IP碎片;FPGA;RLDRAM控制器;最大傳輸

2008-10-07 11:00:19

Xilinx公司發布的SP6,V6系列的FPGA中的DDR2的IP核是一大改變。它由原來的軟核變為了硬核,此舉讓開發DDR2變的簡單,因為不需要太多的時序調試,當然也帶來了麻煩,這是因為當DDR

2015-03-16 20:21:26

Flow將其轉成ASIC版圖.實現流片。2.3 IP核的驗證方法在芯片的設計流程中設計的驗證是一個重要而又費時的環節。在進行Top_Down設計時.從行為級設計開始到RTT級設計再到門級設計相應地利

2021-09-01 19:32:45

1 簡介隨著設計的復雜程度不斷增加,要求把更多的資源放到驗證上,不但要求驗證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應異常的處理狀態,這在傳統測試方法下往往是難以實現的。此外

2019-07-03 07:40:26

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一個單獨的奇偶校驗寫使能位,但在FPGA RAM中沒有單獨的Pariaty寫使能位。 如何實現ASIC RAM奇偶校驗寫入啟用ino FPGA RAM。謝謝娜文G K.

2020-04-24 09:37:05

隨著電路規模不斷擴大,以及競爭帶來的上市時間的壓力,越來越多的電路設計者開始利用設計良好的、經反復驗證的電路功能模塊來加快設計進程。這些電路功能模塊被稱為IP

2019-09-03 07:44:22

如何采用現場可編輯門陣列FPGA來實現對直流電機的控制?

2021-10-19 09:08:30

請教各位大佬,UVM是基于sv的驗證方法學,如果采用systemc語言編程,如何實現?

2019-11-07 15:30:16

的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰性。在FPGA中實現高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊

2019-08-09 07:42:01

Xilinx DDR 控制器。 DDR PHY 與電路板調試: Zynq UltraScale+ MPSoC VCU DDR 控制器采用 MIG PHY。 這意味著您可以使用標準 MIG 示例設計來驗證您

2021-01-07 16:02:09

本帖最后由 小梅哥 于 2015-6-15 22:18 編輯

各位喜愛FPGA技術的小伙伴。小梅哥FPGA設計思想與驗證方法視頻教程的課程大綱已經出爐,歡迎大家根據自己的實際感受,提出各種批評

2015-06-15 22:01:45

大家好,我想設計自己的DDR控制器并在FPGA上驗證它。我將在verilog中實現我剛開始閱讀JESDC79C DDR規格..但我很困惑如何編寫那些初始化序列?請建議如何處理這個設計DDR控制

2019-04-29 11:59:22

DDR2控制和FPGA實現

2015-07-21 19:28:14

步進電機控制通常采用什么方法實現?

2021-09-30 07:15:35

錯誤檢查硬件,監視軟錯誤導致的變化。由于這些硬核IP 是在FPGA 邏輯區中實現的,因此,系統處理器不再承擔這些任務。設計按照Altera 的建議來實現。在認證方法方面,Altera 采用了IEC 規范

2013-11-20 16:57:29

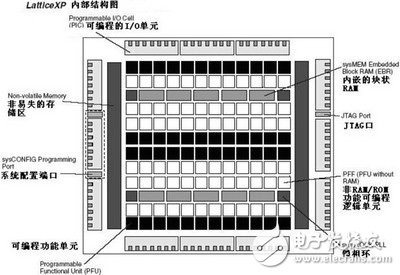

本文介紹一種采用Lattice FPGA與IP來實現DDR RAM控制和驗證的方法。

2021-05-06 09:52:30

IJF編碼是什么原理?如何實現IJF編碼?采用FPGA和集成器件來實現IJF編碼

2021-04-13 06:56:04

本文介紹一款USB 設備控制器IP CORE 的設計與實現。論文首先介紹了USB 設備控制器的設計原理,模塊劃分及每個模塊的功能。然后介紹了該IP CORE 在ModelsimSE 中的功能仿真及FPGA 驗證結

2009-08-06 11:39:00 8

8 針對當今電子系統對高速大容量內存的需要,本文闡述了使用DDR 控制器IP 核來設計實現DDR內存接口的方法。該方法能使設計盡可能簡單,讓設計者更專注于關鍵邏輯設計,以便達到

2009-08-11 09:42:51 20

20 NandFlash控制器的FPGA實現方法技巧與程序案例分享。

2017-09-21 09:40:00 78

78 為了在高速采集時不丟失數據,在數據采集系統和CPU之間設置一個數據暫存區。介紹雙口RAM的存儲原理及其在數字系統中的應用。采用FPGA技術構造雙口RAM,實現高速信號采集系

2010-02-11 11:20:27 69

69 本文主要闡述了在某雷達系統中為實現偽碼對齊,所采用的滑動控制方法的原理及在FPGA芯片上的實現。

2010-03-02 16:04:22 13

13 DDR驗證和調試的高級方法:Memory Design and ValidationChip/Component DesignPrecise understanding of circuit

2010-06-29 17:16:13 21

21 采用FPGA和DSP直接控制硬盤實現存儲控制的方法

摘 要 介紹了采用FPGA和DSP直接控制硬盤進行數據存儲的方法,并采用一片FIFO作為數據緩存,能夠滿足80Khz數

2010-01-12 11:27:22 981

981

利用FPGA實現時分多址的方法有很多種,但大多數方法都對FPGA芯片資源的占用非常巨大。針對這一問題,提出一種改進型方法來實現時分多址。通過使用FPGA芯片內部的雙口隨機訪問存儲器(雙口RAM),利用同一塊RAM采用兩套時鐘線,地址線和數據線,例化雙口RAM的

2011-01-15 15:41:26 29

29 本文側重于介紹IP 模塊中組件控制器的設計和實現。一個基于FPGA 的LCD 控制器設計作為例子被介紹。這個組件控制器設計屬于固核IP 設計,也就是軟硬結合的方法。設計內容主要包括電

2011-12-22 14:00:11 1143

1143

基于FPGA的SD卡控制器IP,以驗證可用。

2015-11-06 09:50:50 10

10 DDR2SDRAM控制器IP功能測試與FPGA驗證_陳平

2017-01-07 21:45:57 3

3 技術方法,驗證了SoC系統、DSP指令、硬件IP等。實驗證明,此FPGA驗證平臺能夠驗證SoC設計,提高了設計效率。

2017-11-17 03:06:01 13138

13138

為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器,只需通過用戶接口信號就能完成DDR

2017-11-18 18:51:25 6412

6412

提出一種便于用戶操作并能快速運用到產品的DDR2控制器IP核的FPGA實現,使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過IP核控制DDR2。簡單介紹了DDR2的特點和操作

2017-11-22 07:20:50 4687

4687

,理解內存控制器對存儲設備的控制機制;然后,設計了接口協議解析邏輯的總體架構,采用FPGA實現并對其中的各個關鍵技術點,包括時鐘、寫平衡、延遲控制、接口同步控制等進行詳細闡述;最后,通過modelsim仿真并進行板級驗證,證明了該設計的正確性和可行

2017-12-05 09:34:44 10

10 本文實現的基于FPGA的PCIe總線接口的DMA控制器是在Altera PHY IP和Synopsys Core IP的基礎上實現的,利用Synopsys VIP驗證環境進行了功能仿真驗證

2018-01-11 10:57:04 11281

11281

大家好,又到了每日學習的時間了,今天我們來聊一聊在FPGA設計中RAM的兩種使用方法,RAM是用來在程序運行中存放隨機變量的數據空間,使用時可以利用QuartusII的LPM功能實現RAM的定制

2018-06-08 11:30:28 19562

19562 實現數據的高速大容量存儲是數據采集系統中的一項關鍵技術。本設計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態機來描述對DDR SDRAM 的各種時序

2019-08-14 08:00:00 3401

3401

復旦大學微電子學院某國家重點實驗室內部教學視頻:基于ZYNQ FPGA與PC的IP設計與驗證方案。

關鍵詞:IP設計,IP驗證,AXI總線協議,ARM,UDP傳輸,PYTHON

2019-08-06 06:16:00 1968

1968

學完SDRAM控制器后,可以感受到SDRAM的控制器的書寫是十分麻煩的,因此在xilinx一些FPGA芯片內已經集成了相應的IP核來控制這些SDRAM,所以熟悉此類IP核的調取和使用是非常必要的。下面我們以A7的DDR3 IP核作為例子進行IP核調取。

2019-11-10 10:28:45 4702

4702

DesignWare DDR5/4 PHY IP核提供基于固件的訓練,無需更改硬件即可進行現場升級,從而幫助客戶降低采用新協議的風險。基于固件的訓練也有助于使用復雜的訓練模式,在系統層面上支持最高裕度和通道可靠性。

2020-08-28 15:38:04 1986

1986 DDR對于做項目來說,是必不可少的。一般用于數據緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 開發工具:Vivado

2020-11-26 15:02:11 7386

7386

核的使用。 ? ? BRAM是FPGA定制的RAM資源,有著較大的存儲空間,且在日常的工程中使用較為頻繁。BRAM以陣列的方式排布于FPGA的內部,是FPGA實現各種存儲功能的主要部分,是真正的雙讀/寫端口的同步的RAM

2020-12-29 15:59:39 9496

9496 基于FPGA的DDR3SDRAM控制器設計及實現簡介(arm嵌入式開發平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器設計及實現(嵌入式開發式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 13:07:09 35

35 本實驗基于xilinx ARTIX-7芯片驗證實現,有時間有興趣的朋友可在其他FPGA芯片上實現驗證。

2023-04-11 10:51:14 703

703 我們知道除了只讀存儲器外還有隨機存取存儲器,這一篇將介紹另一種 存儲類IP核 ——RAM的使用方法。RAM是 隨機存取存儲器 (Random Access Memory),是一個易失性存儲器,斷電丟失。RAM工作時可以隨時從任何一個指定的地址寫入或讀出數據。

2023-08-29 16:46:07 1660

1660

本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現讀寫操作。

2023-09-01 16:23:19 745

745

定制的RAM資源,有著較大的存儲空間,且在日常的工程中使用較為頻繁。BRAM以陣列的方式排布于FPGA的內部,是FPGA實現各種存儲功能的主要部分,是真正的雙讀/寫端口的同步的RAM。 本片

2023-12-05 15:05:02 317

317 FPGA雙口RAM的使用主要涉及配置和使用雙端口RAM模塊。雙端口RAM的特點是有兩組獨立的端口,可以對同一存儲塊進行讀寫操作,從而實現并行訪問。

2024-03-15 13:58:14 81

81

電子發燒友App

電子發燒友App

評論