1 前言

發(fā)射機是無線通信的重要設(shè)備之一,廣泛應(yīng)用于廣播電視、移動通信、海洋運輸及國防等領(lǐng)域。自動控制技術(shù)在無線通信發(fā)射領(lǐng)域正發(fā)揮著越來越重要的作用,發(fā)射設(shè)備的數(shù)字化逐漸趨于成熟。但是,大功率短波發(fā)射機比起中波、調(diào)頻、電視發(fā)射機來說,具有變換工作頻率頻繁,倒頻時間短;不能實現(xiàn)整機固態(tài)化,可靠性降低,故障率較高;工作頻段范圍寬,很難保證在全頻段內(nèi)任意頻率穩(wěn)定工作等特點;加之目前尚無接口標(biāo)準(zhǔn)對大功率短波發(fā)射臺微機實時控制進(jìn)行規(guī)范,給大功率短波發(fā)射臺自動化帶來困難。短波發(fā)射機的自動調(diào)諧技術(shù)正是在這種環(huán)境下產(chǎn)生的。

本設(shè)計的自動調(diào)諧系統(tǒng)是基于FPGA和AVR單片機的,其調(diào)諧對象是功率為150kW,發(fā)射頻率范圍為3.9 26.1MHz的短波發(fā)射機。系統(tǒng)結(jié)構(gòu)如圖1所示:

?

2 FPGA簡介

FPGA是現(xiàn)場可編程門陣列(Field Program一able Gate Array)的簡稱,是新一代的自動調(diào)諧控制單元,它采用VHDL語言進(jìn)行現(xiàn)場編程,其特點是:I/O資源豐富,運算速度快(ns級),集成度高,穩(wěn)定性好,包含的LUT和觸發(fā)器數(shù)量豐富等等。

鑒于這些特點,系統(tǒng)擬采用單片機與現(xiàn)場可編程門陣列(FPGA)組合的方式。FPGA主要完成人機界面、測定發(fā)射機工作頻率及調(diào)整元件位置的邏輯設(shè)計,單片機則完成上位機通信、元件位置數(shù)據(jù)采集、存儲系統(tǒng)參數(shù)等任務(wù)。本系統(tǒng)設(shè)計中主要完成系統(tǒng)邏輯部分設(shè)計。圖2所示為系統(tǒng)邏輯結(jié)構(gòu)。

系統(tǒng)中的各邏輯模塊設(shè)計主要用VHDL硬件描述語言完成。

3 系統(tǒng)功能概述

3.1 自動調(diào)諧

發(fā)射機自動調(diào)諧是指在調(diào)諧過程中根據(jù)當(dāng)前發(fā)射機的工作頻率,將各個調(diào)諧元件調(diào)到與該頻率相對應(yīng)位置的操作過程。短波發(fā)射機各用電單元的通斷,是通過配電箱中相應(yīng)接觸器的通斷來實現(xiàn)。控制接觸器通斷的信號是由調(diào)諧邏輯小盒產(chǎn)生。自動調(diào)諧控制套箱是用來實現(xiàn)本發(fā)射機的高頻回路元件在換頻時的機械定位進(jìn)行調(diào)諧控制。為了達(dá)到調(diào)諧的目的,自動調(diào)諧系統(tǒng)需要完成以下幾項工作:

(1)為了實現(xiàn)工作人員對發(fā)射臺的遠(yuǎn)程監(jiān)控,需要將自動調(diào)諧系統(tǒng)與在線計算機相連;

(2)系統(tǒng)需要設(shè)置各種參數(shù),需要有簡易的人機界面,主要是鍵盤和LED顯示;

(3)系統(tǒng)參數(shù)的存儲及調(diào)用;

(4)發(fā)射機實際工作頻率的測定;

(5)調(diào)諧元件位置信息的采集;

(6)控制執(zhí)行電機調(diào)節(jié)元件位置。

3.2 調(diào)諧原理

操作人員先通過控制面板創(chuàng)建各個工作頻道,每個工作頻道中保存有發(fā)射機的工作頻率及頻率所對應(yīng)的可調(diào)元件位置值。創(chuàng)建完工作頻道后,就可以進(jìn)入正常的調(diào)諧工作。選擇一個工作頻道,并按功能鍵,系統(tǒng)將向單片機發(fā)出中斷請求,F(xiàn)PGA從單片機的EEPROM中取出該頻道所對應(yīng)的頻率值及8個調(diào)諧元件位置信息,經(jīng)單片機采集的8路調(diào)諧元件

實際位置信息也傳送給FPGA,用于與預(yù)置值相比較,差值用于控制電機。調(diào)諧系統(tǒng)還有一個自動測頻模塊,該模塊用于測定發(fā)射機實際工作頻率,當(dāng)該數(shù)值與預(yù)定值相等時,系統(tǒng)自動預(yù)置元件位置值。

系統(tǒng)的主要有效參數(shù)有:工作頻道、工作頻率、被調(diào)元件的位置值。

全機共有8個被調(diào)元件:

1路— — 高前級回路電容器,作為本級調(diào)諧(粗調(diào)、細(xì)調(diào))用;

2路—— 高末級腔體短路板,僅作粗調(diào):

3路—— 高末級態(tài)調(diào)諧電容,作為粗調(diào)、細(xì)調(diào)用;

4路—— 高末級調(diào)諧電容,作為粗調(diào)用;

5路—— 高末級調(diào)載電容,作為粗調(diào)、細(xì)調(diào)用:

6路—— 高末級調(diào)載線圈,作為粗調(diào)用;

7路—— 作為備用;

8路—— 高前級調(diào)諧電感,作為粗調(diào)用。

3.3 調(diào)諧方式

本系統(tǒng)具有“手動”、“半自動”、“自動’,3種調(diào)諧方式。

系統(tǒng)正常工作過程中主要使用“自動”調(diào)諧方式;能采用“預(yù)置”的前提是被調(diào)元件到位精確,系統(tǒng)的機械回差和電氣都在允許的范圍內(nèi);“半自動”方式是輔助方式,它能克服自動方式中總有個別頻率不能調(diào)到最佳狀態(tài)的缺點。

(1)手動方式

“手動”方式是在操作面板上進(jìn)行人工調(diào)諧的工作方式,用于初調(diào)諧和創(chuàng)建頻道、工作頻率及相應(yīng)被調(diào)元件的位置值。全部被調(diào)元件的細(xì)調(diào)和初始粗調(diào)都用手動控制完成的;“手動”給定位值的獲得,可通過面板上的使能鍵和0-9數(shù)字鍵盤手動進(jìn)行頻道初始化、工作頻率設(shè)置、8個可調(diào)元件的位置設(shè)置,每設(shè)置完一個頻道,可保存設(shè)置值。

設(shè)置一個頻道參數(shù)。一個頻道中的頻道值、工作頻率、元件位置值具有一一對應(yīng)關(guān)系,其中一個工作頻率對應(yīng)的8路元件值是專家給定值,如果存在偏差,可以進(jìn)行手動微調(diào)后再次保存。微調(diào)是人工目測,直至“鑒相器”的輸出值為零時,微調(diào)就告完成。通過微調(diào)以達(dá)到獲的最佳數(shù)據(jù)的目的。

(2)自動方式

“自動”和“半自動”都是在“預(yù)置”的方式下完成的。預(yù)置是指根據(jù)需要將存儲于存儲器中的有效參數(shù)(包括頻道、工作頻率、被調(diào)元件的實際位置)傳送至系統(tǒng)邏輯控制單元,用來重現(xiàn)曾經(jīng)調(diào)整正常的工作頻率。調(diào)諧裝置是根據(jù)激勵器的實際工作頻率進(jìn)行自動調(diào)諧工作的,自動調(diào)整過程分為下面幾個步驟。

①選定工作的頻道或工作頻率,為頻率預(yù)置;制器ATmega103。這個過程可稱 4.2 開發(fā)軟件

②根據(jù)工作頻率預(yù)置8路元件位置值,頻率和電平;

③將8路的預(yù)置位置分別與各自的實際位置進(jìn)行比較,計算出存在的比較誤差:

④根據(jù)各自比較結(jié)果誤差的大小和極性來控制相應(yīng)的執(zhí)行電機的正/反轉(zhuǎn),直至比較結(jié)果誤差等于零為止,電機不轉(zhuǎn)。

至此,系統(tǒng)調(diào)諧的粗調(diào)完成,這時整機無高頻輸出。最后,接通高頻,合上相應(yīng)高壓,令鑒相器工作,系統(tǒng)自動地將發(fā)射機準(zhǔn)確地調(diào)諧在振點上,稱為細(xì)調(diào)。

自動方式具有跟蹤工作頻率的能力,也稱為頻率跟蹤調(diào)諧。發(fā)射機共有8個可調(diào)元件,其中只有3個需要細(xì)調(diào),分別為1路、3路和5路。

自動調(diào)諧是按以下順序自動完成調(diào)諧的全過程:粗調(diào)—前級細(xì)調(diào)一末級調(diào)諧—末級調(diào)載—激勵電平設(shè)置。

(3)半自動方式

“半自動”方式是根據(jù)常用的工作頻道自動進(jìn)行預(yù)置,用“手動微調(diào)”手段進(jìn)行人工調(diào)諧的工作方式。主要是用于人工干預(yù)減緩調(diào)諧進(jìn)程和調(diào)試過程。半自動調(diào)諧方式對各路可調(diào)元件而言。頻率預(yù)置是自動進(jìn)行,而自動調(diào)諧的5個步驟(粗調(diào)、前級細(xì)調(diào)、末級細(xì)調(diào)、末級調(diào)載、電平調(diào)整)是手動干預(yù)分步進(jìn)行的。因此,頻率預(yù)置過程與自動方式一樣。

4 系統(tǒng)設(shè)計

4.1 芯片選擇

本調(diào)諧系統(tǒng)設(shè)計目的之一就是對偏遠(yuǎn)地區(qū)的廣播發(fā)射設(shè)備進(jìn)行技術(shù)改造,因此調(diào)諧系統(tǒng)的開發(fā)成本是必須考慮的問題之一。另外,本調(diào)諧系統(tǒng)邏輯設(shè)計大概需9萬邏輯門。而且FPGA芯片資源利用不宜過滿。據(jù)此,F(xiàn)PGA選用XILINX公司Spartan—II系列FPGA :XC2S100—5 PQ208。

xc2s100—5 PQ208提供的系統(tǒng)門數(shù)最大為1O萬門,具有208個引腳,速度等級為5。xC2S100的內(nèi)核采用2.5v供電,工作頻率最高可達(dá)200MHz。xC2S100具有豐富的I/O資源,I/O端口供電電壓為3.3V,可承受5V的輸入高電平,I/O口輸出緩沖器可以接收高達(dá)24 mA的拉電流和48 rnA的灌電流。

單片機采用ATMEL公司8位低功耗AVR微控制器ATmega103。

4.2 開發(fā)軟件

使用Xilinx Foudation F3.1i軟件開發(fā)XC2S100—5 PQ2O8芯片。設(shè)計流程為:首先用編寫VHDL語言程序、繪制原理圖或設(shè)計狀態(tài)機的方法生成表,功能仿真正確后,經(jīng)過邏輯綜合和布線、時序仿真,仿真通過后將編程下載。

4.3 系統(tǒng)模塊化設(shè)計

模塊化設(shè)計是用可編程邏輯器件設(shè)計數(shù)字系統(tǒng)的特點之一,這樣可以簡化系統(tǒng)設(shè)計,同時有利于協(xié)同設(shè)計。最后只需通過元件例化或原理圖連接將多個模塊聯(lián)系在一起,組成一個完整的邏輯系統(tǒng)。本調(diào)諧系統(tǒng)邏輯設(shè)計由多個模塊組成,下面重點介紹通信模快、鍵盤掃描及顯示、測頻模快、電機控制模塊。

4.3.1 FPGA與單片機通信

自動調(diào)諧系統(tǒng)是由單片機子系統(tǒng)及FPGA組成的,這就存在兩者之間的通信問題。單片機系統(tǒng)主要完成了可調(diào)元件的實際位置的數(shù)據(jù)采集、系統(tǒng)參數(shù)的存儲等,這些數(shù)據(jù)需要經(jīng)過FPGA的處理。

通信模塊要完成的數(shù)據(jù)傳輸有:頻道數(shù)、工作頻率及對應(yīng)的元件位置值,元件位置信息包括實際值和預(yù)置值,實際值有單片機系統(tǒng)采集得來,傳送至FPGA與預(yù)置值比較,產(chǎn)生控制信號。

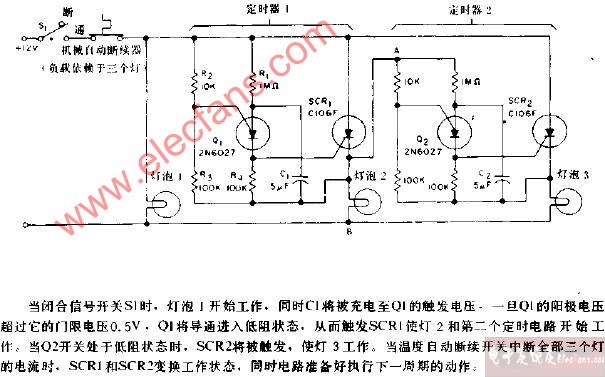

通信模塊根據(jù)單片機的讀寫時序完成兩者之間的互相通信。ATmegal03訪問片外SRAM的時序見圖3。

仿真中的時序是按照單片機的時序,從仿真結(jié)果中看出FPGA與單片機能按預(yù)定時序交換數(shù)據(jù)。圖4所示為通信模塊中部分信號的功能仿真結(jié)果。

4.3.2 鍵盤掃描及顯示

(1)鍵盤掃描

在鍵盤中按鍵數(shù)量較多時,為了減少I/O口的占用,通常將按鍵排列成矩陣形式,矩陣式鍵盤掃描及顯示都采用單片機來完成,這是因為單片機可以極方便的對矩陣式鍵盤進(jìn)行掃描控制。如果使用鍵盤顯示專用芯片,那將使控制變得更加簡單。但是,即使采用矩陣式鍵盤,掃描時仍然要占用大量的1/O資源,這對于I/O資源很有限的單片機來說,將會使編程變得很困難。對于本調(diào)諧系統(tǒng)來說,單片機需要完成于上位機的通信、元件數(shù)據(jù)采集、數(shù)據(jù)存儲等多項工作,I/O資源已經(jīng)很緊張。因此,本系統(tǒng)用FPGA進(jìn)行鍵盤掃描及顯示。一方面可以充分利用FPGAI/O資源豐富的優(yōu)勢,另一方面FPGA的穩(wěn)定性也能保證輸入顯示工作的準(zhǔn)確無誤。

(2)數(shù)碼管顯示

本模塊中的顯示采用動態(tài)掃描顯示。顯示位碼與寄存器acc中的數(shù)具有一一對應(yīng)關(guān)系,對應(yīng)關(guān)系由狀態(tài)掃描信號k來連接。信號k有5個狀態(tài),對應(yīng)5位顯示位碼。顯示部分的最后是7段譯碼,本系統(tǒng)只需顯示數(shù)據(jù),因此只對1O個數(shù)字進(jìn)行譯碼。

4.3.3 測頻模塊

為了保證測試的精度,一般對低頻信號采用測周期法,對高頻信號采用測頻法。本調(diào)諧系統(tǒng)所需測量的頻率范圍是:3.9MHz一26.1MHz,適合用測頻法,而且誤差不大。

根據(jù)系統(tǒng)的要求,測頻計需要對單位時間內(nèi)的信號脈沖進(jìn)行計數(shù),從而測量出信號的頻率。首先要產(chǎn)生一個計數(shù)允許信號,即時基信號,時基信號的寬度為單位時間,例如1s或lOOms。在時基信號有效的時間內(nèi)對被測信號計數(shù),即為信號頻率。測量過程結(jié)束,需要鎖存計數(shù)值或留出一段時間顯示測量值,下一次測量前,應(yīng)該對計數(shù)器清零。如圖5所示:

測頻計由控制器、分頻器、計數(shù)器、鎖存器4部分組成。控制器發(fā)出相應(yīng)的控制信號,完成計數(shù)值的鎖存和計數(shù)器的清零。分頻器將標(biāo)頻信號分成一系列較低頻率信號,其中一個作為測量的時基信號,該系統(tǒng)的分頻器由專門的分頻模塊完成。計數(shù)器的作用是對一個時基信號中的被測信號脈沖數(shù)進(jìn)行計數(shù),計數(shù)結(jié)果即為被測頻率對所選用時基的相對值。鎖存器用來鎖存計數(shù)結(jié)果,以便其它模塊調(diào)用。

為了便于處理,系統(tǒng)采用頻率為1Hz的信號作為時基信號。圖6為測頻計工作時的時序。其中testf為被測信號,clock_ls為時基信號,enable為計數(shù)使能信號,為高時有效,lock為鎖存信號,脈沖上升沿工作,clear為清零信號,為低時清零。

?

計數(shù)使能信號enable是時基信號的二分頻信號,在enable為高的半個周期里,剛好可以計完一個時基信號周期。lock信號是enable信號的取反,在上升沿將恰好計完的計數(shù)值鎖存。Clear信號是在clock_ ls信號和enable信號同時為低時置低,其它情況都為高。

通過功能仿真發(fā)現(xiàn),當(dāng)被測信號換頻時,會出現(xiàn)一個小于被測頻率的計數(shù)值,2個周期后計數(shù)值正常顯示,這與實際情況完全相同。這是因為在換頻時,計數(shù)使能信號已經(jīng)有效,這就會少計數(shù)一段時間,導(dǎo)致計數(shù)值小于實際值。當(dāng)正常計數(shù)后,計數(shù)值會因為小數(shù)問題有微小的波動,但很快趨于正常。見圖7

4.3.4 電機控制

通過單片機采集的調(diào)諧元件實際位置,與EEPROM中保存的此調(diào)諧元件的最佳工作位置(理論值)相比較。如果不等,按其差值的大小和極性來控制步進(jìn)電機的轉(zhuǎn)速和方向,直至二者的差值為零,即可達(dá)到調(diào)諧的目的。此模塊就是理論值和實際值相比較,輸出值用于控制電機的正、反轉(zhuǎn)及轉(zhuǎn)速的快慢。當(dāng)位置預(yù)置值大于實際位置值,控制電機正/反轉(zhuǎn)單元將發(fā)出指令控制電機正轉(zhuǎn);當(dāng)位置預(yù)置值小于實際位置值,控制電機正/反轉(zhuǎn)單元控制電機反轉(zhuǎn);當(dāng)位置預(yù)置值等于實際位置值,執(zhí)行電機不轉(zhuǎn);該模塊還可控制電機的轉(zhuǎn)速,理論值和實際值最高8位不等時,這表明兩者差值較大,控制電機以最快速度轉(zhuǎn)動;當(dāng)最高8位相等而次高4位(D4一D7)不等時,控制電機以次快速度轉(zhuǎn)動;當(dāng)高l2位相等而D2一D3不等時,控制電機以較慢速度轉(zhuǎn)動;當(dāng)最低2位(DO—D1)不等時,控制電機以最慢速度轉(zhuǎn)動。這樣設(shè)計可以使每次換頻時的調(diào)諧時間基本一致,而且保證了自動調(diào)諧的精度。

該模塊也是用VHDL語言描述實現(xiàn),語言描述可以很方便的調(diào)用開發(fā)軟件內(nèi)部IP資源。特別是在該模塊中有多層次比較及減法運算,用原理圖輸入將會很復(fù)雜,而且容易出錯。而VHDL語言支持大于、小于、不等等比較邏輯運算,應(yīng)用這些比較邏輯運算將很容易實現(xiàn)該模塊。

從仿真圖中可看出電機控制模塊符合設(shè)計要求,基本達(dá)到了控制目的。見圖8。

5 結(jié)束語

FPGA的集成度高、邏輯實現(xiàn)能力強、設(shè)計靈活性更好。利用VHDL語言進(jìn)行設(shè)計可以先裝配后編程,成為產(chǎn)品后還可反復(fù)編程,為系統(tǒng)升級提供便利。系統(tǒng)的設(shè)計早期就能查驗設(shè)計系統(tǒng)的功能可行性,隨時可對設(shè)計進(jìn)行仿真模擬。以達(dá)到降低開發(fā)成本的目的。

電子發(fā)燒友App

電子發(fā)燒友App

評論