摘要: 研究了嵌入式TCP/IP通信協(xié)議棧在Xilinx FPGA上的實(shí)現(xiàn),介紹了其軟硬件的系統(tǒng)組成和原理,提出一種實(shí)時(shí)操作系統(tǒng)上TCP/IP協(xié)議棧的高效工作模式,并在Virtex5 FPGA上移植成功。通過(guò)建立測(cè)試平臺(tái)進(jìn)行數(shù)據(jù)傳輸測(cè)試,證明其具有穩(wěn)定、高效的通信性能,為嵌入式設(shè)備開發(fā)提供了新的思路。

隨著電子信息技術(shù)的發(fā)展,網(wǎng)絡(luò)化日益普遍,以太網(wǎng)被廣泛應(yīng)用到各個(gè)領(lǐng)域,只要在設(shè)備上增加一個(gè)網(wǎng)絡(luò)接口并實(shí)現(xiàn)TCP/IP協(xié)議,就可以方便地接入到現(xiàn)有的網(wǎng)絡(luò)中,完成遠(yuǎn)程數(shù)據(jù)傳輸?shù)南嚓P(guān)功能。因此,嵌入式網(wǎng)絡(luò)技術(shù)一直是關(guān)注的焦點(diǎn),目前已經(jīng)廣泛應(yīng)用于通信、工業(yè)控制、消費(fèi)電子等各個(gè)領(lǐng)域。近年來(lái),隨著可編程邏輯器件的飛速發(fā)展,人們開始考慮將整個(gè)嵌入式系統(tǒng)集成到單片F(xiàn)PGA中實(shí)現(xiàn),其中也包括了以太網(wǎng)的嵌入式片上系統(tǒng)。本文從實(shí)際應(yīng)用出發(fā),以Xilinx FPGA的軟核CPU MicroBlaze IPCore搭建的片上系統(tǒng)(SystemonChip),構(gòu)建了嵌入式網(wǎng)絡(luò)硬件開發(fā)平臺(tái),實(shí)現(xiàn)了TCP/IP通信協(xié)議棧LwIP(Lightweight Internet Protocol)在實(shí)時(shí)操作系統(tǒng)Xilkernel上的移植。詳細(xì)介紹了其軟硬件的系統(tǒng)組成和原理,闡述了FPGA的片上系統(tǒng)配置,及其驅(qū)動(dòng)層和協(xié)議棧層軟件的結(jié)構(gòu),并給出部分關(guān)鍵源碼。

1 系統(tǒng)硬件平臺(tái)設(shè)計(jì)

Xilinx為嵌入式網(wǎng)絡(luò)通信解決方案提供了廣泛的組件和資源。Xilinx嵌入式解決方案的一個(gè)主要優(yōu)點(diǎn)是其處理器、IP內(nèi)核以及軟件組件的靈活性和可擴(kuò)展能力,其強(qiáng)大的靈活性允許用戶根據(jù)需要開啟或禁止處理器、IP內(nèi)核以及軟件平臺(tái)的選項(xiàng)和高級(jí)功能,并且可以對(duì)許多獨(dú)立參數(shù)進(jìn)行精細(xì)調(diào)整,直到在軟件級(jí)滿足應(yīng)用要求。

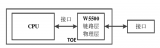

系統(tǒng)采用Xilinx公司的FPGA芯片XC5VFX70T為硬件設(shè)計(jì)平臺(tái),以MicroBlaze軟核作為中央處理器,以VHDL硬件描述語(yǔ)言實(shí)現(xiàn)協(xié)處理功能模塊,以片上總線連接MicroBlaze處理器和外圍設(shè)備(IP)來(lái)搭建嵌入式片上系統(tǒng)。

Xilinx以IBM CoreConnect總線通信鏈作為嵌入式處理器的片上總線,提供了豐富的接口資源,主要有PLB ( Processor Local Bus,處理器本地總線)接口、高速的LMB(Local Memory Bus,本地存儲(chǔ)器總線)接口、FSL(Fast Simplex Link,快速單連接)主從設(shè)備接口、XCL(Xilinx Cache Link,Xilinx緩存鏈路)接口。PLB總線可將外設(shè)IP核連接到MicroBlaze系統(tǒng)中,常用在速度要求不高的場(chǎng)合;LMB專門用于實(shí)現(xiàn)對(duì)片上塊RAM的高速訪問(wèn);XCL則用于實(shí)現(xiàn)對(duì)片外存儲(chǔ)器的高速訪問(wèn)。FSL是MicroBlaze處理器特有的一個(gè)基于FIFO的單向鏈路,可實(shí)現(xiàn)用戶自定義IP核與MicroBlaze內(nèi)部通用寄存器的點(diǎn)對(duì)點(diǎn)直接相連,一般用在傳輸速度要求較高的場(chǎng)合。

已實(shí)現(xiàn)的系統(tǒng)由MicroBlaze處理器、ILMB總線、DLMB總線、Block RAM、DDR SDRAM、10 /100/1000 Soft TEMAC、GPIO接口、UART16550串口、PLB TIMER定時(shí)器,以及基于PLB總線技術(shù)的DDC(數(shù)字下變頻)自定義IPCore和基于FSL總線技術(shù)的FFT(快速傅里葉變換)自定義IPCore組成。設(shè)計(jì)的系統(tǒng)架構(gòu)如圖1所示,整個(gè)系統(tǒng)在Xilinx的EDK開發(fā)工具中構(gòu)建,具有完全的可編程特性,可根據(jù)不同任務(wù)需求來(lái)更改相關(guān)的配置參數(shù)。

圖1 系統(tǒng)架構(gòu)圖

2 系統(tǒng)軟件平臺(tái)設(shè)計(jì)

2.1 LwIP協(xié)議棧

LwIP是一個(gè)開源TCP/IP協(xié)議棧,在實(shí)現(xiàn)TCP/IP協(xié)議棧主要功能的基礎(chǔ)上減少了對(duì)RAM的占用,一般只需要幾十KB的RAM和40 KB左右的ROM就可以運(yùn)行,因此非常適合在硬件配置較低的嵌入式系統(tǒng)中使用。EDK為L(zhǎng)wIP庫(kù)提供了良好的接口,并為Xilinx公司TEMAC IP核提供了適配器,在EDK工程中方便地應(yīng)用LwIP協(xié)議棧實(shí)現(xiàn)網(wǎng)絡(luò)功能。LwIP具有如下特點(diǎn):

① 支持多網(wǎng)絡(luò)接口下的IP轉(zhuǎn)發(fā);

② 支持ICMP協(xié)議;

③ 包括實(shí)驗(yàn)性擴(kuò)展的UDP(用戶數(shù)據(jù)報(bào)協(xié)議);

④ 包括阻塞控制、RTT估算以及快速恢復(fù)和轉(zhuǎn)發(fā)的TCP(傳輸控制協(xié)議);

⑤ 提供專門的內(nèi)部回調(diào)接口(Raw API)用于提高應(yīng)用程序性能;

⑥ 可選擇的Berkeley接口API(多線程情況下);

⑦ 在最新的版本中支持ppp;

⑧ 新版本中增加了的IP fragment的支持;

⑨ 支持DHCP協(xié)議,動(dòng)態(tài)分配IP地址。

在Xilinx的嵌入式開發(fā)工具EDK中,LwIP的版本為lwip130,即LwIP的v1.3.0版本。LwIP庫(kù)提供了RAW模式和Socket模式兩類API函數(shù),前者面向高性能,后者面向通用性,提供一組標(biāo)準(zhǔn)的Socket API接口函數(shù)。

2.2 Xilkernel實(shí)時(shí)操作系統(tǒng)

Xilkernel是Xilinx公司提供的用于EDK系統(tǒng)的小型、模塊化的嵌入式實(shí)時(shí)操作系統(tǒng),支持MicroBlaze、PowerPC405以及PowerPC440處理器。Xilkernel是一種專用的嵌入式操作系統(tǒng),內(nèi)核完整,占用CPU資源較少,運(yùn)行速度快,內(nèi)核響應(yīng)時(shí)間間隔最短可設(shè)置為1 ms,且與EDK生成的硬件系統(tǒng)緊密結(jié)合,具有可定制的特點(diǎn),支持可移植操作系統(tǒng)接口(POSIX),是中小型設(shè)計(jì)的理想操作系統(tǒng)。其內(nèi)部結(jié)構(gòu)如圖2所示。

圖2 Xilkernel內(nèi)部結(jié)構(gòu)示意圖

Xilkernel本身不帶有文件處理系統(tǒng)和TCP/IP協(xié)議棧,但與LwIP庫(kù)具有良好的接口,且支持LibXil MFS文件系統(tǒng)庫(kù),因此,也可形成較為復(fù)雜的嵌入式系統(tǒng)。其具有如下特點(diǎn):

① 內(nèi)核配置功能都已集成到EDK工具中,使用簡(jiǎn)單、方便;

② 內(nèi)核啟動(dòng)時(shí),靜態(tài)創(chuàng)建線程,而動(dòng)態(tài)分配內(nèi)存;

③ 可加載或卸載不同的功能模塊來(lái)實(shí)現(xiàn)內(nèi)核的擴(kuò)展性;

④ 提供了一套符合POSIX的API用戶程序接口函數(shù);

⑤ 所有系統(tǒng)調(diào)用函數(shù)帶有參數(shù)合法性檢查保護(hù),并返回符合POSIX的錯(cuò)誤代碼。

3 TCP/IP通信協(xié)議實(shí)現(xiàn)及測(cè)試

3.1 Socket應(yīng)用程序開發(fā)

LwIP Socket API是建立在Xilkernel操作系統(tǒng)多線程任務(wù)基礎(chǔ)上的,與BSD標(biāo)準(zhǔn)的Socket API非常相似,具有開發(fā)難度較小、便于用戶調(diào)用的特點(diǎn),可滿足一般網(wǎng)絡(luò)應(yīng)用的要求。使用LwIP的Socket模式,首先要在初始化線程中調(diào)用lwip_init()函數(shù)對(duì)LwIP協(xié)議棧進(jìn)行初始化,再使用sys_thread_new()函數(shù)來(lái)產(chǎn)生一個(gè)新的線程,即進(jìn)入主線程。在主線程中首先通過(guò)xemac_add()函數(shù)來(lái)添加網(wǎng)絡(luò)接口,然后為xemacif_input_thread()函數(shù)單獨(dú)開啟一個(gè)線程,將從中斷響應(yīng)過(guò)程中接收到的數(shù)據(jù)包移植到LwIP的xemacif_input_thread()函數(shù)運(yùn)行的線程中,該線程在LwIP數(shù)據(jù)包到達(dá)時(shí)發(fā)出通知,并通過(guò)接收中斷句柄將數(shù)據(jù)存在緩沖中。以下為主線程中添加的網(wǎng)絡(luò)接口程序代碼:

……

struct ip_addr ipaddr, netmask, gw;

struct netif *netif;

netif = &server_netif;

/*初始化IP地址*/

IP4_ADDR(&gw, 000,000,000,000); //設(shè)置網(wǎng)關(guān)

IP4_ADDR(&ipaddr, 192,168,169,110);//設(shè)置IP

IP4_ADDR(&netmask,255,255,255,000); //設(shè)置子網(wǎng)IP

/*加入網(wǎng)絡(luò)接口,并將其設(shè)為默認(rèn)接口*/

if(!xemac_add(netif,&ipaddr,&netmask,&gw,fullmac,XPAR_LLTEMAC_0_BASEADDR)){

xil_printf("Error adding N/W interface\n\r");

return;

}

netif_set_default(netif);

/*啟用網(wǎng)絡(luò)接口*/

netif_set_up(netif);

/*啟用數(shù)據(jù)包接收線程*/

sys_thread_new("xemacif_input_thread",xemacif_input_thread,netif,THREAD_STACKSIZE,MY_THREAD_PRIO);

/*建立Socket接口*/

sock = socket(AF_INET,SOCK_STREAM,0);

addr.sin_family = AF_INET;

addr.sin_port = htons(6000);

addr.sin_addr.s_addr = INADDR_ANY;

bind(sock,(struct sockaddr *)&addr,sizeof(addr));

listen(sock,15);

while(1){

s = accept(sock,(struct sockaddr*)&rem,&len);

……

}

通過(guò)上述步驟后,就可使用Socket編程建立網(wǎng)絡(luò)服務(wù)器。

3.2 網(wǎng)絡(luò)數(shù)據(jù)傳輸性能測(cè)試

使用RJ45交叉以太網(wǎng)線將Xilinx XC5VFX70T開發(fā)板和PC機(jī)直連。PC機(jī)作為TCP/IP的客戶端,Xilinx XC5VFX70T開發(fā)板作為TCP/IP的服務(wù)端,客戶端經(jīng)連接響應(yīng)后,高速向服務(wù)器端連續(xù)發(fā)TCP包。服務(wù)端接收到數(shù)據(jù)后計(jì)算接收到的數(shù)據(jù)總量,不做其他處理。使用iperf網(wǎng)絡(luò)測(cè)試軟件測(cè)試系統(tǒng)網(wǎng)絡(luò)直接發(fā)送數(shù)據(jù)的性能。

Socket模式下網(wǎng)絡(luò)發(fā)送速率為27.2 Mb/s,其iperf服務(wù)器端顯示結(jié)果如圖3所示。

圖3 LwIP協(xié)議棧發(fā)送數(shù)據(jù)速率測(cè)試結(jié)果

為了檢測(cè)本文開發(fā)的應(yīng)用程序中數(shù)據(jù)發(fā)送的速率及其準(zhǔn)確度,在計(jì)算機(jī)端使用LabView軟件開發(fā)網(wǎng)絡(luò)服務(wù)客戶端接收本系統(tǒng)的數(shù)據(jù),并將數(shù)據(jù)記錄為DAT文件,使用多特NetPerSec網(wǎng)絡(luò)測(cè)試軟件測(cè)試網(wǎng)絡(luò)的當(dāng)前速率和平均速率。在寫數(shù)據(jù)速率為24.1 Mb/s時(shí),NetPerSec顯示網(wǎng)絡(luò)接收平均速率為24.8 Mb/s;記錄的DAT文件顯示圖形中無(wú)跳變點(diǎn),數(shù)據(jù)無(wú)丟失,NetPerSec截圖及DAT文件顯示圖形如圖4所示。

?

圖4 NetPerSec網(wǎng)絡(luò)數(shù)據(jù)流量統(tǒng)計(jì)及線性數(shù)據(jù)正確性測(cè)試

寫數(shù)據(jù)速率為24.3 Mb/s時(shí),NetPerSec顯示網(wǎng)絡(luò)接收平均速率為25.4 Mb/s;記錄的DAT數(shù)據(jù)顯示圖形中間出現(xiàn)跳變點(diǎn),說(shuō)明有數(shù)據(jù)包丟失,NetPerSec截圖及DAT數(shù)據(jù)顯示圖形如圖5所示。

圖5 NetPerSec網(wǎng)絡(luò)數(shù)據(jù)流量統(tǒng)計(jì)及數(shù)據(jù)丟包測(cè)試

測(cè)試結(jié)果表明,使用LwIP協(xié)議棧Socket模式進(jìn)行網(wǎng)絡(luò)數(shù)據(jù)傳輸,可實(shí)現(xiàn)網(wǎng)速為24.8 Mb/s、接收偵察信號(hào)帶寬為750 kHz的穩(wěn)定數(shù)據(jù)傳輸。

結(jié)語(yǔ)

本文研究了TCP/IP通信協(xié)議在Xilinx公司FPGA上的實(shí)現(xiàn),介紹了其軟硬件的系統(tǒng)組成及原理。其功能可根據(jù)需要進(jìn)行定制,不但引入了軟核處理器和嵌入式操作系統(tǒng)Xilkernel,而且應(yīng)用了LwIP TCP/IP協(xié)議棧,同時(shí)使用了大量的IP核,系統(tǒng)構(gòu)建非常靈活。其軟硬件部分的設(shè)計(jì)采用分離的設(shè)計(jì)架構(gòu),使得整個(gè)系統(tǒng)修改和重構(gòu)更加方便,真正實(shí)現(xiàn)了嵌入式片上系統(tǒng)。

參考文獻(xiàn)

[1] Xilinx Inc.ML402 User Guider,2005.

[2] Xilinx Inc.MicroBlaze Processor Reference Guide,2008.

[3] Xilinx Inc.OS and Libraries Document Collection,2008.

[4] Xilinx Inc.UG650:LwIP 1.3.0 Liabrary(v1.00.b),2009.

[5] 田耘,徐文波,胡彬,等.Xilinx ISE Design Suite 10.x FPGA開發(fā)指南[M].北京:人民郵電出版社,2008.

[6] 鮑興川.TCP/IP通信技術(shù)在Xilinx FPGA上的實(shí)現(xiàn)[J].水利水文自動(dòng)化,2007,6(2):2022.

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論