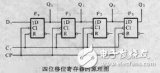

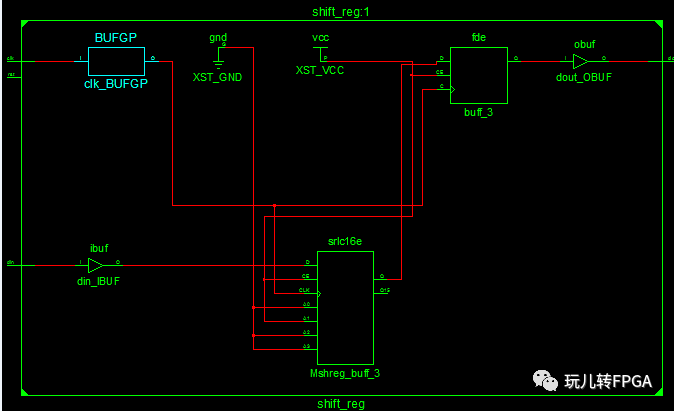

可以定義移位長度的移位寄存器。

就是用一個lut可以實現16位的移位寄存器。

SRL16 的是 16bit移位寄存器查找表 // 16-Bit Shift Register Look-Up-Table (LUT)

在一個LUT中可以實現16個FF移位的功能!

SSRL16 SRL16_inst (

.Q(Q), // SRL data output

.A0(A0), // Select[0] input

.A1(A1), // Select[1] input

.A2(A2), // Select[2] input

.A3(A3), // Select[3] input

.CLK(CLK), // Clock input

.D(D) // SRL data input

);

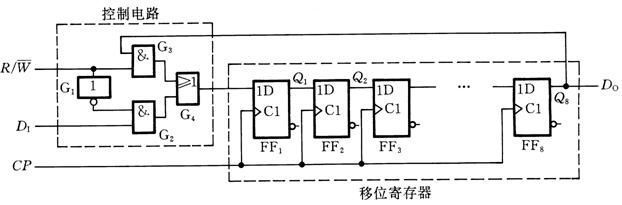

Xilinx 官網的說明——原理

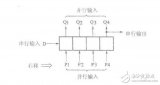

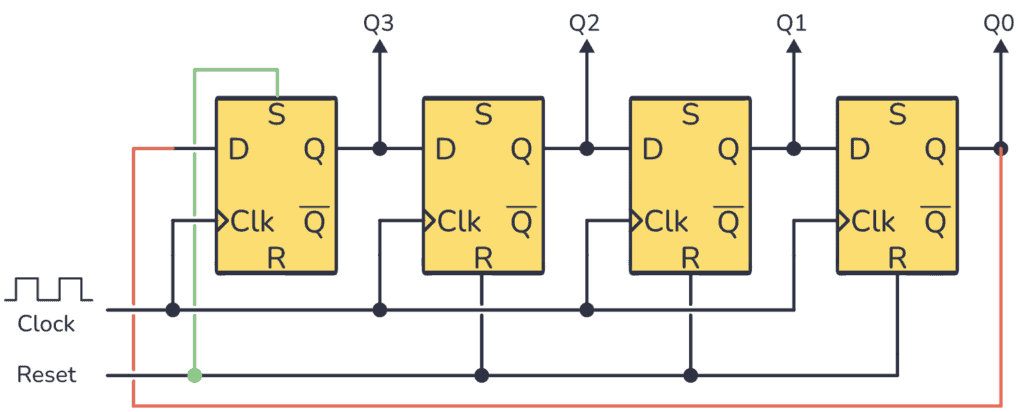

SRL16 is a shift register look up table (LUT). The inputs A3, A2, A1, and A0 select the output length of the shift register. The shift register may be of a fixed, static length or it may be dynamically adjusted.

The shift register LUT contents are initialized by assigning a four-digit hexadecimal number to an INIT attribute. The first, or the left-most, hexadecimal digit is the most significant bit. If an INIT value is not specified, it defaults to a value of four zeros (0000) so that the shift register LUT is cleared during configuration.

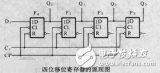

The data (D) is loaded into the first bit of the shift register during the Low-to-High clock (CLK) transition. During subsequent Low-to-High clock transitions data is shifted to the next highest bit position as new data is loaded. The data appears on the Q output when the shift register length determined by the address inputs is reached.

這里說了幾點,

- 移位寄存器的初始值可以用INIT屬性初始化;

- 移位寄存器的長度由地址線的取值決定;

- 移位數據從D端輸入,Q端輸出

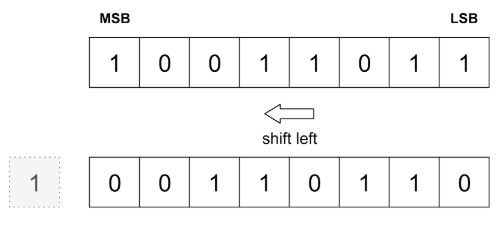

- 先移入的數據是MSB

Xilinx 官網的說明——Static Length Mode

To get a fixed length shift register, drive the A3 through A0 inputs with static values. The length of the shift register can vary from 1 bit to 16 bits as determined from the following formula:

Length = (8*A3) +(4*A2) + (2*A1) + A0 +1

If A3, A2, A1, and A0 are all zeros (0000), the shift register is one bit long. If they are all ones (1111), it is 16 bits long.

Xilinx 官網的說明——Dynamic Length Mode

The length of the shift register can be changed dynamically by changing the values driving the A3 through A0 inputs. For example, if A2, A1, and A0 are all ones (111) and A3 toggles between a one (1) and a zero (0), the length of the shift register changes from 16 bits to 8 bits.

Internally, the length of the shift register is always 16 bits and the input lines A3 through A0 select which of the 16 bits reach the output.

Inputs Output

Am CLK D Q

Am X X Q(Am)

Am ↑ D Q(Am-1)

m= 0, 1, 2, 3

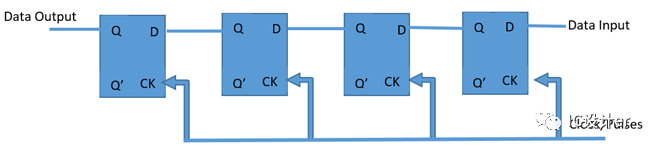

這里提示了幾個要點:

- 移位寄存器是可變長度的

- 長度的改變由地址線來指定

- 內部的寄存器長度是不變的,只是截取的長度變了

- 數據先移入到A0,然后到A1,以此類推,最后從指定長度的Am-1處輸出,比如A=8,則數據從地址0輸入,從地址7輸出,這樣有效的移位長度就為8。

Xilinx 官網的說明——VHDL例化實例

-- SRL16: 16-bit shift register LUT operating on posedge of clock

-- All FPGAs

-- Xilinx HDL Libraries Guide version 7.1i

SRL16_inst : SRL16

-- The following generic declaration is only necessary if you wish to

-- change the initial contents of the SRL to anything other than all

-- zero's.

generic map (

INIT => X"0000")

port map (

Q => Q, -- SRL data output

A0 => A0, -- Select[0] input

A1 => A1, -- Select[1] input

A2 => A2, -- Select[2] input

A3 => A3, -- Select[3] input

CLK => CLK, -- Clock input

D => D -- SRL data input

);

-- End of SRL16_inst instantiation

復制代碼

Xilinx 官網的說明——Verilog例化實例

-- SRL16: 16-bit shift register LUT operating on posedge of clock

- All FPGAs

-- Xilinx HDL Libraries Guide version 7.1i

SSRL16 SRL16_inst (

.Q(Q), // SRL data output

.A0(A0), // Select[0] input

.A1(A1), // Select[1] input

.A2(A2), // Select[2] input

.A3(A3), // Select[3] input

.CLK(CLK), // Clock input

.D(D) // SRL data input

);

// The following defparam declaration is only necessary if you wish to

// change the initial contents of the SRL to anything other than all

// zero's. If the instance name to the SRL is changed, that change

// needs to be reflected in the defparam statements.

defparam SRL16_inst.INIT = 16'h0000;

// End of SRL16_inst instantiation

電子發燒友App

電子發燒友App

評論