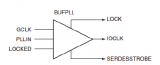

5.1.6 SelectIO模塊

Virtex-6每個I/O片(I/O Tile)包含兩個IOB、兩個ILOGIC、兩個OLOGIC 和兩個IODELAY,如圖5-24 所示。

?

圖5-24 I/O 片結構圖

本小節就以下幾個方面介紹Virtex-6 的SelectIO 資源。

(1) SelectIO 的電氣特性。

(2) SelectIO 的邏輯資源——ILOGIC 資源和OLOGIC 資源。

(3) SelectIO 的高級邏輯資源——ISERDES 資源、OSERDES 資源和Bitslip。

一、 SelectIO IO 的電氣特性

所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驅動器與接收器,支持非常廣泛的接口標準。強大的功能SelectIO 包括輸出強度和斜率的可編程控制以及使用數控阻抗(DCI)的片上終端。

IOB 包含輸入、輸出和三態SelectIO 驅動器。支持單端I/O 標準(LVCMOS、HSTL、SSTL)和差分I/O 標準(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。

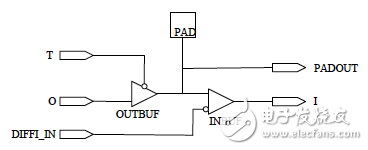

IOB、引腳及內部邏輯的連接如圖5-25 所示。

圖5-25 IOB、引腳及內部邏輯連接圖

IOB 直接連接ILOGIC/OLOGIC 對,該邏輯對包含輸入和輸出邏輯資源,可實現數據和三態控制。ILOGIC和OLOGIC可分別配置為ISERDES和OSERDES。

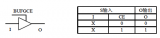

Xilinx軟件庫提供了大量與I/O相關的原語,在例化這些原語時,可以指定I/O標準。與單端I/O相關的原語包括IBUF(輸入緩沖器)、IBUFG(時鐘輸入緩沖器)、OBUF(輸出緩沖器)、OBUFT(三態輸出緩沖器)和IOBUF(輸入/輸出緩沖器)。與差分I/O相關的原語包括IBUFDS(輸入緩沖器)、IBUFGDS(時鐘輸入緩沖器)、OBUFDS(輸出緩沖器)、OBUFTDS(三態輸出緩沖器)、IOBUFDS(輸入/輸出緩沖器)、IBUFDS_DIFF_OUT(輸入緩沖器)和IOBUFDS_DIFF_OUT(輸入/輸出緩沖器)。

二、 SelectIO的邏輯資源

SelectIO的邏輯資源主要是指ILOGIC和OLOGIC資源,它們完成了FPGA引腳到內部邏輯的連接功能,包括組合輸入/輸出、三態輸出控制、寄存器輸入/輸出、寄存器三態輸出控制、DDR輸入/輸出、DDR輸出三態控制、IODELAYE1高分辨率可調整延遲單元及其控制模塊。

下面簡要介紹ILOGIC和OLOGIC功能。

(1) ILOGIC。

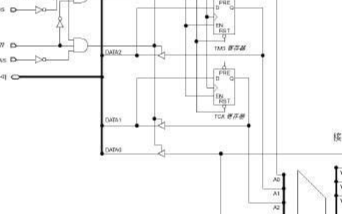

圖5-26 ILOGIC內部邏輯

ILOGIC的內部邏輯如圖5-26所示,可以實現的操作包括:異步/組合邏輯、DDR模式(OPPOSITE_EDGE、SAME_EDGE或SAME_EDGE_PIPELINED)、電平敏感型鎖存器和邊沿觸發D型觸發器。

異步/組合邏輯。

用來創建輸入驅動器與FPGA內部資源之間的直接連接。當輸入數據與FPGA內部邏輯之間存在直接(非寄存)連接,或者當“將I/O寄存器/鎖存器合并到IOB中”的設置為OFF時,此通路被自動使用。

輸入DDR(IDDR)。

Virtex-6器件的ILOGIC中有專用寄存器來實現輸入雙倍數據速率(DDR)。可以通過例化IDDR的原語來使用此功能。IDDR只有一個時鐘輸入,下降沿數據由輸入時鐘的反相版本(在ILOGIC內完成反相)進行時鐘控制。所有輸入I/O模塊的時鐘均為完全多路復用,即ILOGIC或OLOGIC模塊之間不共用時鐘。IDDR支持以下三種操作模式:

OPPOSITE_EDGE模式、SAME_EDGE模式和SAME_EDGE_PIPELINED模式。

SAME_EDGE和SAME_EDGE_PIPELINED與Virtex-5一樣。這些模式允許設計人員在ILOGIC模塊內部將下降沿數據轉移到上升沿時鐘域,以節省CLB和時鐘資源并提高性能。這些模式是用DDR_CLK_EDGE屬性實現的。

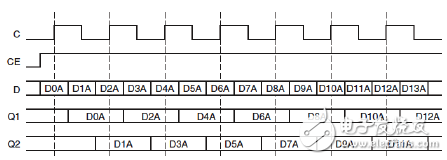

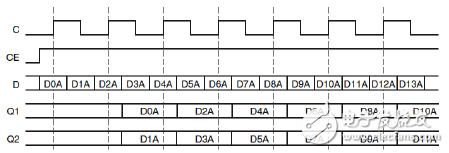

各模式下時序圖請參考圖5-27、圖5-28和圖5-29。

圖5-27 OPPOSITE_EDGE模式下的輸入雙倍數據速率

圖5-28 SAME_EDGE模式下的輸入雙倍數據速率

圖5-29 SAME_EDGE_PIPELINED模式下的輸入雙倍數據速率

可編程絕對延遲單元IODELAYE1。

每個I/O模塊包含一個可編程絕對延遲單元,稱為IODELAYE1。IODELAYE1可以連接到ILOGIC/ISERDES或OLOGIC/OSERDES模塊,也可同時連接到這兩個模塊。

IODELAYE1是具有32個tap的環繞延遲單元,具有標定的tap分辨率。請參考附帶光盤中的《Virtex-6 IO用戶手冊》。IODELAYE1可用于組合輸入通路、寄存輸入通路、組合輸出通路或寄存輸出通路,還可以在內部資源中直接使用。IODELAYE1允許各輸入信號有獨立的延遲。通過在《Virtex-6用戶手冊》中規定的范圍內選擇IDELAYCTRL參考時鐘,可以改變tap延遲分辨率。IODELAYE1資源可用作IDELAY、ODELAY或組合延遲。

.IDELAYE1允許各輸入信號有獨立的延遲。延遲單元可以被校驗到一個絕對延時固定值(TIDELAYRESOLUTION),這個值不隨工藝,電壓和溫度的變化而改變。

IODELAYE1有四種操作模式:分別是零保持時間延遲模式(IDELAY_TYPE=DEFAULT)、固定延遲模式(IDELAY_TYPE=FIXED)、可變延遲模式(IDELAY_TYPE=VARIABLE)和可裝載的可變延時模式(IDELAY_TYPE=VAR_LOADABLE)。零保持時間延遲模式允許向后兼容,以使用Virtex-5器件中的零保持時間延遲功能的設計,在這種模式下使用時,不需要例化IDELAYCTRL的原語。在固定延遲模式,延遲值由屬性IDELAY_VALUE確定的tap數決定,此值配置后不可更改,此模式必須例化IDELAYCTRL的原語。在可變延遲模式,配置后通過控制信號CE和INC來改變延遲值,此模式必須例化IDELAYCTRL的原語。在可裝載的可變延時模式下,IDELAY TAP可以通過FPGA邏輯相連的5位CNTVALUEIN<4:0>裝載。當配置為此模式時,也必須例化IDELAYCTRL原語。

IDELAYCTRL延時控制模塊。

當IDELAYE1或ISERDES的原語中的IOBDELAY_TYPE屬性設置為FIXED、VARIABLE或者VAR_LOADABLE時,都必須例化IDELAYCTRL。IDELAYCTRL模塊連續校驗IODELAYE1的延時環節,以減少工藝、電壓和溫度的影響。

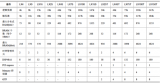

(2) OLOGIC資源。

OLOGIC由兩個主要模塊組成,分別是輸出數據通路和三態控制通路。這兩個模塊具有共同的時鐘(CLK),但具有不同的使能信號OCE和TCE。

輸出通路和三態通路可獨立配置為邊沿觸發的D型觸發器、電平敏感鎖存器、異步/組合邏輯或者DDR模式。

?

組合數據輸出和三態控制路徑。

組合輸出通路用來實現從FPGA內部邏輯到輸出驅動器或輸出驅動器控制端的直接連接。當FPGA的內部邏輯與輸出數據或三態控制之間存在直接(不寄存)連接,或者當“將I/O寄存器/鎖存器合并到IOB中”的設置為OFF時,此路徑被使用。

?

輸出DDR(ODDR)。

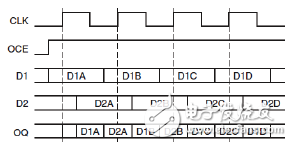

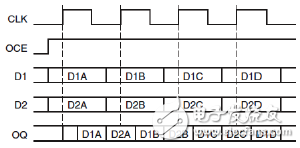

Virtex-6器件的OLOGIC中具有專用寄存器,用來實現DDR功能。要使用此功能,只需要例化ODDR。ODDR只有一個時鐘輸入,下降沿數據由輸入時鐘的反相時鐘控制。ODDR支持兩種操作模式:OPPOSITE_EDGE模式和SAME_EDGE模式。SAME_EDGE模式允許在ODDR時鐘的上升沿將兩個數據送至ODDR,以節省CLB和時鐘資源并提高性能。OPPOSITE_EDGE模式使用時鐘的兩個沿以兩倍吞吐量從FPGA內部采集數據,兩個輸出都送至IOB的數據輸入或三態控制輸入。圖5-30所示為使用OPPPOSITE_EDGE模式時輸出DDR的時序圖。圖5-31所示為使用SAME_EDGE模式時輸出DDR的時序圖。

?

圖5-30 OPPPOSITE_EDGE模式時輸出DDR

圖5-31 SAME_EDGE模式時輸出DDR

輸出ODDR可以將時鐘的一個副本傳送到輸出。將ODDR原語的D1固定為High,D2固定為Low,時鐘與數據ODDR的時鐘一樣。這個方案可以確保輸出數據與輸出時鐘延時的一致性。

三、 SelectIO的高級特性

除了SelectIO的電器特性和專用于收發SDR或DDR數據的寄存器結構之外,Virtex-6還提供了更高級的邏輯特性。其中包含串并轉換器ISERDES、并串轉換器OSERDES和Bitslip。

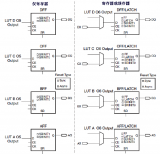

(1) ISERDES。

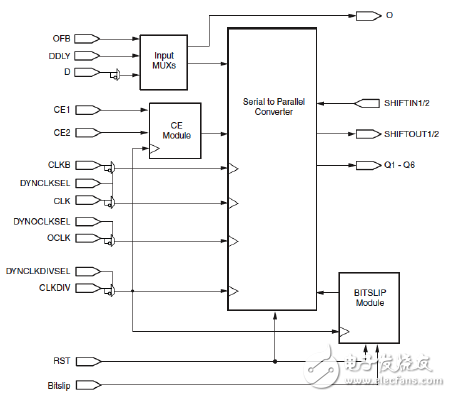

Virtex-6 ISERDES是專用的串并轉換器,具有專門實現高速源同步應用的時鐘控制與邏輯功能。圖5-32為ISERDES的結構圖,其中包括串并轉換器(ISERDES)、Bitslip子模塊,以及對選通存儲器接口的支持,如網絡接口、DDR3接口和QDR接口。

圖5-32 ISERDES結構圖

輸入串并轉換器。

ISERDES解串器可以實現高速數據傳輸,不要求FPGA內部資源與輸入數據頻率匹配。此轉換器支持SDR和DDR。在SDR模式下,串并轉換器可以實現2、3、4、5、6、7或8bit寬的并行字。在DDR模式下,串并轉換器可以實現4、6、8或10位寬的并行字。

ISERDES的原語ISERDES1如圖5-33所示。

圖5-33 ISERDES的原語ISERDES1

Bitslip模塊。

Virtex-6器件中的所有ISERDES模塊都包含一個Bitslip子模塊。這個子模塊可在源同步網絡型應用中實現字對齊。Bitslip對ISERDES模塊中的并行數據重新排序,以便將解串器所接收重復串行模式的每種組合都送至FPGA內部邏輯。這種重復串行模式通常稱為培訓模式(許多網絡和電信標準都支持培訓模式)。

Bitslip操作通過將ISERDES模塊的Bitslip引腳置為有效,可以在并行側對輸入串行數據流重新排序。此操作重復進行,直到找到訓練模型。圖5-34 中所示為SDR 和DDR 模式下Bitslip 操作的效果。為了便于說明,采用了八位數據寬度。Bitslip 操作與CLKDIV 同步。在SDR 模式下,每次Bitslip 操作使輸出模式左移一位。在DDR 模式下,每次Bitslip

操作使輸出模式在右移一位和左移三位之間交替變化。在此示例中,輸出模式在第八次Bitslip 操作時還原到初始模式。這里假定串行數據是八位重復模式。

?

圖5-34 Bitslip 操作

使用Bitslip 子模塊的指導原則如下。

只有在NETWORKING 模式下,Bitslip 才有效。其他模式下,不支持Bitslip。

要啟動Bitslip 操作,BITSLIP 端口置為High 有效的時間必須持續在一個CLKDIV 周期。在SDR 模式下,Bitslip 的置位時間不能長達兩個連續的CLKDIV 周期;在兩次Bitslip有效置位之間,Bitslip 的無效時間至少有一個CLKDIV 周期。在SDR 和DDR 兩種模式下,從ISERDES 采樣到Bitslip 有效的宣稱輸入到“bit-slipped”ISERDES 的輸出Q1-Q6 被

采樣到FPGA 內部邏輯,總延遲是兩個CLKDIV 周期。

對選通存儲器接口的支持。

ISERDES 包含專用電路(包括OCLK 輸入引腳),可以完全在ISERDES 模塊內部處理選通門到FPGA 跨時鐘域的功能。該功能可以極大方便選通存儲器的支持,如網絡接口、DDR3 接口和QDR 接口。

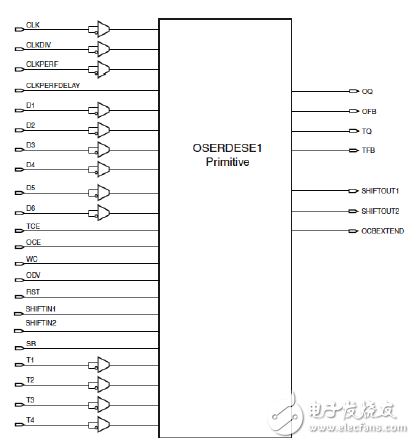

(2) 輸出并串轉換器(OSERDES)。

Virtex-6 OSERDES 是專用的并串轉換器,用來實現高速源同步接口設計。每個OSERDES 模塊包括一個數據串行器和一個實現三態控制的串行器。此轉換器支持SDR 和DDR。數據串行化可達6:1(如果使用“OSERDES 寬度擴展”可達10:1)。三態串行化可達4:1。OSERDES 的框圖如圖5-35 所示。

數據并串轉換器。

一個OSERDES 模塊中的數據并串轉換器接收來自內部邏輯的二到六位并行數據,將數據串行化,然后通過OQ 輸出將數據送至IOB。并行數據串行化是按照從數據輸入引腳的最低位到最高的順序進行的(即D1 輸入引腳上的數據傳輸到OQ 引腳的首位)。

OSERDES 使用CLK 和CLKDIV 兩個時鐘進行數據速率轉換。CLK 是高速串行時鐘;CLKDIV 是分頻并行時鐘。

?

圖5-35 OSERDES的結構框圖

三態并串轉換。

除了數據的并串轉換,OSERDES模塊還包含一個三態并串轉換器,三態并串轉換器最多只能串行化四位并行三態信號。三態轉換器不能級聯。

OSERDES的原語如圖5-36所示。

圖5-36 OSERDES的原語

電子發燒友App

電子發燒友App

評論