ETD第14期:SDR源同步接口時序約束方法

- FPGA(591969)

- 接口設計(29663)

- ETD(16852)

相關推薦

工程師談FPGA時序約束七步法

時序例外約束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但這還不是最完整的時序約束。

2016-05-29 23:25:10 1064

1064

1064

1064FPGA案例解析:針對源同步的時序約束

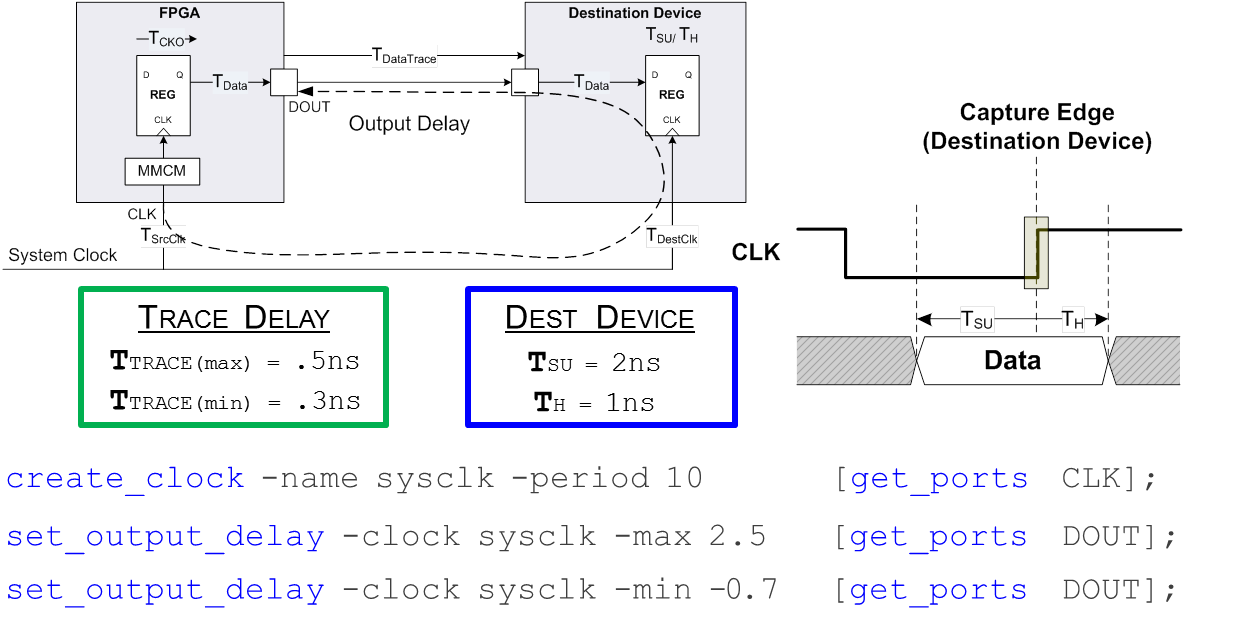

是指FPGA與外部器件共用外部時鐘;源同步(SDR,DDR)即時鐘與數據一起從上游器件發送過來的情況。在設計當中,我們遇到的絕大部分都是針對源同步的時序約束問題。所以下文講述的主要是針對源同步的時序約束。 根據網絡上收集的資料以及結合自

2020-11-20 14:44:52 6859

6859

6859

6859

VIVADO時序約束及STA基礎

時序約束的目的就是告訴工具當前的時序狀態,以讓工具盡量優化時序并給出詳細的分析報告。一般在行為仿真后、綜合前即創建基本的時序約束。Vivado使用SDC基礎上的XDC腳本以文本形式約束。以下討論如何進行最基本時序約束相關腳本。

2022-03-11 14:39:10 8731

8731

8731

8731FPGA的IO口時序約束分析

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382

1382

1382FPGA主時鐘約束詳解 Vivado添加時序約束方法

在FPGA設計中,時序約束的設置對于電路性能和可靠性都至關重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的基礎知識。

2023-06-06 18:27:13 6213

6213

6213

6213

FPGA時序約束之衍生時鐘約束和時鐘分組約束

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1230

1230

1230

1230FPGA時序約束之偽路徑和多周期路徑

前面幾篇FPGA時序約束進階篇,介紹了常用主時鐘約束、衍生時鐘約束、時鐘分組約束的設置,接下來介紹一下常用的另外兩個時序約束語法“偽路徑”和“多周期路徑”。

2023-06-12 17:33:53 868

868

868

868同步電路設計中靜態時序分析的時序約束和時序路徑

同步電路設計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最壞情況下滿足時序要求,我們需要進行靜態時序分析,即不依賴于測試向量和動態仿真,而只根據每個邏輯門的最大延遲來檢查所有可能的時序違規路徑。

2023-06-28 09:35:37 490

490

490

490

FPGA設計大家談:讓時序約束更簡單—ETD第14期

1月10日,由電子發燒友網主辦的FPGA技術沙龍順利開展。本次沙龍邀請的是Altera代理商駿龍科技FAE張亞峰,嘉賓在沙龍現場為聽眾詳解了“SDR源同步接口時序約束”。聽眾均來自車載系統、測試儀

2015-01-14 16:34:26 4704

4704

4704

4704ETD第12期:科技與體育的碰撞——智能羽毛球拍[深圳市]

。 但是目前業內企業關注的焦點似乎都在智能家居以及可穿戴設備上,做智能體育硬件的廠商是寥寥無幾。從這也可看出智能體育硬件存在極大的發展空間,而科技體育是未來發展的必然趨勢,此次ETD第12期技術沙龍有幸

2014-11-05 11:11:20

ETD第13期安防與智能家居技術沙龍PPT下載!

智能家居已然是大勢所趨,業內企業如何在風口浪尖上贏得市場是大家最關心的。不難發現創新的產品設計是獲取用戶青睞的前提。對此,電子發燒友網ETD第13期技術沙龍邀請到安銳通科技秦總和科地通信龔總為大家

2014-12-09 10:51:21

ETD第14期SDR源同步接口時序約束方法視頻出爐了!

電子發燒友網ETD第14期SDR源同步接口時序約束方法-會前交流電子發燒友網ETD第14期SDR源同步接口時序約束方法-演講電子發燒友網ETD第14期SDR源同步接口時序約束方法-提問

2015-01-17 16:27:32

ETD第14期:SDR源同步接口時序約束方法

ETD第14期:SDR源同步接口時序約束方法活動詳情 在設計接口時,要滿足同步時鐘和總線信號有確定的時序要求困擾了不少工程師,那么如何有效的解決此問題呢?同步接口約束是FPGA工程師常用的方法之一

2014-12-31 14:21:17

時序約束 專版

此版只討論時序約束約束理論約束方法約束結果時鐘約束(Clock Specification): 約束所有時鐘(包括你的設計中特有的時鐘)對準確的時序分析結果而言是必不可少的。Quartus II

2013-05-16 18:51:50

時序約束之時序例外約束

當邏輯行為以默認的方式不能正確的定時邏輯行為,想以不同的方式處理時序時,必須使用時序例外命令。1. 多周期路徑約束指明將數據從路徑開始傳播到路徑結束時,所需要的時鐘周期

2018-09-21 12:55:34

時序約束是如何影響數字系統的,具體如何做時序分析?

的(頻率和相位都同步),那么數據引腳和時鐘引腳的時序關系以及從引腳到寄存器輸入端的延時共同決定了第一個寄存器的建立時間和保持時間能否得到滿足,設計者可以對數據引腳到寄存器輸入端的延時進行約束。為了保證

2020-08-16 07:25:02

時序約束資料包

好的時序是設計出來的,不是約束出來的時序就是一種關系,這種關系的基本概念有哪些?這種關系需要約束嗎?各自的詳細情況有哪些?約束的方法有哪些?這些約束可分為幾大類?這種關系僅僅通過約束來維持嗎?1

2018-08-01 16:45:40

時序分析總結(以SDRAM時序約束為例)

都是以clock為基準的,記住這個,算的時候就很容易了;4.基本的時序約束有:時鐘約束,IO約束,例外說明,這些都是可以通過timequest來設置的。所謂同步時序,寄存器在同一個時鐘沿動作,所謂異步

2014-12-29 14:53:00

源同步時序系統之基本結構

,這個選通信號也可以稱為源同步時鐘信號。源同步時鐘系統中,數據和源同步時鐘信號是同步傳輸的,我們保證這兩個信號的飛行時間完全一致,這樣只要在發送端的時序是正確的,那么在接收端也能得到完全正確的時序。整個

2014-12-30 13:54:22

源同步的約束該怎么加?

最近遇到個問題,想請教一下大家 FPGA和一個芯片使用源同步的方式通訊,輸出一個時鐘CLK和一個數據總線DataData在內部由全局失蹤clk0驅動,想知道Data的offset約束該怎么加啊? 我

2014-12-29 14:43:02

約束源怎么同步DDR接口

我有一個RGMII接口,時鐘與邊緣的數據DDR對齊。根據我的理解,我應該使用具有90°相位的再生時鐘來采樣具有最佳時序余量。這意味著我必須使用一個PLL我看到用于DDR接口的SelectIO內核,它

2019-03-12 09:56:10

FPGA時序約束--基礎理論篇

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

FPGA時序約束OFFSET

FPGA時序約束,總體來分可以分為3類,輸入時序約束,輸出時序約束,和寄存器到寄存器路徑的約束。其中輸入時序約束主要指的是從FPGA引腳輸入的時鐘和輸入的數據直接的約束。共分為兩大類:1、源同步系統

2015-09-05 21:13:07

FPGA時序約束的幾種方法

Incremental Compilation。這是造成上述兩種方法容易混淆的原因。5. 核心頻率約束+時序例外約束+I/O約束+寄存器布局約束 寄存器布局約束是精確到寄存器或LE一級的細粒度布局約束。設計者

2017-12-27 09:15:17

FPGA時序約束的幾種方法

控。從最近一段時間工作和學習的成果中,我總結了如下幾種進行時序約束的方法。按照從易到難的順序排列如下:0. 核心頻率約束 這是最基本的,所以標號為0。1. 核心頻率約束+時序例外約束 時序例外約束包括

2016-06-02 15:54:04

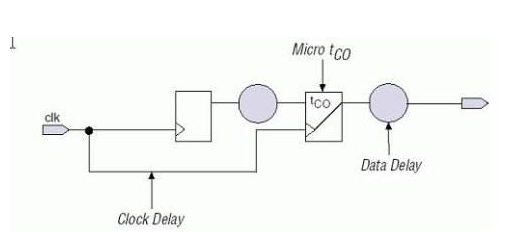

FPGA實戰演練邏輯篇55:VGA驅動接口時序設計之2源同步接口

可以分析一下這個接口的時序要求,然后對其進行約束。這個輸出的信號,其實是很典型的源同步接口,它的時鐘和數據都是由FPGA來驅動產生的。一般的源同步接口的寄存器模型如圖8.25所示。在我們的這個系統中

2015-07-29 11:19:04

FPGA實戰演練邏輯篇56:VGA驅動接口時序設計之3時鐘約束

,FPGA產生的數據data_out和時鐘clk_out的理想波形是時鐘上升沿鎖存到穩定可靠的數據。(特權同學,版權所有)圖8.26 源同步接口寄存器和時序波形關系下面我們來探討如何對這個設計進行約束。首先

2015-07-30 22:07:42

FPGA實戰演練邏輯篇61:CMOS攝像頭接口時序設計1理想時序

/1pJ5bCtt 本實例的CMOS接口是時序分析中典型的pin2reg接口。由于詳細的設計說明將在第12章中,因此大家可以先大體瀏覽過第12章,對整個系統設計有一定了解后,再來進行本節的pin2reg

2015-08-12 12:42:14

FPGA實戰演練邏輯篇64:CMOS攝像頭接口時序設計4時序約束

CMOS攝像頭接口時序設計4時序約束(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s

2015-08-18 21:24:30

FPGA沙龍:SDR源同步接口時序約束方法沙龍精彩內容回顧!

草叢中兩只花,今天的沙龍現場我們還迎來了兩位美女工程師,有木有感覺本次沙龍的氛圍更加輕松了呢~~~!張工正在為大家介紹SDR源同步接口時序約束,學會這個保證你貫穿全部時序問題!會中認真聽講并記錄

2014-12-31 14:25:41

xilinx 時序分析及約束

大部分的時序分析和約束都寫在這里了。 一、基本時序路徑1、clock-to-setup周期約束跨時鐘域約束: (1)當源觸發器和目標觸發器的驅動時鐘不同,且時鐘的占空比不是50

2017-03-09 14:43:24

《EDA工具手冊》約束管理器分冊

第一章 約束管理器介紹41.1約束管理器簡介41.2約束管理器界面簡介81.2.1worksheet selector81.2.2用戶接口91.2.3View選項91.3啟動約束管理器11第2章

2017-11-10 12:30:42

【潘文明至簡設計法】系列連載教程 FPGA時序約束視頻教程

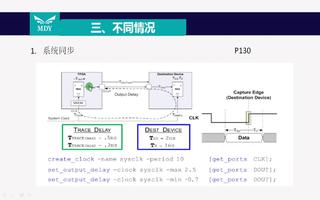

延時約束是約束的重點。明德揚把輸入約束分成三大類:系統同步、源同步和無時鐘數據,其中源同步分成SDR和DDR兩場景,而DDR又可再細分成邊沿對齊和中心對齊。以上每種情況,其約束語句、獲取參數的方法都是

2017-06-14 15:42:26

【轉帖】經驗總結:FPGA時序約束的6種方法

控。 下文總結了幾種進行時序約束的方法。按照從易到難的順序排列如下: 0. 核心頻率約束 這是最基本的,所以標號為0。1. 核心頻率約束+時序例外約束 時序例外約束包括FalsePath

2017-10-20 13:26:35

與時鐘頻率不同的源同步數據如何約束?

考慮第4個約束。我還試圖使用MMCM生成的時鐘來設置OFFSET = IN約束TIMEGRP“sdr_c_0”OFFSET = IN 3.125 ns有效6.25 ns在“CMX_input_inst

2018-10-16 17:14:28

關于時序約束

本帖最后由 seduce 于 2015-2-3 14:20 編輯

關于約束今天在研究時序約束這一塊,于是想著上來和大家分享一下心得,同時和大家交流交流,互相成長,歡迎批評指正。首先說一下

2015-02-03 14:13:04

關于FPGA時序約束的一點總結

)。方法2調試起來簡單,PLL設置簡單,出錯可能性小。通過不斷調整相位,最終肯定可以正確通信。缺點也明顯,接口一多,每個都要做隨路時鐘就浪費了。最近一直在做時序約束,總結一下時序約束過程。(1)根據時序

2016-09-13 21:58:50

分享一個關于源同步接口時序分析與相移計算的例子

= ((td2- tc1-7ns)+( td1+7ns-tc2))/2 = (td2+td1-tc1-tc2)/2 回頭看看,其實這類時序也是非常典型的源同步接口,和SDRAM接口相比,SDRAM不僅

2014-12-26 16:36:46

對邊沿對齊源同步輸入端口的約束

[get_ports data_in*] -add #對false path的約束。#對于源同步接口,virt_clk為Launch Clock#data_clock為Latch

2014-12-25 14:28:06

本人小白,請教什么是源同步接口?

最近經常看到有人在聊源同步接口,但是百度、谷歌也沒找到太多相關的信息,不找到哪位大神可以解釋一下什么是源同步接口啊?它的用途是什么呢?可以做些什么呀?十分感謝,本人小白,希望大家不要見笑哈!

2014-12-26 15:51:35

榮小菜補鈣記第55期: AF消息傳遞太麻煩?試試接口吧!

榮小菜補鈣記第55期: AF消息傳遞太麻煩?試試接口吧!同步更新于 WeChat:榮小菜在補鈣歡迎關注 內容更豐富大家好,我是榮小菜,本期講解下在操作者框架中使用接口類來傳遞消息的方法,該方法主要

2022-01-23 11:47:41

詳解FPGA的時序以及時序收斂

參考ug612。4.輸出時序約束輸出就是輸入的逆,因此分析的過程是類似的,分類也是類似的。針對時鐘的不同,有系統同步和源同步兩種。此處不再詳細說明。系統同步SDR源同步DDR(一般來說不給約束就可以)5.

2019-07-09 09:14:48

請教時序約束的方法

我是一個FPGA初學者,關于時序約束一直不是很明白,時序約束有什么用呢?我只會全局時鐘的時序約束,如何進行其他時序約束呢?時序約束分為哪幾類呢?不同時序約束的目的?

2012-07-04 09:45:37

高云半導體時序約束的相關內容

實現時序約束以及如何閱讀STA 報告。有關本手冊中的高云半導體云源?軟件(以下簡稱云源)界面截圖參考的是 1.9.8.01 版本。因軟件版本更新,部分信息可能會略有差異,具體以用戶軟件版本信息為準。

2022-09-29 08:09:58

同步時序邏輯電路

同步時序邏輯電路:本章系統的講授同步時序邏輯電路的工作原理、分析方法和設計方法。從同步時序邏輯電路模型與描述方法開始,介紹同步時序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0

0

0時序約束與時序分析 ppt教程

時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎常用時序概念QuartusII中的時序分析報告

設置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0

0

0時序約束用戶指南

時序約束用戶指南包含以下章節: ?第一章“時序約束用戶指南引言” ?第2章“時序約束的方法” ?第3章“時間約束原則” ?第4章“XST中指定的時序約束” ?第5章“Synplify中指定的時

2010-11-02 10:20:56 0

0

0

0Xilinx時序約束培訓教材

時序約束的概念 時序約束主要包括周期約束(FFS到FFS,即觸發器到觸發器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態路徑約束(STA, IPAD到OPAD)等3種。通過附加約束條件可以使綜合布線工具調整映射和布局布線過程,使設計達到時序要求。例如用OFFSET_IN_BEFORE

2011-03-16 18:10:38 0

0

0

0FPGA開發之時序約束(周期約束)

偏移約束。 這里先說一下周期約束:周期約束是為了達到同步組件的時序要求。如果相鄰同步原件相位相反,那么延遲就會是時鐘約束值的一半,一般不要同時使用上升沿和下降沿。注意:在實際工程中,附加的約束時間為期望值的

2017-02-09 02:56:06 605

605

605

605基于FPGA 和 SoC創建時序和布局約束以及其使用

作時序和布局約束是實現設計要求的關鍵因素。本文是介紹其使用方法的入門讀物。 完成 RTL 設計只是 FPGA 設計量產準備工作中的一部分。接下來的挑戰是確保設計滿足芯片內的時序和性能要求。為此

2017-11-17 05:23:01 2417

2417

2417

2417

FPGA中的時序約束設計

一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

2326

2326

深入了解時序約束以及如何利用時序約束實現FPGA 設計的最優結果

作為賽靈思用戶論壇的定期訪客(見 ),我注意到新用戶往往對時序收斂以及如何使用時序約束來達到時序收斂感到困惑。為幫助 FPGA設計新手實現時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實現

2017-11-24 19:37:55 4903

4903

4903

4903

添加時序約束的技巧分析

。 在添加全局時序約束時,需要根據時鐘頻率劃分不同的時鐘域,添加各自的周期約束;然后對輸入輸出端口信號添加偏移約束,對片內邏輯添加附加約束。

2017-11-25 09:14:46 2347

2347

2347

2347FPGA時序約束簡介

在簡單電路中,當頻率較低時,數字信號的邊沿時間可以忽略時,無需考慮時序約束。但在復雜電路中,為了減少系統中各部分延時,使系統協同工作,提高運行頻率,需要進行時序約束。通常當頻率高于50MHz時,需要考慮時序約束。

2018-03-30 13:42:59 14208

14208

14208

14208

【時序約束資料包】培訓課程Timing VIVADO

好的時序是設計出來的,不是約束出來的 時序就是一種關系,這種關系的基本概念有哪些? 這種關系需要約束嗎? 各自的詳細情況有哪些? 約束的方法有哪些? 這些約束可分為幾大類? 這種關系僅僅通過約束

2018-08-06 15:08:02 400

400

400

400進行時序約束的方法都在這里,趕緊收藏

1. 核心頻率約束 這是最基本的,所以標號為0。 2. 核心頻率約束+時序例外約束 時序例外約束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但這還

2018-09-21 22:04:01 1440

1440

1440

1440

如何使用時序約束向導

了解時序約束向導如何用于“完全”約束您的設計。

該向導遵循UltraFast設計方法,定義您的時鐘,時鐘交互,最后是您的輸入和輸出約束。

2018-11-29 06:47:00 2702

2702

2702

2702

時序約束步驟:系統同步與源同步

針對普通時鐘系統存在著限制時鐘頻率的弊端,人們設計了一種新的時序系統,稱之為源同步時序系統。它最大的優點就是大大提升了總線的速度,在理論上信號的傳送可以不受傳輸延遲的影響。

2019-12-20 07:09:00 4151

4151

4151

4151

賽靈思關于I/O約束法的簡要概括(下)

DDR接口的約束稍許復雜,需要將上升沿和下降沿分別考慮和約束,以下以源同步接口為例,分別就Setup/Hold Based 方法和Skew Based方法舉例。

2019-07-25 11:01:38 2457

2457

2457

2457

FPGA時序約束的建立和保持時間方法

首先來看什么是時序約束,泛泛來說,就是我們告訴軟件(Vivado、ISE等)從哪個pin輸入信號,輸入信號要延遲多長時間,時鐘周期是多少,讓軟件PAR(Place and Route)后的電路能夠

2020-01-28 17:34:00 3077

3077

3077

3077

Vivado進行時序約束的兩種方式

上面我們講的都是xdc文件的方式進行時序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進行時序約束:時序約束編輯器(Edit Timing Constraints )和時序約束向導(Constraints Wizard)。兩者都可以在綜合或實現后的Design中打開。

2020-03-08 17:17:00 19067

19067

19067

19067

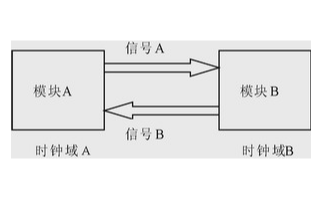

多時鐘域的同步時序設計和幾種處理異步時鐘域接口的方法

在數字電路設計中,大部分設計都是同步時序設計,所有的觸發器都是在同一個時鐘節拍下進行翻轉。這樣就簡化了整個設計,后端綜合、布局布線的時序約束也不用非常嚴格。但是在設計與外部設備的接口部分時,大部分

2020-07-24 09:52:24 3920

3920

3920

3920

正點原子FPGA靜態時序分析與時序約束教程

靜態時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態時序分析,靜態時序分析不需要測試矢量,而是直接對芯片的時序進行約束,然后通過時序分析工具給出

2020-11-11 08:00:00 58

58

58

58FPGA時序約束的6種方法詳細講解

對自己的設計的實現方式越了解,對自己的設計的時序要求越了解,對目標器件的資源分布和結構越了解,對EDA工具執行約束的效果越了解,那么對設計的時序約束目標就會越清晰,相應地,設計的時序收斂過程就會更可控。

2021-01-11 17:44:44 8

8

8

8FPGA時序約束的常用指令與流程詳細說明

器件共用外部時鐘;源同步(SDR,DDR)即時鐘與數據一起從上游器件發送過來的情況。在設計當中,我們遇到的絕大部分都是針對源同步的時序約束問題。所以下文講述的主要是針對源同步的時序約束。

2021-01-11 17:46:32 13

13

13

13FPGA時序約束的概念和基本策略

A 時序約束的概念和基本策略 時序約束主要包括周期約束(FFS到FFS,即觸發器到觸發器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態路徑約束(IPAD到OPAD)等3種。通過附加

2021-09-30 15:17:46 4401

4401

4401

4401創建輸入輸出接口時序約束的竅門

時序約束中的 set_input_delay/set_output_delay 約束一直是一個難點,無論是概念、約束值的計算,還是最終的路徑分析,每一次都要費一番腦子。Vivado為方便用戶創建

2022-08-02 09:54:20 1797

1797

1797

1797

約束、時序分析的概念

很多人詢問關于約束、時序分析的問題,比如:如何設置setup,hold時間?如何使用全局時鐘和第二全局時鐘(長線資源)?如何進行分組約束?如何約束某部分組合邏輯?如何通過約束保證異步時鐘域之間

2023-05-29 10:06:56 372

372

372

372

如何在Vivado中添加時序約束呢?

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向導(Constraints Wizard)、時序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

1847

1847

靜態時序分析的基本概念和方法

向量和動態仿真 。本文將介紹靜態時序分析的基本概念和方法,包括時序約束,時序路徑,時序裕量,setup檢查和hold檢查等。 時序路徑 同步電路設計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最

2023-06-28 09:38:57 714

714

714

714

電子發燒友App

電子發燒友App

評論