?

在嵌入式系統中經常采用IIS(Inter-IC Sound)總線連接專用音頻器件以實現音頻輸入輸出。不少嵌入式處理器帶有專用的IIS總線,通過操作特殊功能寄存器實現對外接音頻器件的操作,但也有一些嵌入式處理器沒有擴展IIS總線,如ARM7芯片S3C4510B。近年來,FPGA技術發展迅速,現已成為可編程片上系統(SoPC)的硬件載體。采用FPGA實現IIS總線及與總線相關的接口控制,一方面可以用硬件的方法實現IIS總線操作,使嵌入式系統很容易擴展音頻功能;另一方面由于FPGA可以實現大量的組合邏輯和時序邏輯,還可以用來實現DSP算法,增加了系統的靈活性。

1 基本原理

1.1 系統方案

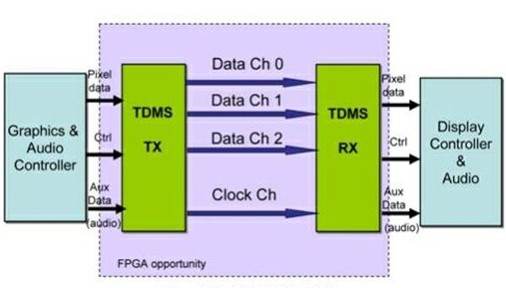

嵌入式處理器采用Samsung公司的ARM7芯片S3C4510B;音頻芯片使用Philips 公司開發的UDA1341TS,這是一款適用于MiniDisc(MD)、PDA等便攜式設備的高性能低功耗的經濟型音頻編碼解碼器;FPGA芯片則使用 Xilinx公司的Spartan-II 系列芯片XC2S100。系統示意圖如圖1。

?

圖1中FPGA負責連接S3C4510B和UDA1341TS,為此需要按照訪問UDA1341TS的時序要求實現IIS總線和L3接口,同時要按照S3C4510B總線時序要求,實現按存儲器方式操作的特殊功能寄存器,并將對UDA1341TS的操作轉換成對特殊功能寄存器的操作。這樣S3C4510B便可以直接訪問FPGA實現的特殊功能寄存器,從而實現對UDA1341TS的控制。

1.2 IIS和UDA1341TS簡介

IIS又稱I2S, 是Philips公司提出的串行數字音頻總線協議,專用于芯片間進行高速高效的音頻數據傳輸。IIS總線只處理聲音數據,其他信號必須單獨傳輸,如控制信號。IIS總線包括3 個信號線,即1個雙向數據傳輸線SD(Serial Data)、一個聲道選擇線WS(Word Select)和1個時鐘線SCK(Serial Clock)。在數據傳輸過程中,發送端和接收端具有相同的時鐘信號,發送端作為主裝置(Master)時,產生位時鐘信號和聲道選擇信號,接收端被動響應。為了實現全雙工傳輸模式,一些IIS實現時使用了Dout和Din兩個數據線。

UDA1341TS片內集成了立體聲ADC、DAC以及模擬輸入通道,其中模擬輸入通道包括可編程增益放大器(PGA)、數字自動增益控制(AGC)、 數字聲音處理(DSP)等。UDA1341TS的重放過程也具有可編程的DSP功能,如去加重、音量控制、低音增強、高音增強以及軟件配置靜音等。

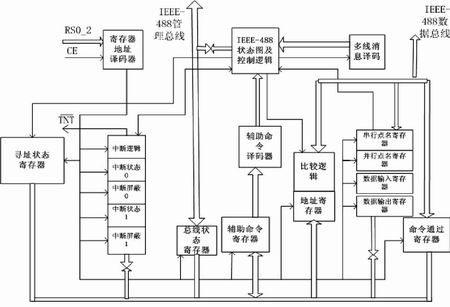

根據串行音頻數據輸入輸出格式和每聲道字長的不同,UDA1341TS支持4種操作模式,分別是:(1)字長不超過20位的IIS總線模式;(2)字長不超過20位的最高位對齊(MSB-justified)模式;(3)字長為16、18或20位的最低位對齊(LSB-justified)模式;(4)輸出采用最高位對齊,輸入采用字長為16、18或20位的最低位對齊模式。其中IIS總線模式和最高位對齊模式操作時序如圖2所示。二者具有相同的信號線,但左右聲道控制電平和位延遲不同,對于IIS總線,聲道控制電平改變后,最高位推遲一個時鐘周期才發送。

?

對UDA1341TS的所有功能控制和狀態獲取均通過3線串行接口L3實現。該接口包含3個信號線,分別是串行數據線L3DATA、接口模式選擇線L3MODE和串行時鐘線L3CLOCK。L3接口操作有兩種模式,即地址模式和數據傳輸模式。地址模式用于選中后續操作所要訪問的芯片及其內部寄存器,被地址模式選中的芯片和寄存器一直保持有效,直到UDA1341TS收到一個新的地址模式命令字節。數據傳輸模式用于將音頻處理和系統控制參數寫入UDA1341TS并可以讀取回放的音頻數據的峰值電平。L3MODE為低電平時操作為地址模式,高電平時操作為數據傳輸模式。

地址模式下由主器件按標準時序送出8位地址,其中高6位表示UDA1341TS芯片地址000101,最低2位選擇要訪問的該芯片內部寄存器,分別是DATA0、DATA1和STATUS,由此產生下面的3種寄存器操作模式。

(1)STATUS操作模式可以控制芯片復位、系統時鐘頻率、數據輸入格式、DC濾波器、輸入增益、輸出增益、ADC和DAC極性控制、倍速播放和功率控制等。

(2)DATA0操作模式又分為兩種:直接地址模式和擴展地址模式。數據最高2位非‘11’時為直接地址模式,在這種模式下,可以直接控制音量、低音增強、高音增強、峰值檢測位置、去加重、靜音等功能;數據最高2位為‘11’時為擴展地址模式,可以通過3位選擇6個5位的擴展寄存器,分別控制通道混合增益、MIC靈敏度、自動增益控制、輸入放大器增益器等。

(3)DATA1操作模式用于讀取音頻數據重放時的峰值電平。

2 FPGA設計及功能仿真

如圖1所示,FPGA負責連接S3C4510B和UDA1341TS,需要實現S3C4510B總線接口、IIS總線和L3接口等。采用模塊化設計思想,劃分幾個功能相對獨立的模塊,并將各個功能模塊封裝成元件(Component),分別設計、仿真、測試、驗證各元件,最后在頂層調用各元件,并將元件信號與實際輸入輸出信號關聯,實現整體功能。實際實現了4個元件,如圖2所示。

圖2中,元件ARM_Interface負責實現與S3C4510B接口,主要是實現幾個可以映射成存儲器的地址單元,并提供這些單元與其他元件的接口。其中左右聲道單元為16位,在內部分別與2個FIFO相連接,以便音頻數據以選定的速率回放;IIS_out元件負責產生IIS總線或MSB對齊模式時序;L3_3B_Mod元件實現UDA1341TS數據傳輸模式中的DATA0擴展地址模式,共需傳輸3個字節;L3_2B_Mod元件則負責UDA1341TS其余的操作模式,只需傳輸2字節,即1字節地址和1字節數據。采用這種元件模塊設計的方法主要考慮到FPGA容易實現并行操作,但對復雜條件操作和邏輯判斷則不如處理器編程實現方便。因此并行實現多個元件,再由簡單邏輯和條件及輸入參數控制選定的元件工作,以實現需要的功能,這是FPGA設計的主要思想。

2.1 嵌入式處理器接口實現

此模塊主要負責處理與嵌入式系統的數據傳輸接口。主要輸入信號包括全局時鐘GCLK、片選信號nCS、寫信號nWBE0、讀信號nOE以及地址信號ADDR[4..0],其中地址信號確定相對于片選地址的偏移地址,5位地址信號最多可尋址32個16位地址單元。所有總線數據操作與全局時鐘同步。根據需要,實際設計實現了7個寄存器,分別是DATA0直接地址寄存器、DATA0擴展地址寄存器、DATA1寄存器、STATUS寄存器、左聲道音頻數據緩存器、右聲道音頻數據緩存器、FPGA控制寄存器,它們的偏移地址分別是0x00100、0x00110、0x01000、0x10100、0x00000、0x00010、0x01100。上述寄存器中,只有左右聲道音頻數據緩存器為16位,其余均為8位,因此只能實現不超過16位的IIS總線和MSB對齊模式。

測試本元件時,首先應測試單元的讀寫特性,通過ARM仿真器直接對編程單元進行讀寫即可驗證擴展的正確性。對于內建16x8的FIFO的左右聲道數據緩存器,可以通過讀寫多次測試其滿空狀態,并通過1個接在FPGA的I/O口線上的LED直接觀察。測試無誤后,該元件便可使用。

2.2 IIS總線實現

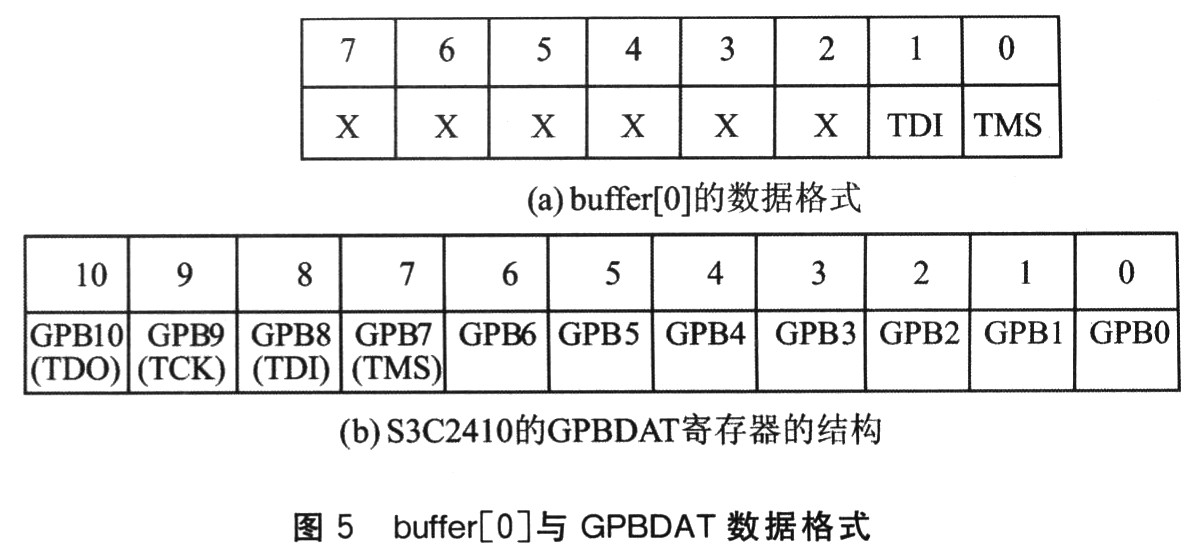

IIS總線通過IIS_out元件來實現,其接口信號如圖3所示。輸入信號是ARM_Interface提供的左右聲道音頻數據,輸出信號是IIS總線要求的3個串行信號,即bclk、sync和dout,分別與SCK、WS和SD對應,這3個信號通過FPGA的I/O口線與UDA1341的BCK、WS以及DATAI與DATAO信號線相連。IIS 格式的信號無論有多少位有效數據,數據的最高位(MSB)總是被最先傳輸,在WS 變化后的第2 個SCK脈沖處,因此最高位擁有固定的位置,而最低位的位置則依賴于數據的有效位數。實際設計的數據有效位是16位,低于16位數據時高位填充‘0’,處理器將數據以16位方式寫入左右聲道音頻數據緩存器時,自動進行高位填充。

?

實現IIS總線時序時,關鍵是要正確處理各種時鐘信號之間以及生成的IIS總線3個信號之間的時序關系。要依據音頻信號的采樣速率選擇FPGA系統時鐘和UDA1341時鐘選項,同時要合理使用計數器并正確讀取左右聲道音頻數據緩存器,最終實現音頻數據通過IIS總線的正確傳輸。

設計實現的IIS時序仿真圖如圖4所示。

?

圖4顯示的是IIS_out元件將左右聲道音頻數據緩存器內2個16位數據由IIS總線輸出的時序仿真結果。bclk信號的上升沿數據dout穩定有效,在bclk為低電平時dout才變化。當左右聲道控制信號sync為低電平時,傳輸左聲道數據‘0111011101110111’;當sync為高電平時,傳輸右聲道數據‘1010101010101010’。從仿真波形可知,每聲道數據反映在dout波形上是從sync電平變化后的第2個bclk周期開始的。

圖2所示的最高位對齊模式與IIS使用相同的信號,很容易在IIS總線的基礎上修改實現。實際實現的最高位對齊模式仿真時序正確,在此不再詳述。

2.3 L3接口實現

由于IIS總線只處理聲音數據,其他信號必須單獨傳輸,所以為了控制UDA1341TS而設計了L3接口。在FPGA實現L3接口時,根據UDA1341TS操作模式的不同,設計了兩個元件。圖3中元件L3_2B_Mod用于只需傳輸1字節地址和1字節數據的情況,而L3_3B_Mod則用來傳輸1字節地址和兩字節數據。

為了便于控制,在元件ARM_Interface中專門設置了一個控制寄存器來控制L3接口的工作模式,該寄存器偏移地址為0x01100,其高4位有定義。最高位為接口允許位TRANS_EN,為‘1’時L3接口啟動工作,為‘0’時停止;次高位為L3接口工作模式選擇位TRANSMODE,為‘0’時選擇L3_2B_Mod,為‘1’時選擇L3_3B_Mod;接下來的二位用于選擇寄存器。

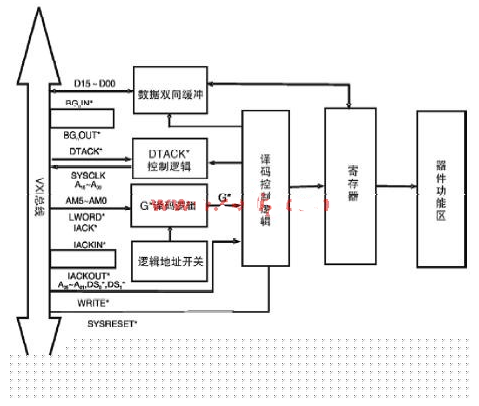

實際設計實現的元件L3_3B_Mod時序仿真圖見圖5。

圖5顯示的是L3接口DATA0擴展地址模式時序圖,共傳輸了3字節數據,即1個地址字節、2個數據字節。地址字節的高6位為UDA1341TS地址,低2位選擇DATA0操作模式,緊接著的數據字節最高兩位為‘11’選擇擴展地址模式,這意味著該字節后面還要傳輸1字節數據。圖5中的3字節分別為0x14、0xC4和0xF0,該命令將打開輸入通道的自動增益控制。L3接口要求串行數據的低位在前傳輸,這一點與IIS有所不同。

實現L3_3B_Mod元件時引入了一個參考時鐘REF_CLK,由一個5位計數器對該時鐘信號計數,根據L3接口在3字節操作時的時鐘信號圖案,控制由REF_CLK生成L3CLOCK,得到L3CLOCK之后,L3接口的操作均以此時鐘信號來同步。

元件L3_2B_Mod設計及仿真結果與L3_2B_Mod類似。

3 測試方法及結果

在以S3C4510B為核心的嵌入式系統中,根據存儲器配置情況,選擇一段未用的存儲空間,將FPGA實現的寄存器映射成S3C4510B在該段存儲空間中的存儲單元,這樣就可以用C語言編程來訪問這些存儲單元,從而實現對UDA1341TS的控制。實際選擇了S3C4510B的可重定位片選信號nRCS1作為FPGA實現的寄存器基地址選擇信號,并將該片選地址定位為0x12000000,這樣各寄存器的實際地址如表1。

?

根據UDA1341TS命令列表,在Hitool For ARM support μClinux軟件開發環境下,編寫C語言程序,測試STATUS操作和DATA0操作功能及結果。程序運行之前需要用JTAG下載電纜將ISE開發環境下生成的bit文件下載 到FPGA芯片中,以實現要求的功能。

經實際測試,通過FPGA實現的IIS總線和L3接口,S3C4510B可以控制UDA1341TS芯片完成各種操作,實現STATUS操作模式和DATA0模式的各種控制功能,并可用DATA1操作模式獲取音頻數據重放時的峰值電平。

編寫測試程序,輸出1kHz正弦信號,并控制聲道、音量、靜音等變化,示波器觀察和耳機聽到的結果正確。

編寫測試程序,讀入麥克風音頻信號,分時由左右聲道輸出,測試結果正確。

本設計采用音頻接口專用芯片UDA1341TS,并通過FPGA實現了IIS總線和L3接口,使得基于S3C4510B的嵌入式系統可以方便地擴展音頻功能,實驗結果正確。

在本文工作的基礎上,可以進一步發揮FPGA的靈活性。如可以利用FPGA實現DSP功能,從而提供音頻DSP處理或編碼解碼;也可以與SoPC相結合,作為音頻接口模塊,為片上系統提供音頻接口。

電子發燒友App

電子發燒友App

評論