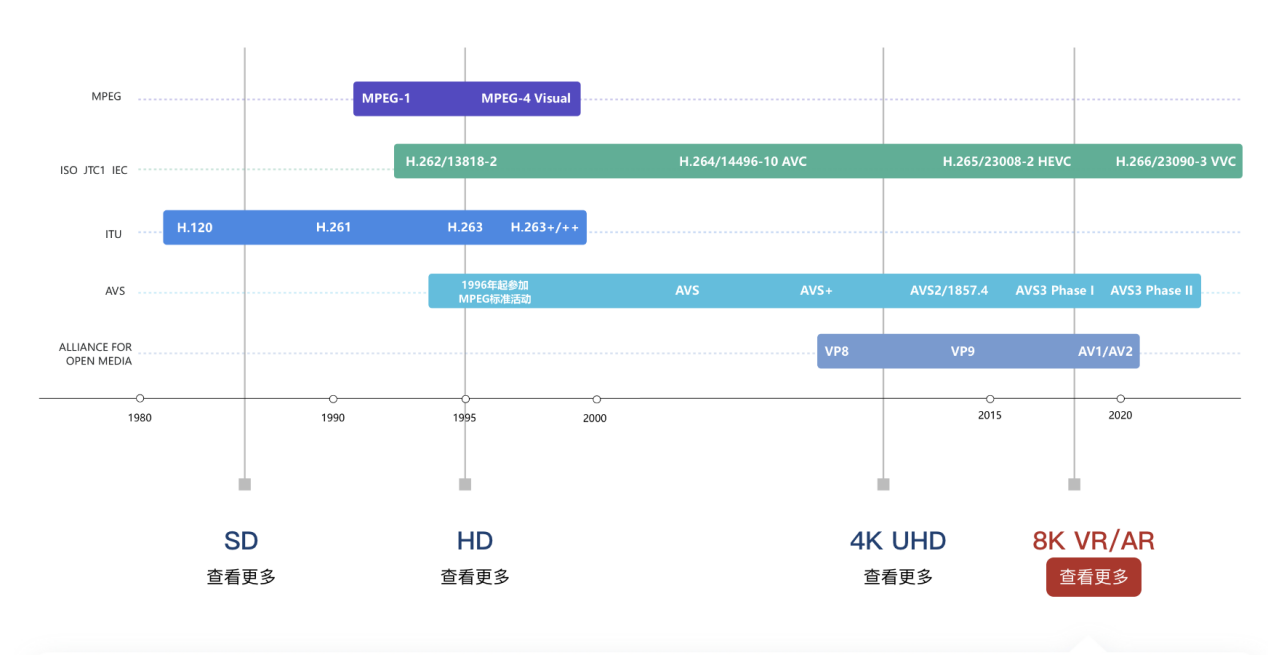

AVS標準是《信息技術先進音視頻編碼》系列標準的簡稱,是我國具備自主知識產權的第二代信源編碼標準。AVS標準包括系統、視頻、音頻、數字版權管理等四個主要技術標準和一致性測試等支撐標準。

目前音視頻產業可以選擇的信源編碼標準有四個:MPEG-2、MPEG-4、AVC(也稱JVT、H.264)和AVS。從制訂者分,前三個標準是由MPEG專家組完成的,第四個是我國自主制定的。從發展階段分,MPEG-2是第一代信源標準,其余三個為第二代標準。從主要技術指標——編碼效率比較,MPEG-4是MPEG-2的1.4倍,AVS和AVC相當,都是MPEG-2的兩倍以上。

AVC標準中,對預測殘差有兩種熵編碼的方式:基于上下文的自適應變長碼(CAVLC)和基于上下文的自適應二進制算數編碼(CABAC);對于非預測殘差,采用指數哥倫布碼或CABAC編碼,視編碼器的設置而定[1]。

AVS標準所用的熵編碼技術相比于以前有了很多改進,它的語法元素和殘差系數是由定長碼和指數哥倫布碼構成的,其中指數哥倫布碼和語法元素之間存在多種映射關系。

1 AVS標準熵解碼算法描述

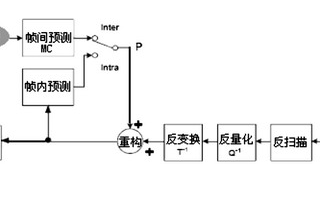

在整個AVS視頻的解碼過程中,熵解碼模塊位于系統的最前端,負責從壓縮后的碼流中解析出宏塊頭信息以及量化系數,供后續的幀內預測模塊和幀間預測模塊使用。而熵解碼模塊又可以大體分為兩個部分:解析K階指數哥倫布碼部分和解析語法元素部分。

解析K階指數哥倫布碼時,首先從比特流的當前位置開始尋找第一個非零比特,并將找到的零比特個數記為leadingZeroBits,然后根據leadingZeroBits計算CodeNum。用偽代碼描述如下:

由于AVS視頻中所有的語法元素以及經過變換和量化的殘差系數都是以指數哥倫布碼的形式映射成二進制碼流的,因此在解析出K階指數哥倫布碼的CodeNum后,下一步就是要還原出各種語法元素和殘差系數。

在AVS標準中規定了四種映射方式:ue(v)、se(v)、me(v)和ce(v)。其中ue(v)、se(v)和me(v)所描述的語法元素采用0階的指數哥倫布碼,ce(v)用來描述殘差系數,可以采用0階、1階、2階或者3階指數哥倫布碼。它們的解析過程如下:

ue(v):無符號直接映射,語法元素的值等于CodeNum;

se(v):有符號映射,映射關系為:當CodeNum=k時,語法元素值為(-1)k+1×Ceil(k÷2)

me(v):分為MbCBP和MbCBP422兩種模式,分別根據CodeNum的值,查找相對應的表來得到語法元素的值。

ce(v):ce(v)描述的語法元素可以采用0階、1階、2階或3階指數哥倫布碼進行解析,還有19個相關的碼表,對于階數的確定規則以及碼表的切換規則,在AVS標準中都有詳細的說明。解析時,首先語法元素trans_coefficient等于CodeNum,如果trans_coefficient小于59,可以根據trans_coefficient的值查找相關的碼表得到殘差系數;如果trans_coefficient大于等于59,解析下一個ce(v)語法元素,得到一個新的CodeNum,escape_level_diff等于CodeNum,然后根據trans_coefficient和escape_level_diff求得殘差系數[3]。

2 熵解碼器的硬件設計

由于熵解碼器位于整個解碼結構的最前端,所有后續模塊中需要用到的數據都是熵解碼模塊從原始碼流中解析出來的,因此熵解碼器性能的優劣直接影響到整個AVS視頻解碼器的性能。

從前面的介紹中可以了解到,經過指數哥倫布編碼后形成的碼流中,每個碼的碼長不固定,而且前后具有很大的相關性,這樣在解碼時就必須逐位讀取數據,解析完一個碼字后才能解析下一個碼字。這種串行解碼的方式嚴重限制了熵解碼器的性能,所以需要找到一種能夠并行解碼的方式。這里的并行解碼并不是指同時對好幾個碼進行解碼,而是針對一個變長碼的多個位來說的。具體來說就是一次讀入N位數據,通過比較操作,得到碼長,使得解碼可以在確定的時間長度內進行,而不是隨著碼長的不同而變化。顯然,這將提高硬件的復雜度,但是換來了解碼速度的提高[4]。

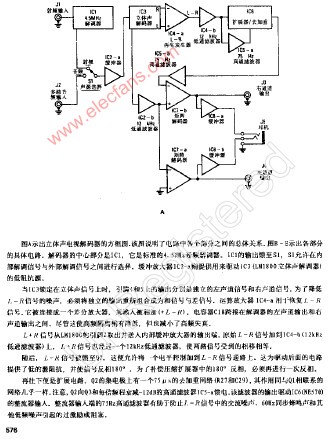

整個熵解碼器可以分為四個模塊:數據準備模塊、解指數哥倫布碼模塊、語法元素解析模塊和解碼控制模塊。硬件結構如圖1所示。

?

下面通過分析碼流數據的解析過程來逐個說明各個模塊的功能和實現。

2.1 數據準備模塊

這個模塊的功能是為后邊的解指數哥倫布碼模塊準備好未解碼數據,要求解指數哥倫布碼模塊解完一個碼,數據準備模塊就要在碼流中將解完的碼移走,并準備好下一個要解的碼字送給下一模塊。硬件結構如圖2所示。

?

RegA和RegB是兩個32位的寄存器,其中RegB直接從未解碼碼流中讀取數據,RegA則接收RegB中的數據,兩個寄存器共同組成barrelshifter的輸入。

barrelshifter是一個64位輸入、32位輸出的暫存器,每次輸出都將剛解完的一個碼字移出,以保證輸出的32位數據中最低位為下一個要解碼的碼字的開始。移位的位數由輸入的地址Addr來決定,即輸出64位輸入的[Addr,Addr+31]位。

當En信號有效時,更新數據,將RegB中的數據存到RegA中,再從碼流中讀取新的32位數據,存到RegB中。其中Addr和En信號由解指數哥倫布碼模塊給出。

2.2解指數哥倫布碼模塊

這個模塊的功能是接收上一模塊準備好的未解碼數據,計算出從最低位開始的一個指數哥倫布碼的CodeNum,并根據這個碼的碼長算出筒形移位器的移位地址。模塊結構如圖3所示。

?

由于上一個模塊準備好的未解碼碼流是一個以新的指數哥倫布碼的開始為最低位的32位碼流,因此要計算出這個碼的CodeNum,首先要算出這個碼的碼長,然后在這32位數據中截取出這個碼字,才可以計算它的CodeNum。根據指數哥倫布碼的結構,碼長與這個碼的前導零個數M和階數K有密切關系,可以總結出一個公式:CodeL=2×M+K+1。碼長計算模塊就是根據這個原理來計算碼長的,首先通過一組比較器檢測從最低位開始有幾個零,然后根據上述公式得到碼長。對于階數K,解ue(v)、me(v)和se(v)語法元素時,階數K為0。解ce(v)時,當前解碼碼字的階數在解碼上一個碼字時可以得出。

累加器模塊是一個模為32的加法器,將碼長計算模塊計算出來的碼長CodeL累加到上一次的移位地址上,得到一個新的移位地址,筒形移位器根據這個新的地址,將本次解碼的碼字移出,準備好下一個未解碼碼流。En為進位輸出,當累加器的En為1時,說明已經解完了32位數據,這時需要對RegA和RegB進行數據更新。

計算碼字的CodeNum時,首先根據碼長計算模塊算出來的碼字長度,從上一模塊準備好的未解碼碼流中把本次要解碼的碼字截取出來,拋棄無用的位,然后再根據公式CodeNum=2leadingZeroBits+k-2k+read_bits(leadingZeroBits+k)計算這個碼字的CodeNum。顯然這個公式太過復雜,不適合直接硬件化,但是經過分析公式以及指數哥倫布碼的結構,可以改造一下公式。因為指數哥倫布碼的結構為前面M個前導0,中間一個1,后面M+K位數據組成,而read_bits(leadingZeroBits+k)即為后面M+K位數據的碼字值,2leadingZeroBits+k正好為中間那個1的碼字值,所以一個碼字的CodeNum就等于這個碼字的碼字值減去2k,這樣對CodeNum的計算就大大簡化了。

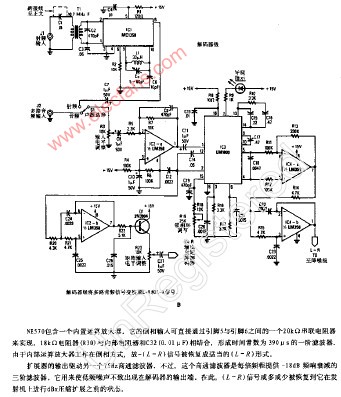

2.3 語法元素解析模塊

顧名思義,這個模塊就是最終解析出語法元素含義的模塊,它接收上一模塊計算出來的CodeNum值,然后主要通過查表的方式解析出這個碼字所代表的語法元素含義,結構如圖 4所示。

?

這里主要介紹下最復雜的ce(v)部分的解析過程。

逃逸碼判斷模塊:在解析ce(v)語法元素時,首先要判斷是否為逃逸碼,即CodeNum<59時,按照正常ce(v)語法元素解析規則解析;CodeNum≥59時,下一碼字為逃逸碼,則按照逃逸碼解析規則解析。

ce(v)語法元素解析模塊:正常ce(v)語法元素的解析過程為:以CodeNum的值為索引,查找當前碼表,得到(run、level),然后根據標準中的碼表切換規則進行碼表切換,并得到下一碼字的階數K。解析逃逸碼的解析過程為:令transcoefficient等于CodeNum,得到run=(transcoefficient-59)/2。以當前碼表為索引,查表得到對應的MaxRun,如果run>MaxRun,則RefAbslevel=1,否則以run為索引查當前碼表,得到RefAbslevel。解析下一個語法元素,得到一個新的Codenum,escape_level_diff等于CodeNum。如果transcoefficient為奇數,則level等于-(RefAbslevel+escape_level_diff);如果transcoefficient為偶數,則level等于(RefAbslevel+escape_level_diff)。最后再按照標準中的碼表切換規則進行碼表切換,等待解析下一個語法元素。

3 測試與驗證

將本文提出的熵解碼器結構設計用Verilog HDL實現,用ModelSim在綜合前進行仿真,仿真模型如圖5所示。AVS標準參考軟件產生測試碼流數據,將測試碼流數據輸入硬件描述語言仿真模型,然后將輸出數據與標準輸出對比,實現仿真功能。經過測試,硬件熵解碼后的數據與軟件熵解碼后的數據完全一致。

?

整個電路使用Altera的QuartusII 9.0軟件進行綜合,使用的LE總數為1 906個。變字長解碼器模塊是AVS解碼器的一部分,綜合后與其他部分集成,通過了FPGA驗證,采用CycloneII系列的EP2C35型FPGA,其最高頻率能達到94 MHz,可以實現AVS高清晰度視頻的實時解碼。圖6為ce(v)解碼模塊的功能仿真結果圖。

?

本文提出了一種基于AVS標準的熵解碼器的硬件結構,從總體設計到各個模塊的設計都使用了流水線、并行處理、可重用設計等硬件設計的思想和方法;采用Verilog硬件描述語言實現,并通過FPGA進行了驗證,達到了標準清晰度實時解碼的要求。

電子發燒友App

電子發燒友App

評論