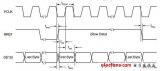

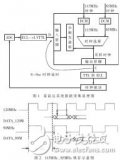

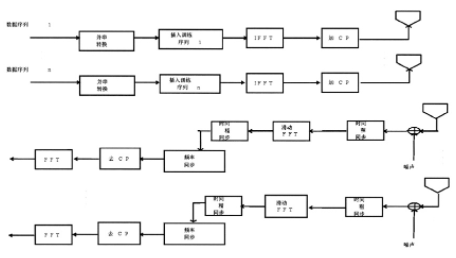

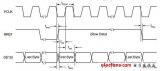

對于數據采集接收的一方而言,所謂源同步信號,即傳輸待接收的數據和時鐘信號均由發送方產生。FPGA應用中,常常需要產生一些源同步接口信號傳輸給外設芯片,這對FPGA內部產生

2012-05-04 11:42:26 4167

4167

在時分復接通信系統中,位同步是收、發兩端的時鐘頻率必須同頻、同相,這樣在接收端才能正確地判決發送端送來的每一個碼元。為了達到收、發端頻率同頻、同相,在設計傳輸碼型時,一般要考慮傳輸的碼型中應含有發送

2020-07-30 18:02:44 1076

1076

時鐘使能電路是同步設計的重要基本電路,在很多設計中,雖然內部不同模塊的處理速度不同,但是由于這些時鐘是同源的,可以將它們轉化為單一的時鐘電路處理。在FPGA的設計中,分頻時鐘和源時鐘的skew不容易

2020-11-10 13:53:41 4795

4795

7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 1276

1276 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 655

655

摘要:FPGA異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的幾種同步策略。關鍵詞

2009-04-21 16:52:37

FPGA時鐘問題 2010-06-11 15:55:39分類: 嵌入式1.FPGA的全局時鐘是什么?FPGA的全局時鐘應該是從晶振分出來的,最原始的頻率。其他需要的各種頻率都是在這個基礎上利用PLL或者其他分頻手段得到的。

2021-07-29 09:25:57

我們的設計用到了FPGA和AD9789進行CMOS電平的數字通信。fpga的時鐘跟AD9789的時鐘是異步的,不知道這樣的設計會不會導致fpga和ad9789的通信不穩定,如何避免。fpga和ad9789是如何同步的?通信速率fs=18.284MHz,fdac=2.395204GHz。謝謝!

2023-12-21 08:29:25

PART 1

同步是基本需求

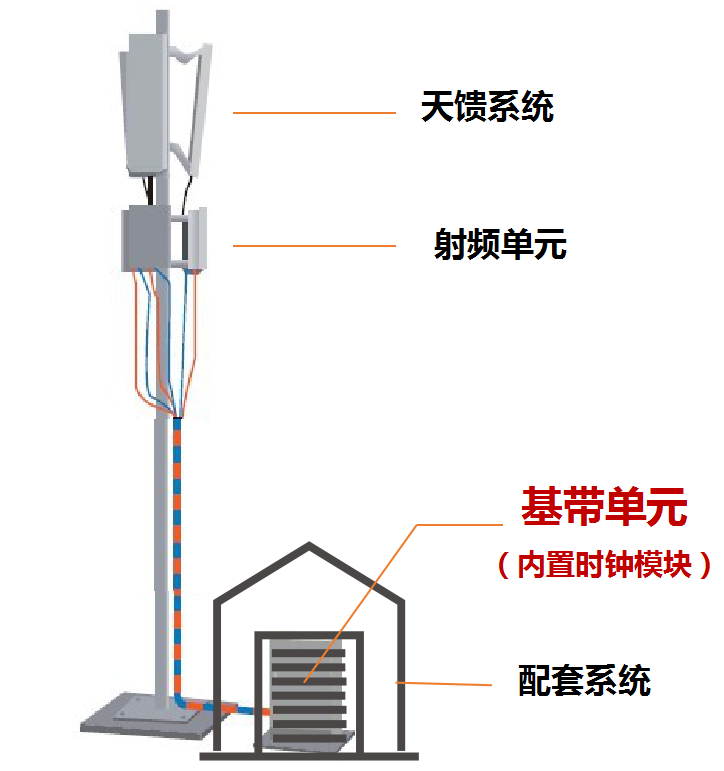

時鐘同步,對于無線網絡來說至關重要。從2G到5G,不同的無線接入技術對頻率同步和相位同步的精度都有著不同的要求。

同步的基本原理和對表類似。

每個

2023-05-10 17:09:50

視頻信號(包括數據與時鐘,其中數據位寬16位,時鐘1位,最高工作頻率148.5MHZ).2.遇到的問題時鐘相對于數據的延時,也就是信號的建立與保持時間在經過FPGA后出現偏移。造成后端的DA不能正確的采集到數據。

2014-02-10 16:08:02

系統中頻率最高的信號; ⑶ 時鐘信號通常是負載最重的信號,所以要合理分配負載。 出于這樣的考慮在 FPGA 這類可編程邏輯器件內部一般都設有數量不等的專門用于系統時鐘驅動的全局時鐘網絡。這類網絡

2012-03-05 14:29:00

拉票第一名,所以直接獲得試用機會項目描述:位同步時鐘提取現在本科階段平時喜歡鉆研,征戰了2016TI杯電子設計競賽,并獲得省二,對FPGA以及Verilog HDL有一定程度的了解,自己通過FPGA

2016-08-29 15:40:44

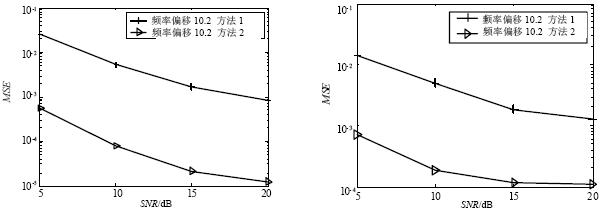

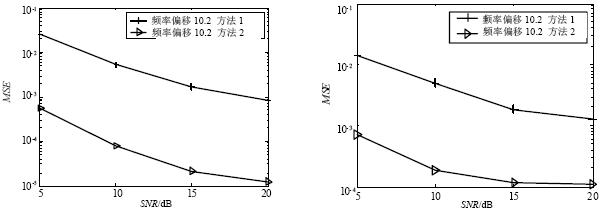

估計法(Kay法)比較具有代表性,它在高信噪比條件下可達到Cramer-Rao界(CRB),并且運算量不大,適于硬件實現。本文以Kay頻率估計法為基礎構建了一種適用于脈沖信號的載波頻率同步環,并通過計算機仿真和FPGA實現來驗證其有效性。

2023-09-20 08:28:04

我在我的同學面前炫耀FPGA是做高速處理的,可是,當人家問我,我的時鐘頻率能達到多少時,我說利用PLL能拉到200MHz,他說,這么低啊?我的手機頻率都是1.5G的呢。我無語。。。后來才了解到,他

2012-03-08 17:11:08

呢?一般根據關系的緊密程度分為“頻率同步”和“相位同步”這兩個級別。頻率同步是指兩個基站的時鐘的變化頻率一致,而相位則不一定一致,可以保持相對固定的差值。

假設兩個基站內部各有一個鐘表,在某一

2023-05-10 16:06:10

?一般根據關系的緊密程度分為“頻率同步”和“相位同步”這兩個級別。頻率同步是指兩個基站的時鐘的變化頻率一致,而相位則不一定一致,可以保持相對固定的差值。

假設兩個基站內部各有一個鐘表,在某一

2023-05-06 12:37:03

將造成30μm的運動誤差。高速加工中心中加工速度為120m/min時,伺服電機之間1μs的時間同步誤差,將造成2μm的加工誤差,影響了加工精度的提高。分布式網絡中節點的時鐘通常是采用晶振+計數器的方式

2019-09-19 08:14:19

YB2414高效率同步降壓轉換器

概述:

YB2414是一款高效率500 kHz同步降壓DC-DC轉換器,能夠提供4A/5A電流。 YB2414可在4.5V至18V的寬輸入電壓范圍內工作,并集成

2024-01-13 12:14:59

必須適當地與所有數據位的到達保持同步。如果接收器使用發射時鐘,可能會要求延遲從發送端到接收端的時鐘信號。 有時設計可能需要一個更高的時鐘頻率來運行FPGA上的邏輯。但是,只有低頻率輸出的時鐘源可以用

2020-04-25 07:00:00

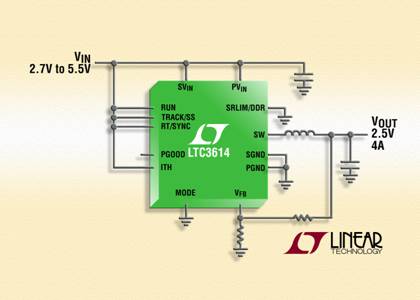

,降低AFE靈敏度。頻率同步的作用頻率同步可用于控制開關諧波的位置,并最小化否則會降低系統靈敏度的開關拍頻率。這種技術經常用于負載點直流調節的開關模式電源(開關電源),其中功率調節器與外部時鐘源同步

2020-01-06 15:50:31

具有外部頻率同步的LTC3728LCUH 5V / 4A,3.3V / 5A穩壓器的典型應用電路。 LTC3728L是雙路高性能降壓型開關穩壓控制器,可驅動所有N溝道同步功率MOSFET級

2020-06-15 09:39:00

演示電路DC1598A是一款固定頻率同步降壓 - 升壓轉換器,具有擴展的輸入和輸出范圍。獨特的4開關單電感架構可在高于,低于或等于輸出電壓的輸入電壓下提供低噪聲和無縫操作

2020-08-10 09:40:04

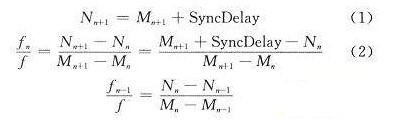

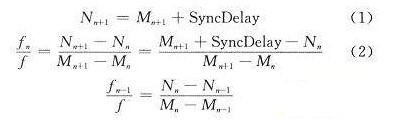

本文研究了一種可對頻率進行動態調整的時鐘,通過對時鐘頻率的動態修正,實現主從時鐘頻率的同步,進而實現時間同步。

2021-04-08 06:23:43

摘要:隨著石油勘探的發展,在地震勘探儀器中越來越需要高精度的同步技術來支持高效采集。基于這種目的,采用FPGA技術設計了一種時鐘恢復以及系統同步方案,并完成了系統的固件和嵌入式軟件設計。通過室內測試

2019-06-18 08:15:35

STEVAL-ISA077V2,基于L6920D的高效率同步整流升壓轉換器演示板。基于L6920D的高效率同步整流升壓轉換器演示板

2020-07-30 07:25:55

我想做多個FPGA的時鐘同步,目前的想法是用一個FPGA的內部時鐘,復制到外接IO口,接到另一個FPGA的外部時鐘引腳,波形有較小的相移但是可以保證同步。想問一下可以復制多次,驅動多個FPGA的同步嗎。對驅動能力有什么要求?其中每一個FPGA都用的是一個EP4CE的最小系統板。

2019-01-21 15:07:41

本文研究了一種可對頻率進行動態調整的時鐘,通過對時鐘頻率的動態修正,實現主從時鐘頻率的同步,進而實現時間同步。

2021-05-10 07:01:08

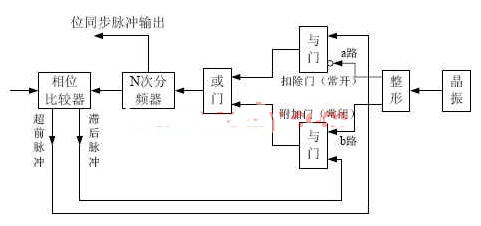

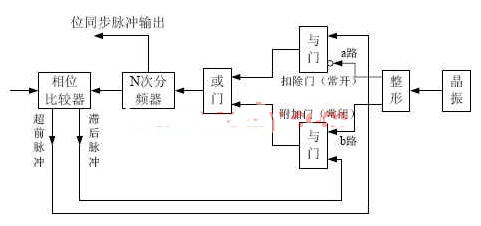

信息。自同步法又可以分為兩種,即開環同步法和閉環同步法。開環法采用對輸入碼元做某種變換的方法提取位同步信息。閉環法則用比較本地時鐘和輸入信號的方法,將本地時鐘鎖定在輸入信號上。閉環法更為準確,但是也更為復雜。那么,我們該怎么利用FPGA設計提取位同步時鐘DPLL?

2019-08-05 06:43:01

方法并沒有從根本上解決時鐘頻率的不同步問題,因此要進一步提高同步精度很困難。 如何設計使主從時鐘頻率同步?這個問題急需考慮!

2019-08-06 06:34:51

靈敏度。頻率同步的作用頻率同步可用于控制開關諧波的放置并最小化切換拍頻,否則會降低系統靈敏度。該技術通常用于開關模式電源(SMPS),用于負載點DC-DC調節,其中功率調節器與外部時鐘源同步。SMPS

2019-03-25 21:49:46

,否則會降低系統靈敏度。該技術通常用于開關模式電源(SMPS)中,以實現負載點DC-DC調節,其中電源調節器與外部時鐘源同步。SMPS因其高效率而被普遍使用,但它們也帶來了獨特的排放挑戰。頻率同步在

2020-11-21 09:50:48

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時鐘的全數字鎖相環設計方法。

2021-05-06 08:00:46

的代碼時,都需要調整采樣時鐘的相位才能夠進行正確的采樣,有時調整相位也采樣不正確。這是采樣時鐘與數據不同步造成的么?我在網上看了一些資料,說可以使用idelay增加時鐘的延時,我的FPGA

2016-08-14 16:58:50

計算FPGA外部引腳的頻率。我需要將其與內部FPGA時鐘同步嗎?內部參考時鐘以60Mhz運行,外部頻率在10khz到15khz之間變化,不同步的外部頻率是否會導致錯誤或問題?以上來自于谷歌翻譯以下

2019-06-18 09:37:29

需要一款小功率同步電機,以及驅動板,去哪里購買比較合適?

2014-09-18 12:00:43

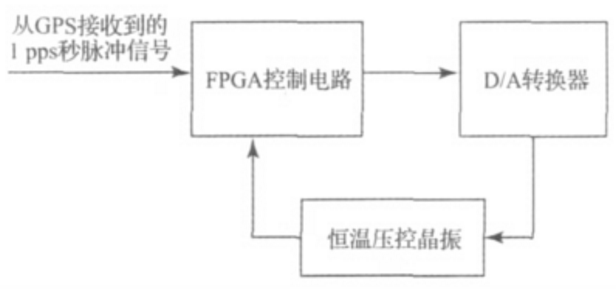

在介紹了GPS 同步時鐘基本原理和FPGA 特點的基礎上,提出了一種基于FPGA 的GPS同步時鐘裝置的設計方案,實現了高精度同步時間信號和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 40

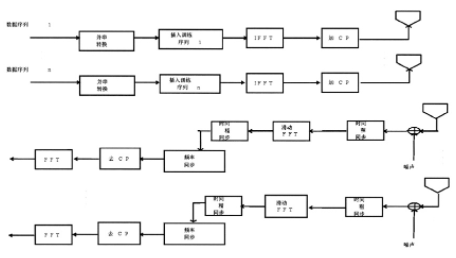

40 FMT系統的頻率同步算法:提出了一種基于訓練符號的FMT系統的頻率同步算法,并分析了其性能.仿真結果表明,采用輔助數據的頻率同步算法,改進了SCA算法,在快衰落環境

2010-03-18 16:22:09 25

25 針對OFDM技術中的載波頻率同步問題,分析了載波頻率偏差對OFDM系統造成的影響,總結了基于IEEE802.11標準的三種常見的頻偏估計算法:基于循環前綴的最大似然算法、基于訓練序列

2010-10-08 16:32:13 18

18 OFDM的頻率同步算法

文中提出的頻率同步方法是在取得時間同步后,將接收的每PN序列長度的數據與本地PN序列作相關,共得L個值,分別為c1

2009-03-01 16:43:00 978

978

基于FPGA的提取位同步時鐘DPLL設計

在數字通信系統中,同步技術是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監測輸入碼元信號,確保收發

2010-01-25 09:36:18 2890

2890

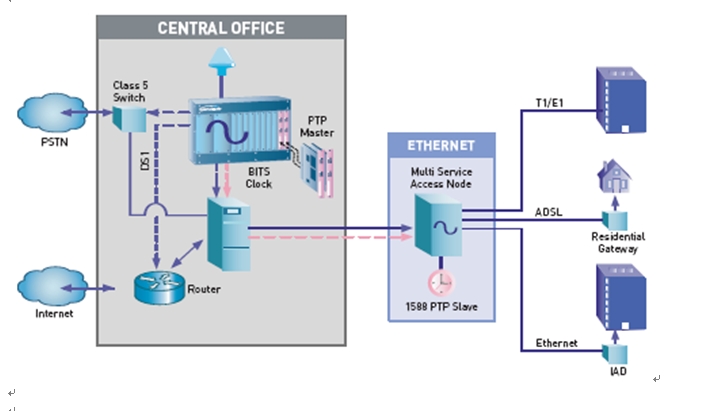

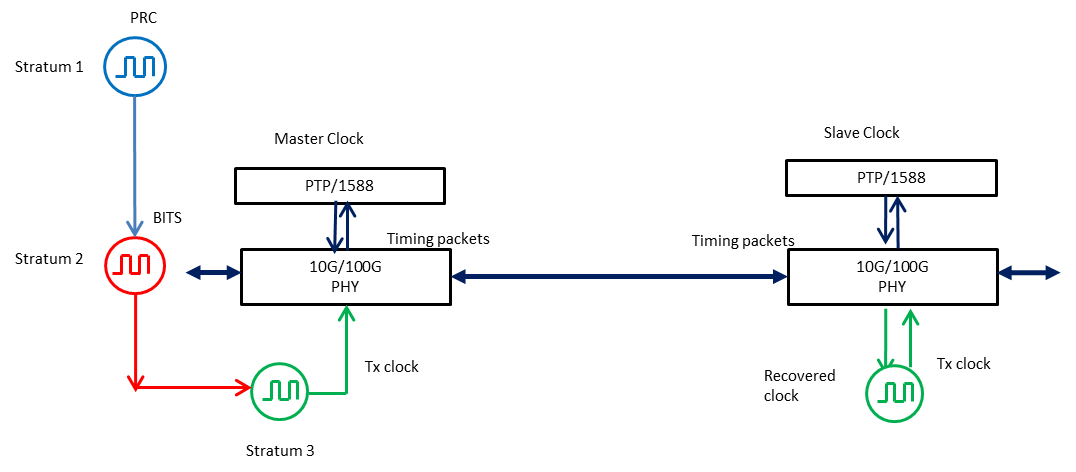

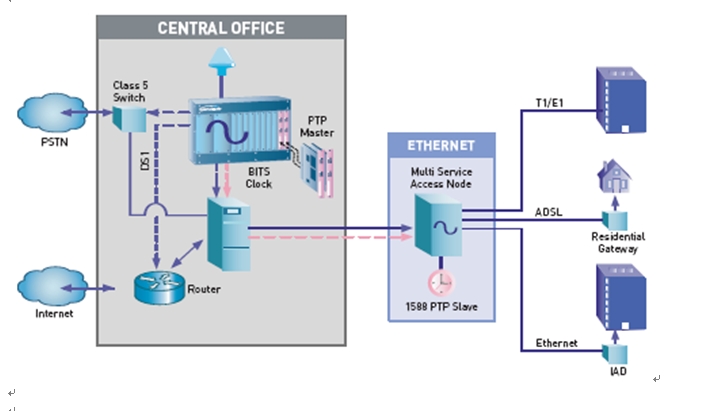

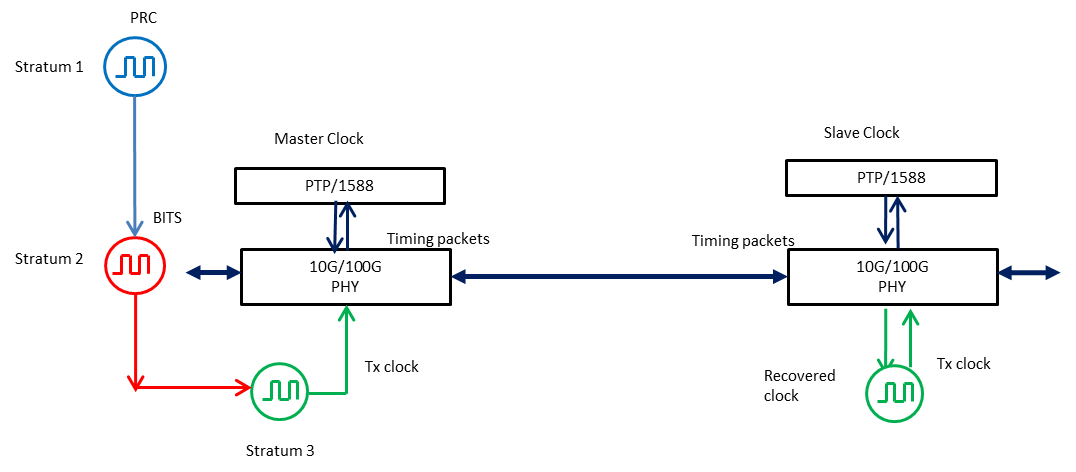

IEEE 1588精密時間協議—分組網絡上的頻率同步

電信網絡正在從電路交換技術快速轉向分組交換技術,以滿足核心網和接入網對帶寬需求的迅速擴大。傳統的電路交換TDM

2010-02-03 09:25:53 4542

4542

同步網時鐘及等級

基準時鐘 同步網由各節點時鐘和傳遞同步定時信號的同步鏈路構成.同步網的功能是準確地將同步定時信號從基

2010-04-03 16:27:34 3661

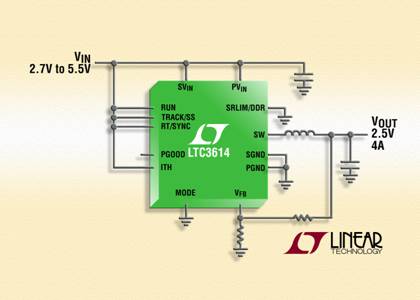

3661 高效率同步降壓型穩壓器LTC3614(Linear)

LTC3614器件采用恒定頻率、電流模式架構,能夠實現高達 4MHz 的開關頻率。低電阻內部開關

2010-04-17 10:21:55 892

892

基于fpga的鎖相環位同步提取電路

該電路如圖所示,它由雙相高頻時鐘

2010-10-08 12:00:23 1483

1483

一,單頻網的同步過程 上一章所談的同頻網的頻率效率及功率效率的代價是實現廣播網內的發射機的同步工作,也就是在單頻網中實現頻率,時間以及比特的三同步。 (1)頻率同步

2011-05-11 08:28:23 14

14 凌力爾特公司 (Linear Technology Corporation) 推出具備非線性控制、差分輸出電壓檢測和時鐘同步功能的固定頻率同步降壓型 DC/DC 控制器 LTC3867

2011-08-13 14:33:37 1211

1211

在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 3472

3472

鑒于電網頻率具有正常波動范圍, 因而實時數據采集構成對電網的電量進行分析、實時監測的關鍵環節。分析了同步采樣和準同步采樣兩種頻率跟蹤技術, 系統采用了同步采樣方法中的硬

2011-10-28 15:40:49 69

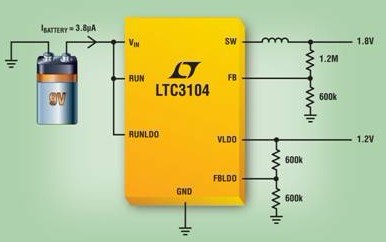

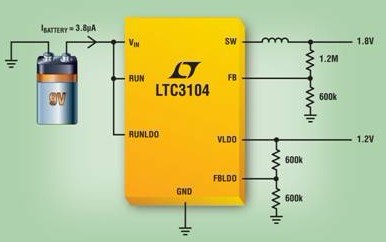

69 凌力爾特公司 (Linear Technology Corporation) 推出 15V、固定頻率同步降壓型轉換器 LTC3103 和 LTC3104,

2011-11-29 17:07:58 1011

1011

FPGA 異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA 異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的

2011-12-20 17:08:35 63

63 永磁同步電機(PMSM)可以用一個與電源頻率同步的恒定速度進行旋轉,而不受負載和線路電壓的影響。電機運行可以保持恒定的,與電源頻率同步的速度,只要轉矩不超過電機的極限運

2012-02-03 17:11:02 0

0 文章結合高精度晶振無隨機誤差和GPS秒時鐘無累計誤差的特點,采用GPS測量監控技術,對高精度晶體振蕩器的輸出頻率進行精密測量和調節,使晶振的輸出頻率同步在GPS系統上,從而提

2012-08-09 14:07:29 5152

5152

2016年1月12日,致力于亞太地區市場的領先半導體元器件分銷商---大聯大控股宣布,其旗下友尚推出業內首款具有頻率同步功能的TI的20A和30A同步DC/DC降壓轉換器---TPS544B25和TPS544C25。

2016-01-12 16:24:54 921

921 致力于亞太地區市場的領先半導體元器件分銷商---大聯大控股宣布,其旗下友尚推出業內首款具有頻率同步功能的TI的20A和30A同步DC/DC降壓轉換器---TPS544B25和TPS544C25

2016-01-13 15:02:32 1298

1298

目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-02-11 11:34:11 4223

4223 時鐘頻率(又譯:時鐘頻率速度,英語:clock rate),是指同步電路中時鐘的基礎頻率,它以“若干次周期每秒”來度量,量度單位采用SI單位赫茲(Hz)。它是評定CPU性能的重要指標。一般來說主頻數字值越大越好。外頻,是CPU外部的工作頻率

2017-11-10 14:21:26 23331

23331

介紹了精密時鐘同步協議(PTP)的原理。本文精簡了該協議,設計并實現了一種低成本、高精度的時鐘同步系統方案。該方案中,本地時鐘單元、時鐘協議模塊、發送緩沖、接收緩沖以及系統打時標等功能都在FPGA

2017-11-17 15:57:18 6196

6196

異步復位同步釋放 首先要說一下同步復位與異步復位的區別。 同步復位是指復位信號在時鐘的上升沿或者下降沿才能起作用,而異步復位則是即時生效,與時鐘無關。異步復位的好處是速度快。 再來談一下為什么FPGA設計中要用異步復位同步釋放。

2018-06-07 02:46:00 1989

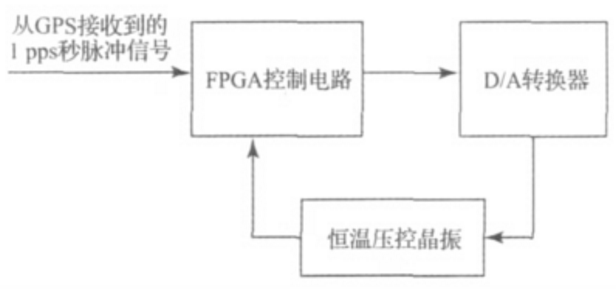

1989 本文主要介紹了基于FPGA的壓控晶振同步頻率控制系統的研究與設計。利用GPS提供的1pps秒脈沖信號,為解決上述問題,在FPGA的基礎上利用干擾秒脈沖信號消除和偏差頻率平均運算等方法,減少外圍電路

2018-03-02 14:55:59 4473

4473

FPGA輸入數據與FPGA內部時鐘的相對相位關系不確定;在時鐘頻率可變的情況下,相對相位關系還會隨頻率變化。在FPGA內部一般采用D觸發器實現對輸入數據的采樣。為了避免亞穩態 ,D觸發器要求輸入數據相對時鐘

2018-08-02 16:03:00 1858

1858

分布式網絡中節點的時鐘通常是采用晶振+計數器的方式來實現,由于晶振本身的精度以及穩定性問題,造成了時間運行的誤差。時鐘同步通常是選定一個節點時鐘作為主時鐘,其他節點時鐘作為從時鐘。主節點周期性地通過

2019-05-05 08:17:00 11795

11795

基于FPGA的數字系統設計中大都推薦采用同步時序的設計,也就是單時鐘系統。但是實際的工程中,純粹單時鐘系統設計的情況很少,特別是設計模塊與外圍芯片的通信中,跨時鐘域的情況經常不可避免。如果對跨時鐘

2018-09-01 08:29:21 5302

5302

交換網絡提供更高質量的同步與定時機制。傳統以太網沒有內置時鐘的分布能力,同步以太網對現有以太網做了一種擴展,類似TDM網絡在物理層發布時鐘,實現了設備間時鐘頻率同步。但是還有一些應用需要時間上的同步

2020-01-13 16:29:21 3387

3387

PART1同步是基本需求時鐘同步,對于無線網絡來說至關重要。從2G到5G,不同的無線接入技術對頻率同步和相位同步的精度都有著不同的要求。

2020-10-18 09:41:27 5731

5731

對于 FPGA 來說,要盡可能避免異步設計,盡可能采用同步設計。 同步設計的第一個關鍵,也是關鍵中的關鍵,就是時鐘樹。 一個糟糕的時鐘樹,對 FPGA 設計來說,是一場無法彌補的災難,是一個沒有打好地基的樓,崩潰是必然的。

2020-11-11 09:45:54 3656

3656 PLL 是一種用來同步輸入信號和輸出信號頻率和相位的相位同步電路,也可用來實現時鐘信號的倍頻(產生輸入時鐘整數倍頻率的時鐘)。在 FPGA 芯片上,PLL 用來實現對主時鐘的倍頻和分頻,并且 PLL

2020-11-16 17:04:44 3292

3292 區域(Region):每個FPGA器件被分為多個區域,不同的型號的器件區域數量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA

2020-12-09 14:49:03 20

20 界。應用數字下變頻技術和Kay算法實現載波頻率的精確估計。設計實例的仿真結果表明了該環路的有效性,環路可在短對同內完成高精度的載波頻率同步。

2021-02-05 17:35:53 36

36 傳統的異步采集方法會影響采集到的功耗信息的信噪比,降低功耗分析的成功率。針對異步采集的問題提出一種新的時鐘同步功耗信息采集方法。該采集方法基于現場可編程門陣列(FPGA)的時鐘同步采集平臺

2021-03-31 15:50:21 6

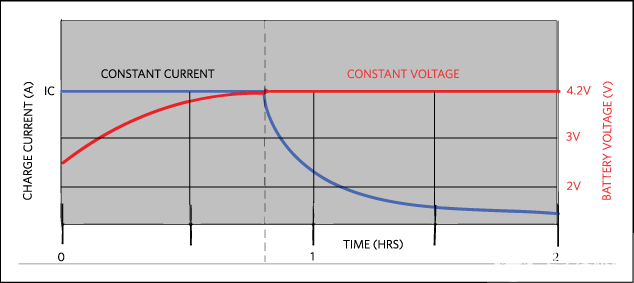

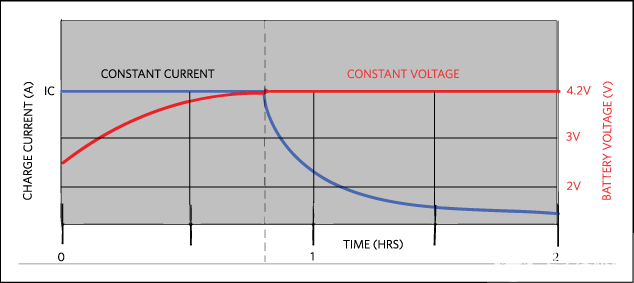

6 電子發燒友網為你提供帶有頻率同步的電池充電電路設計資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-22 08:46:26 2

2 LTM4608A:低VIN,8A DC/DCμ模塊(電源模塊)穩壓器,帶跟蹤、余量和頻率同步數據表

2021-04-22 17:10:08 8

8 對于一個設計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預測的時鐘。只要可能就應盡量在設計項目中采用全局時鐘。FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。

2021-04-24 09:39:07 5827

5827

LTM4618:6A帶跟蹤和頻率同步功能的DC/DCμ模塊(電源模塊)穩壓器數據表

2021-04-27 13:01:56 11

11 LTM4608:8A,低VIN DC/DCμ模塊(電源模塊),帶跟蹤、余量、多相和頻率同步數據表

2021-05-13 16:22:50 1

1 對MIMO-OFDM系統來說,時間同步方面,接收端需要對各個天線上的信號分別進行延時估計和調整。頻率同步方面,接收端需要對各個天線上的信號分別進行頻率偏移估計和補償。傳統的MIMO-OFDM同步算法

2021-06-17 16:34:29 2266

2266

同步,從字面意思上看,是指兩個或兩個以上隨時間變化的量在變化過程中保持一定的相對關系。到底是怎么樣的相對關系呢?一般根據關系的緊密程度分為“頻率同步”和“相位同步”這兩個級別。頻率同步是指兩個基站

2021-09-28 15:43:23 7417

7417 SyncE。同步以太網通過從串行數據碼流中恢復出發送端的時鐘,從而實現網絡時鐘同步。但SyncE不能提供時間同步。IEEE1588v2是統一提供時間同步和頻率同步的方法,能適合于不同傳送平臺的時頻傳

2022-01-15 14:35:31 2389

2389 晶振頻率是晶體振蕩器的固有頻率,而時鐘頻率是以時間為準的振蕩頻率,一個時鐘周期等于兩個振蕩周期,所以晶振頻率等于2倍時鐘頻率。那么這兩個頻率之間有什么區別?

2022-01-29 16:57:00 9435

9435 CDC(不同時鐘之間傳數據)問題是ASIC/FPGA設計中最頭疼的問題。CDC本身又分為同步時鐘域和異步時鐘域。這里要注意,同步時鐘域是指時鐘頻率和相位具有一定關系的時鐘域,并非一定只有頻率和相位相同的時鐘才是同步時鐘域。異步時鐘域的兩個時鐘則沒有任何關系。這里假設數據由clk1傳向clk2。

2022-05-12 15:29:59 1334

1334 業界首款 20-A 和 30-A 同步 DC/DC 降壓轉換器具有頻率同步功能,可實現低噪聲和降低的 EMI/EMC,以及用于自適應電壓調節 (AVS) 的 PMBus 接口。

2022-08-29 09:25:09 430

430 本文描述了在以太網絡上時鐘頻率同步特性的需求和技術關鍵點以及華為數通CX產品的實現。

2022-10-24 15:31:37 0

0 工作頻率,這確實是一個很重要的方法,今天我想進一步去分析該如何提高電路的工作頻率。 我們先來分析下是什么影響了電路的工作頻率。 我們電路的工作頻率主要與寄存器到寄存器之間的信號傳播時延及clock skew 有關。在 FPGA 內部如果時鐘走

2022-11-16 12:10:02 713

713 該電路是一款具有頻率同步功能的高壓、高效率、開關模式電池充電器。該電路適用于對諧波發射敏感的電池供電應用。

2023-01-11 10:01:35 529

529

本節介紹小功率同步電機的基本概念本節介紹永磁式、磁阻式、磁滯式同步電機的結構、原理、機械特性、優缺點本節介紹電磁減速同步電機的結構、原理文章

主要作為發電機運行(絕大部分電都是由同步發電機發出來

2023-03-28 09:58:04 0

0 提供時間同步和頻率同步的方法,能適合于不同傳送平臺的時頻傳送,既可以基于1588v2的時間戳以基于分組的時間傳送(TOP)方式單向傳遞頻率,也可使用IEEE1588v2的協議實現時間同步。

2023-03-30 09:38:09 908

908

時鐘信號的同步 在數字電路里怎樣讓兩個不同步的時鐘信號同步? 在數字電路中,時鐘信號的同步是非常重要的問題。因為在信號處理過程中,如果不同步,就會出現信號的混淆和錯誤。因此,在數字電路中需要采取一些

2023-10-18 15:23:48 771

771 fpga與dsp通訊怎樣同步時鐘頻率?dsp和fpga通信如何測試? 在FPGA與DSP通訊時,同步時鐘頻率非常重要,因為不同的設備有不同的時鐘頻率,如果兩者的時鐘頻率不同步,會導致通訊數據的錯誤

2023-10-18 15:28:13 1060

1060 。 一、頻率同步 在傳送網中,頻率同步是指網絡中的各個節點之間的時鐘頻率保持一致,以便實現數據傳輸的精確同步。在頻率同步的實現過程中,一般采用以下兩種方法: 1.1. 時鐘信號同步 傳送網中的設備一般都有自己的時鐘源,通過時鐘

2024-01-16 14:42:48 228

228 USB設備之間是怎么同步時鐘的?是所有USB設備的時鐘頻率都是一致的嗎? USB設備之間的時鐘同步是通過USB協議中的幀同步機制實現的。USB設備的時鐘頻率并不一定完全一致,但是USB協議通過

2024-01-16 14:42:52 485

485 晶振頻率和時鐘頻率本質上有何區別呢?時鐘頻率有什么作用? 晶振頻率和時鐘頻率是兩個相關但又有所不同的概念。下面我們將逐一介紹這兩個概念的含義、區別和作用。 首先,我們來了解晶振頻率。晶振是一種

2024-01-24 16:11:35 307

307

![]()

電子發燒友App

電子發燒友App

評論