如今的智能產品越來越多地需要將傳統的實時嵌入式設計需求與要求更高的應用級軟件結合在一起。除了更大的計算負載外,這些產品還需要支持通過先進的媒體服務(如觸摸屏、高分辨率 3D 圖形和圖像傳感器)與用戶交互。

隨著需求的擴大,開發人員在減小功耗、成本和系統尺寸方面所面臨的壓力也更大,因此不得不尋找更有效的方法來替代傳統的多子系統設計。

本文將討論這些設計需求的演變,以及到目前為止,處理器是如何滿足這些需求的。然后將介紹并展示如何使用 NXP Semiconductors 的新型處理器。這些處理器為開發人員提供了一種更簡單的滿足這一不斷增長的需求的解決方案,讓設計能夠同時處理實時計算和應用計算要求。

升級處理器并保持代碼投資

開發人員通常使用與特定應用處理要求匹配的多核微處理器來升級其設計的計算能力。使用這種方法,開發人員既可實現性能提升,又可保持與現有代碼庫的兼容性,以及相應器件系列的使用體驗。

例如,使用 NXP i.MX 6 應用處理器系列,設計人員不僅可以保持代碼兼容性,而且能夠使用配備單個 Arm? Cortex?-A9 應用處理器內核的 i.MX 6Solo、配備兩個內核的 i.MX 6Dual 或集成四個內核的 i.MX 6Quad,來提升性能。

這種升級應用處理能力的需求,也在曾被視為傳統嵌入式系統的設計中快速發展。對于這些設計,產品制造商希望為家用電器、工業控制器、醫療儀器等設備增加智能性。為此,半導體供應商提供了異構多核處理 (HMP) 器件,這些器件可同時集成應用處理器內核和嵌入式處理器內核。例如,NXP i.MX 8M 系列結合了多至四個 Arm Cortex-A53 應用處理器內核,以及一個 Arm Cortex-M4 嵌入式處理器內核。

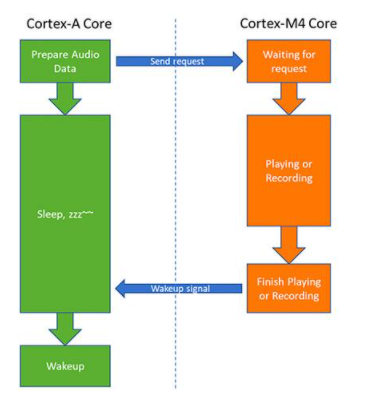

只需使用這一單個器件,開發人員就可以打造出智能音頻產品。這些產品可充分利用應用處理器來增強、過濾或以其他方式處理音頻數據。然后,音頻系統依靠嵌入式處理器內核來執行播放所需的實時功能(圖 1)。在嵌入式處理器執行實時操作期間,應用處理器可以置于低功耗模式,從而降低整體功耗。當實時操作完成時,嵌入式處理器只需向應用處理器發送喚醒信號。

圖 1:異構多核處理器尤其適用于智能產品設計,既可提供高性能計算與實時功能,同時又不影響緊張的功率預算。(圖片來源:NXP Semiconductors)

除了異構內核外,NXP i.MX 8M 系列還集成了各種多媒體資源,包括 4K 視頻處理單元 (VPU) 和高性能 3D 圖形處理單元 (GPU)。因此,該系列可以為越來越多的視頻及 3D 圖形智能產品提供有效解決方案。

盡管如此,開發人員在構建高性能系統時,仍然面臨著電池及線路供電系統對低功耗需求日益增長的挑戰。為應對這一挑戰,NXP i.MX 8M Mini 處理器系列采用先進的半導體工藝技術制造,可解決高性能混合負載處理與功耗降低之間的需求矛盾。

高性能、低功耗計算

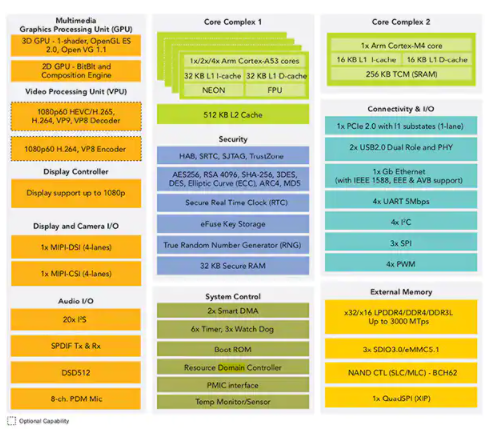

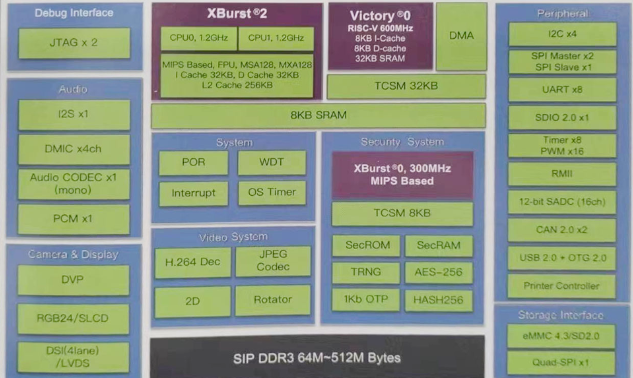

NXP i.MX 8M Mini 處理器屬于首款采用 14 納米 (nm) FinFET 工藝技術制造的 NXP HMP 系列,專為新興的工業和物聯網 (IoT) 系統而設計,這些系統對高性能、高安全性和低功耗都提出了要求。與 NXP i.MX 8M 系列一樣,NXP i.MX 8M Mini 也集成了一個 Arm Cortex-M4 嵌入式處理內核,以及最多四個 Arm Cortex-A53 應用處理內核,還有一個全面的安全子系統以及多個連接和 I/O 選項(圖 2)。

圖 2:NXP i.MX 8M Mini 處理器結合了最多四個 Arm Cortex-A53 應用處理器內核和一個 Arm Cortex-M4 嵌入式內核,還有新興智能產品所需的全套安全、多媒體、系統功能以及 I/O 接口。(圖片來源:NXP Semiconductors)

為了支持嵌入式設計,與之前的 NXP i.MX 8M 相比,i.MX 8M Mini 減少了某些 I/O 通道的數量及其多媒體子系統的高分辨率能力。例如,i.MX 8M Mini 器件包括商業版 (MIMX8MM6DVTLZAA) 和工業版 (MIMX8MM6CVTKZAAA),提供一個單一著色器 GPU 和一個 1080p 60 赫茲 (Hz) VPU,而 NXP i.MX 8M 則提供四著色器 GPU 和 4K VPU。i.MX 8M Mini 系列的其他成員包括商業版 (MIMX8MM5DVTLZAA) 和工業版 (MIMX8MM5CVTKZAA) 器件,則完全去除了 VPU。與早期的 NXP i.MX 8M 一樣,i.MX 8M Mini 能夠讓開發人員利用處理器對多種存儲器類型的支持(包括雙倍數據速率 3 低電壓 (DDR3L)、DDR4 和低功耗 DDR4 (LPDDR4)),實現性能與成本之間的進一步平衡。

降低功耗

為了進一步優化性能和功耗,開發人員可利用 NXP i.MX 8M Mini 功能,以自動或編程方式切換到低功耗工作模式。在一定條件下,應用內核可以自動切換到空閑模式,并且關閉 GPU、VPU 和應用內核,同時對大多數內部邏輯進行時鐘選通,但保留對 L2 數據緩存的供電。在此模式下,Arm Cortex-M4 內核仍可繼續運行,以執行更多傳統嵌入式處理任務,如傳感器數據采集等。

掛起模式是最省電的模式,通過同時禁用用于管理存儲器接口的雙倍數據速率控制器 (DDRC),延長空閑狀態下功耗降低的時間。最后,安全非易失性存儲 (SNVS) 模式只保留對 SNVS 邏輯和實時時鐘的供電。

i.MX 8M 中采用的 14 nm FinFET 工藝技術具有功耗降低特性,在掛起和 SNVS 模式下表現尤為明顯。在采用 FinFET 的 i.MX 8M Mini 中,掛起模式的功耗大約為 7.81 毫瓦 (mW)。而在早期的 i.MX 8M 中,功能類似的模式(稱為深度休眠模式)消耗 197 mW。類似的功耗降低也發生在 SNVS 模式,在該模式下,i.MX 8M Mini 的功耗約為 0.11 mW,而早期的 i.MX 8M 功耗約為 17 mW。

像 i.MX 8M Mini 這樣的復雜器件具有大量的功能塊和微調工作模式,使工程師面臨諸多嚴格的實現要求。與其他同類器件一樣,i.MX 8M Mini 也依賴多個功率域來優化電源管理和效率。要啟動和關閉這些器件,必須嚴格遵照指定的上電和斷電順序。

對 i.MX 8M Mini 上電時,首先為 SNVS 存儲體中的 GPIO 前級驅動器加電,通常為 1.8 伏。在 2 毫秒 (ms)(最多 2.4 ms)內,必須為 SNVS 內核邏輯加電,通常為 0.8 伏。隨后,再通過 12 個步驟,按順序將特定信號或電力供給 i.MX 8M Mini 的各個引腳,每一步按 0.015 ms 到 20 ms 間隔定時進行。

為器件斷電的順序正好相反,但是連續步驟之間的延遲均為 10 ms。無論是哪一種情況,若不遵守這些準則,都可能使器件無法啟動,導致上電期間電流過大,或者在最壞的情況下,會造成器件發生不可逆轉的損壞。

處理器的 PC 板物理設計也有自身的嚴格要求。對于處理器 486 焊球 14 x 14 毫米 (mm) 封裝的布局,NXP 建議使用至少 8 層的 PC 板層疊結構,并分配足夠的層專門用于電源軌,以滿足電流電阻 (IR) 下降規范的要求。與此同時,布局工程師必須確保高速線路上的串擾最小,包括受支持、以 1.5 千兆赫 (GHz) 和 3,000 百萬次/秒 (MT/s) 速度運行的存儲器器件線路。

快速開發

為幫助工程師快速開始應用開發或加快定制硬件設計的開發,NXP 推出了 NXP i.MX 8M Mini EVK(評估套件)和相關的參考設計(圖 3)。該評估套件以基板和系統級模塊 (SOM) 板形式交付,提供了一個完整的系統,包括外部 LPDDR4 存儲器和閃存,以及 USB 和其他接口。

圖 3:NXP i.MX 8M Mini EVK 板組提供了一個完整的系統平臺,用于立即評估 i.MX 8M Mini 處理器,以及快速開發異構多核處理器應用。(圖片來源:NXP Semiconductors)

除千兆位以太網外,該套件還包含 Wi-Fi 和藍牙連接選項。提供的擴展板包括 MINISASTOCSI 相機模塊和 MX8-DSI-OLED1 有機發光二極管 (OLED) 觸摸屏,用于幫助進行視頻和顯示應用設計。

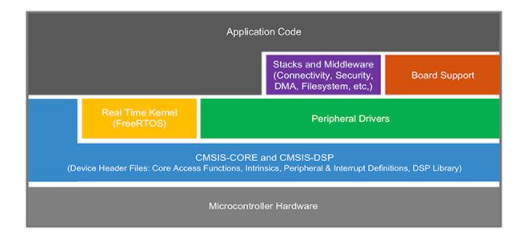

借助用于嵌入式 Linux? 和嵌入式 Android? 操作環境的可用預建鏡像,開發人員可以立即使用該套件評估 i.MX 8M Mini 處理器,并運行樣例應用程序。對于構建自己的軟件應用的開發人員,NXP 免費提供 MCUXpresso 軟件開發工具包 (SDK),該工具包提供了一整套軟件組件,用于構建典型的高性能嵌入式應用(圖 4)。

圖 4:MCUXpresso 軟件開發工具包 (SDK) 架構由整套軟件層組成,包括驅動程序、板級支持包,以及開發大多數嵌入式應用所需的可選組件。(圖片來源:NXP Semiconductors)

使用 NXP 的在線 MCUXpresso SDK Dashboard,開發人員可以針對 GCC Arm Embedded 工具鏈或用于 Arm 的 IAR Embedded Workbench 進行 SDK 配置,還可以添加可選的中間件組件,包括 Arm Cortex 微控制器軟件接口標準 (CMSIS) DSP 庫和 Amazon FreeRTOS。配置后的 SDK 分發包將包含 Arm 標準庫、外設驅動程序、用于 FreeRTOS 的外設驅動程序包裝器,以及一套齊全的軟件樣例。在 SDK 分發包的軟件樣例中,有一對應用程序演示了一種關鍵的信息交換設計模式,該模式是實現異構計算的基礎。

在任何多核計算環境中,單獨的處理器都需要有效的機制來傳遞請求和共享數據。對于 i.MX 8M Mini EVK 應用,NXP 使用的是 RPMsg-Lite——遠程處理器消息傳遞 (RPMsg) 協議的精簡版。RPMsg 協議是開放式非對稱多處理 (OpenAMP) 框架項目的組成部分,旨在為異構多核系統中多核之間的通信提供標準接口。NXP 的 RPMsg-Lite 解決了小型嵌入式系統中的資源限制,縮小了封裝尺寸,并取消了與這些系統不一致的功能。

在 SDK 分發包中,樣例應用程序 rpmsg_lite_pingpong_rtos 演示了一次簡單的交換,即使用 RPMsg-Lite 實現不同處理器之間的簡單 ping-pong 交互(清單 1)。在為另一個“遠程”處理器創建 RPMsg 隊列 (my_queue) 和端點 (my_ept) 后,“主機”應用處理器向遠程內核發送信號。在收到來自遠程內核的握手響應后,主機處理器將開始執行一個循環,該循環使用阻塞策略等待遠程內核的“ping”消息,然后再發送自己的“pong”響應。

void app_task(void *param) {

。..my_rpmsg = rpmsg_lite_remote_init((void *)RPMSG_LITE_SHMEM_BASE, RPMSG_LITE_LINK_ID, RL_NO_FLAGS); while (!rpmsg_lite_is_link_up(my_rpmsg))

;

PRINTF(“Link is up!\r\n”);

my_queue = rpmsg_queue_create(my_rpmsg);

my_ept = rpmsg_lite_create_ept(my_rpmsg, LOCAL_EPT_ADDR, rpmsg_queue_rx_cb, my_queue);

ns_handle = rpmsg_ns_bind(my_rpmsg, app_nameservice_isr_cb, NULL);

rpmsg_ns_announce(my_rpmsg, my_ept, RPMSG_LITE_NS_ANNOUNCE_STRING, RL_NS_CREATE);

PRINTF(“Nameservice announce sent.\r\n”);

/* Wait Hello handshake message from Remote Core.*/

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, helloMsg, sizeof(helloMsg), NULL, RL_BLOCK);

while (msg.DATA 《= 100)

{ PRINTF(“Waiting for ping.。.\r\n”);

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, (char *)&msg, sizeof(THE_MESSAGE), NULL,

RL_BLOCK);

msg.DATA++; PRINTF(“Sending pong.。.\r\n”);

rpmsg_lite_send(my_rpmsg, my_ept, remote_addr, (char *)&msg, sizeof(THE_MESSAGE), RL_BLOCK);

} PRINTF(“Ping pong done, deinitializing.。.\r\n”);

rpmsg_lite_destroy_ept(my_rpmsg, my_ept);

my_ept = NULL;

rpmsg_queue_destroy(my_rpmsg, my_queue);

my_queue = NULL;

rpmsg_ns_unbind(my_rpmsg, ns_handle);

rpmsg_lite_deinit(my_rpmsg);

msg.DATA = 0; 。..}

列表 1:這個片段來自 MCUXpresso 軟件開發工具包提供的樣例代碼,演示了在異構多核處理器中不同處理器間實現交互的基本設計模式。(代碼來源:NXP Semiconductors)

開發人員可以基于這一簡單的交換,輕松創建完整操作,以跨越多個處理器分配任務執行。另一個樣例應用程序 sai_low_power_audio 實質上將 RPMsg-Lite 用作更高層簡化型實時消息傳遞 (SRTM) 應用協議的低級數據鏈路層。在此應用程序中,Arm Cortex-A53 處理器使用該 SRTM 協議請求 Arm Cortex-M4 處理器播放共享存儲器中的音頻文件。在控制了共享緩沖區之后,M4 將執行多項操作,最終執行智能直接存儲器訪問 (SDMA) 事務,以將數據傳輸到適當的代碼,最后傳輸到串行音頻接口 (SAI) 進行音頻輸出。在執行這些操作期間,A53 內核可以進入低功耗模式。盡管在設計上比 ping-pong 應用程序更復雜,但 sai_low_power_audio 樣例應用程序演示了開發人員如何能夠使用異構多核處理器來實現性能最大化,同時充分降低智能產品的功耗。

總結

智能產品正在將傳統的實時嵌入式處理系統與強大的應用處理能力結合在一起。然而,開發人員需要在滿足這些處理要求的同時,還要滿足人們對于電池和線路供電型系統中低功耗產品的持續預期。

NXP i.MX 8M Mini 應用處理器采用先進的半導體工藝制造,既可提供高性能異構多核處理能力,又能保持低功耗。使用 NXP i.MX 8M Mini 器件,開發人員可以更好地滿足日益復雜的智能產品中的嵌入式系統設計對于高性能計算的新興需求。

電子發燒友App

電子發燒友App

評論