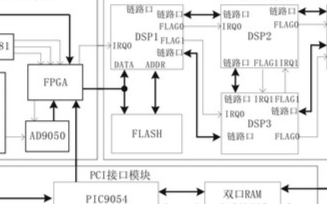

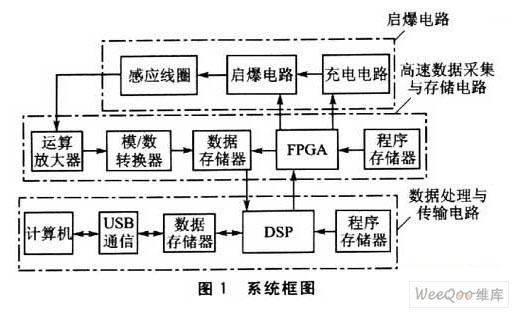

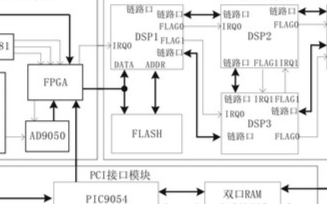

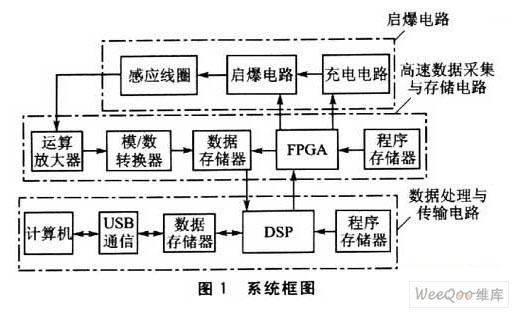

該系統(tǒng)可以完成圖像的采集、處理和顯示,從而實(shí)現(xiàn)目標(biāo)識(shí)別與跟蹤的智能信號(hào)處理。該系統(tǒng)是對(duì)攝像機(jī)數(shù)字,模擬兩路視頻數(shù)據(jù)進(jìn)行采集,處理后通過PCI總線在PC機(jī)上顯示出來。整個(gè)系統(tǒng)主要由視頻信號(hào)采集模塊、DSP圖像處理模塊、PCI接口模塊三個(gè)部分組成(圖1)。

2021-01-07 09:58:50 2687

2687

使用XINTF總線進(jìn)行通訊進(jìn)行數(shù)據(jù)傳輸,DSP,F(xiàn)PGAIO全部引出 這樣就可以很容易的將主控板融入到嵌入式系統(tǒng)中,需要什么外設(shè)可以直接裝在主控板上,可以用來控制電機(jī),可以用來做數(shù)據(jù)采集系統(tǒng)。將外部

2016-07-18 16:59:22

DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,F(xiàn)PGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計(jì)的過程中遇到

2016-07-18 16:53:28

DSP28335+FPGA+AD7606的數(shù)據(jù)采集系統(tǒng),DSP采用TI公司的TMS320F28335,F(xiàn)PGA使用 ALTERA的Cyclone3 的 EP3C5E144C8N在設(shè)計(jì)的過程中遇到

2016-07-18 17:13:01

TI公司 DSP5000系列強(qiáng)大的音頻壓縮能力,語(yǔ)音應(yīng)用得到了較大的發(fā)展。因此,基于 DSP的聲音采集系統(tǒng)的設(shè)計(jì)與開發(fā)具有重要的現(xiàn)實(shí)意義。

2019-09-20 06:41:05

外接速率更高的外設(shè),適合用于線陣CCD的數(shù)據(jù)采集。在USB2.0版本中,增加了一種高速模式,其數(shù)據(jù)傳輸率最高可以達(dá)到480Mb/s,完全可以滿足高速CCD數(shù)據(jù)采集系統(tǒng)的需要。2 接口硬件組成本系統(tǒng)選用高速

2018-12-03 15:18:20

基于DSP5509 的數(shù)據(jù)采集系統(tǒng)系統(tǒng)采用了DSP + FPGA 的雙核結(jié)構(gòu),由CMOS 感光芯片OV7620 采集圖像,得到數(shù)據(jù)源, FPGA 作為輔助處理器,控制部分外圍器件并協(xié)助采集

2009-04-28 10:47:02

申請(qǐng)理由:我是一名在讀研究生,目前在做數(shù)據(jù)采集系統(tǒng),采用的是STM32,做成之后感覺系統(tǒng)不是很穩(wěn)定,精度也不高,后來查了資料,原來DSP更適合做信號(hào)處理分析這一類別,所以申請(qǐng)一下。項(xiàng)目描述

2015-09-10 11:18:52

申請(qǐng)理由:借助此平臺(tái)完成數(shù)據(jù)的處理項(xiàng)目描述:高速ADC+高密度FPGA+高性能DSP,其中FPGA主要負(fù)責(zé)高速數(shù)據(jù)緩存,并對(duì)整個(gè)高速數(shù)據(jù)采集系統(tǒng)進(jìn)行控制;DSP器件擁有很強(qiáng)的數(shù)字信號(hào)處理能力和良好

2015-11-06 10:01:48

測(cè)量速度和精度。 系統(tǒng)總體設(shè)計(jì)方案 本文提出了一種基于LABVIEW的USB接口高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì),充分利用DSP豐富的片上外設(shè)以及高性能的數(shù)字信號(hào)處理能力,將采集的數(shù)據(jù)經(jīng)DSP處理后通過

2014-12-16 11:32:57

。網(wǎng)絡(luò)接口模塊為多核系統(tǒng)通訊資源接口。2.1 幀格式定義 圖3所示為兩種協(xié)議的數(shù)據(jù)格式定義。以太網(wǎng)IP核用戶接口數(shù)據(jù)以幀格式定義數(shù)據(jù)的輸出或輸入,數(shù)據(jù)寬度為8位,幀數(shù)據(jù)長(zhǎng)度范圍為64~1 518

2019-06-03 05:00:02

關(guān)于DSP核信號(hào)采集系統(tǒng)通訊接口原理及設(shè)計(jì)你想知道的都在這

2021-05-31 06:38:06

處理器選擇 視頻系統(tǒng)通常包括視頻信號(hào)的采集、處理和輸出。其中最核心的部分是處理部分。對(duì)于4路720×576標(biāo)清格式的PAL制式視頻采集系統(tǒng)及1路720×576標(biāo)清格式的PAL制式視頻輸出,系統(tǒng)輸入

2011-05-03 11:37:38

另一類數(shù)據(jù)密集處理型芯片DSP。DSP由于其特殊的結(jié)構(gòu)、專門的硬件乘法器和特殊的指令,使其能快速地實(shí)現(xiàn)各種數(shù)字信號(hào)處理及滿足各種高實(shí)時(shí)性要求。隨著現(xiàn)代嵌入式系統(tǒng)的復(fù)雜度越來越高,操作系統(tǒng)已成為嵌入式

2019-07-23 07:37:33

基于DSP核控制的SoC系統(tǒng)是由哪些部分組成的?基于DSP核控制的SoC系統(tǒng)該如何去設(shè)計(jì)?

2021-06-18 09:42:47

管理。這樣充分利用DSP對(duì)數(shù)字信號(hào)高速處理的優(yōu)勢(shì),提高信號(hào)處理系統(tǒng)的實(shí)時(shí)性和穩(wěn)定性。本文以TMS320VC5402 DSP為例,給予說明。1 系統(tǒng)的硬件設(shè)計(jì)1.1 PCI接口芯片

2018-12-17 11:29:06

基于DSP的圖像采集系統(tǒng)的硬件設(shè)計(jì)基于DSP的圖像采集系統(tǒng)的軟件設(shè)計(jì)

2021-06-01 06:27:34

基于C55x DSP核芯片實(shí)現(xiàn)基帶信號(hào)處理系統(tǒng)的設(shè)計(jì)

2020-12-21 06:19:01

(Field Programmable Gate Array,F(xiàn)PGA)由于其設(shè)計(jì)靈活、速度快,在數(shù)學(xué)專用集成電路的設(shè)計(jì)中得到廣泛的應(yīng)用。數(shù)字信號(hào)處理(DSP)的理論與實(shí)現(xiàn)手段獲得了快速發(fā)展,已成為當(dāng)代發(fā)展最快

2019-08-30 06:45:55

在分析某型飛機(jī)MILSTD1553B數(shù)據(jù)總線系統(tǒng)構(gòu)成的基礎(chǔ)上,結(jié)合其通信協(xié)議與其消息傳輸格式,建立了某型飛機(jī)總線系統(tǒng)通訊層次結(jié)構(gòu),并運(yùn)用FPGA和DSP技術(shù)設(shè)計(jì)了此型飛機(jī)總線系統(tǒng)通訊軟件。

2019-09-20 06:32:59

FPGA+DSP構(gòu)成的光纖傳感信號(hào)實(shí)時(shí)處理系統(tǒng)的硬件及軟件設(shè)計(jì).并針對(duì)載波相位延遲造成的解調(diào)信號(hào)幅度衰減提出了解決方法。本系統(tǒng)具有高速實(shí)時(shí)數(shù)據(jù)運(yùn)算能力。可廣泛應(yīng)用于多路數(shù)據(jù)采集處理等領(lǐng)域,可升級(jí)能力強(qiáng),應(yīng)用前景

2021-07-05 11:23:33

、中斷、錯(cuò)誤和核特性標(biāo)志等控制信息,也是IP核與系統(tǒng)間交換控制和狀態(tài)信息的手段,可以同請(qǐng)求/響應(yīng)信號(hào)異步,但與時(shí)鐘上升沿同步。測(cè)試信號(hào)支持掃描、時(shí)鐘控制和JTAG。OCP接口時(shí)序及接口狀態(tài)機(jī)以簡(jiǎn)單讀寫

2019-06-11 05:00:07

速度和精度。

系統(tǒng)總體設(shè)計(jì)方案

本文提出了一種基于LABVIEW的USB接口高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì),充分利用DSP豐富的片上外設(shè)以及高性能的數(shù)字信號(hào)處理能力,將采集的數(shù)據(jù)經(jīng)DSP處理后通過高速USB

2018-12-26 07:00:05

分布式工業(yè)系統(tǒng),一方面需要更多的數(shù)字信號(hào)處理能力來更精確地控制馬達(dá),另一方面也需要更多和更高級(jí)的網(wǎng)絡(luò)接口(CAN,Ethernet 或者 Wireless 等)來實(shí)現(xiàn)實(shí)時(shí)的分布式監(jiān)控或控制功能。再比如

2019-07-04 07:49:02

如何讓CAN通訊完勝我們的傳統(tǒng)通信呢?讓小編來給你答案。

2021-05-18 06:08:19

對(duì)多點(diǎn)開關(guān)量采集。該系統(tǒng)通過RS232串口進(jìn)行通信,一臺(tái)采集系統(tǒng)就有四路開關(guān)量輸入,可實(shí)時(shí)采集四路開關(guān)量信號(hào)。系統(tǒng)內(nèi)置GPRS通訊模塊,可通過GPRS網(wǎng)絡(luò)發(fā)送信號(hào)到上位機(jī),傳輸距離無(wú)限遠(yuǎn),信號(hào)傳輸不受遮擋

2014-03-28 12:31:45

本文介紹了IP核的概念及其在SoC設(shè)計(jì)中的應(yīng)用,討論了為提高IP核的復(fù)用能力而采用的IP核與系統(tǒng)的接口技術(shù)。引言隨著半導(dǎo)體技術(shù)的發(fā)展,深亞微米工藝加工技術(shù)允許開發(fā)上百萬(wàn)門級(jí)的單芯片,已能夠?qū)?b class="flag-6" style="color: red">系統(tǒng)級(jí)

2018-12-11 11:07:21

本文介紹了使用ARM和DSP雙CPU構(gòu)成的雙核嵌入式系統(tǒng)的硬件平臺(tái),以及源代碼開放的Linux作為嵌入式系統(tǒng)中操作系統(tǒng)的方法,給出了系統(tǒng)設(shè)計(jì)的總體框圖,詳細(xì)介紹了ARM和DSP通信接口的設(shè)計(jì)。

2021-05-26 06:21:39

本文設(shè)計(jì)了一套基于DSP的陣列聲波信號(hào)采集與處理系統(tǒng),此系統(tǒng)將作為正在研制的陣列聲波測(cè)井儀中的一部分,應(yīng)用于油田勘探中。

2021-05-31 06:26:35

和Zynq-7045/7100兩款不同架構(gòu)的處理器。那么這款DSP + ZYNQ核心板,是如何實(shí)現(xiàn)核間通訊呢??核心板簡(jiǎn)介SOM-TL6678ZH是一款基于TIKeyStone架構(gòu)C6000系列TMS320C6678八

2021-03-16 17:53:53

怎樣去設(shè)計(jì)核信息遠(yuǎn)程采集系統(tǒng)的硬件部分?怎樣去設(shè)計(jì)核信息遠(yuǎn)程采集系統(tǒng)的軟件部分?

2021-05-27 07:09:01

)RESET模塊 該模塊生成全局復(fù)位信號(hào)。是所有模塊中優(yōu)先級(jí)最高的。系統(tǒng)上電后,該模塊將復(fù)位信號(hào)拉低并持續(xù) 1秒而后拉高,對(duì) DSP和 FPGA內(nèi)部其他模塊進(jìn)行復(fù)位。(2)DS18B20接口模塊 該模塊

2020-08-19 09:29:48

介紹一種基于DSP 的黑白電視信號(hào)采集電路。電路由通用視頻A/D 轉(zhuǎn)換器構(gòu)成, DSP 啟動(dòng)A/D 轉(zhuǎn)換并讀取A/D 轉(zhuǎn)換結(jié)果。電路結(jié)構(gòu)簡(jiǎn)潔、成本低、容易實(shí)現(xiàn),能滿足黑白電視信號(hào)采集的需

2009-04-16 14:25:36 23

23 介紹一種基于DSP 的黑白電視信號(hào)采集電路。電路由通用視頻A/D 轉(zhuǎn)換器構(gòu)成, DSP 啟動(dòng)A/D 轉(zhuǎn)換并讀取A/D 轉(zhuǎn)換結(jié)果。電路結(jié)構(gòu)簡(jiǎn)潔、成本低、容易實(shí)現(xiàn),能滿足黑白電視信號(hào)采集的需

2009-05-14 14:22:41 18

18 介紹一個(gè)基于USB2.0 接口和DSP的高速數(shù)據(jù)采集處理系統(tǒng)的工作原理、設(shè)計(jì)及實(shí)現(xiàn)。該高速數(shù)據(jù)采集處理系統(tǒng)采用TI 公司的TMS320C6000 數(shù)字信號(hào)處理器和Cypress 公司的USB2.0 接口芯片,可以

2009-05-16 14:48:53 21

21 提出了一種基于DSP 的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方案,對(duì)其中高速A/D、高速緩存。DSP 控制以及數(shù)據(jù)通訊接口等內(nèi)容進(jìn)行了討論,提出了更為有效的同步控制方式。該設(shè)計(jì)方案電路

2009-06-12 16:37:58 17

17 針對(duì)工業(yè)控制系統(tǒng)實(shí)際問題,使用列表的方法總結(jié)了通訊協(xié)議所涉及的內(nèi)容,討論了由阻塞和干擾引起的異常情況以及處理辦法,給出了工業(yè)控制系統(tǒng)通訊協(xié)議的基本規(guī)范和縱向描

2009-06-25 14:20:35 25

25 為了更好地解決心電信號(hào)的采集和處理問題, 沒計(jì)了以高性能DSP芯片TMS320C32x為核心心電信號(hào)的采集記錄系統(tǒng),對(duì)心電信號(hào)的放大、濾波部分的硬件設(shè)計(jì)進(jìn)行_r重點(diǎn)研究并針對(duì)實(shí)際應(yīng)

2009-07-06 16:00:17 73

73 為滿足瞬態(tài)沖擊信號(hào)快速測(cè)量,介紹了一種基于DSP的瞬態(tài)沖擊信號(hào)采集方法。采用器件內(nèi)的ADC和控制模塊,設(shè)計(jì)了包括衰減提升,LCD接口電路、存儲(chǔ)器接口電路等數(shù)字化信號(hào)采集

2009-07-07 17:19:52 14

14 介紹以TMS320C542 為核心處理器的數(shù)據(jù)采集系統(tǒng)實(shí)現(xiàn)微弱信號(hào)檢測(cè)。該系統(tǒng)優(yōu)化硬件調(diào)理電路設(shè)計(jì),保證采集數(shù)據(jù)的精度要求。利用DSP 實(shí)現(xiàn)時(shí)域信號(hào)的取樣積累平均算法,改善信噪

2009-08-07 09:27:11 20

20 為了解決基于DSP 視頻監(jiān)控系統(tǒng)的數(shù)據(jù)采集問題,本系統(tǒng)采用了視頻專用解碼A/D 芯片和復(fù)雜可編程邏輯器件CPLD進(jìn)行控制和接口設(shè)計(jì),有效地實(shí)現(xiàn)視頻信號(hào)的采集與讀取的高速并行性

2009-08-13 10:47:55 21

21 目前環(huán)境監(jiān)測(cè)儀器迫切需求高速,準(zhǔn)確,實(shí)時(shí),連續(xù)采集分析性,網(wǎng)絡(luò)化遠(yuǎn)程控制系統(tǒng)。本文介紹一種通過單片機(jī)與數(shù)字信號(hào)處理器(DSP)的同步串行通訊實(shí)現(xiàn)單片機(jī)控制DSP完成

2009-12-19 16:24:03 15

15 本文基于DSP5402芯片HPI接口技術(shù)的研究實(shí)例,重點(diǎn)介紹了在腦電數(shù)據(jù)采集系統(tǒng)中通過CCS5000集成開發(fā)環(huán)境實(shí)現(xiàn)DSP芯片HPI自舉加載并與主機(jī)通信的調(diào)試;并論述了系統(tǒng)的硬件設(shè)計(jì)和各

2010-01-07 13:16:04 12

12 基于DSP和DSP/BIOS的實(shí)時(shí)雷達(dá)信號(hào)采集與處理系統(tǒng):介紹了一種在實(shí)時(shí)操作系統(tǒng)DSP和DSP/BIOS 平臺(tái)下的雷達(dá)信號(hào)實(shí)時(shí)采集" 處理與傳輸系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn)! 利用Tms320c6416DSP強(qiáng)大的數(shù)據(jù)處理

2010-01-16 16:59:46 25

25 介紹了DSP聲音采集系統(tǒng)的硬件設(shè)計(jì)思想,以及硬件接口電路,包括電平轉(zhuǎn)換電路、AD轉(zhuǎn)換電路、存儲(chǔ)器、JTAG電路和USB接口電路等的設(shè)計(jì)方法,可以實(shí)現(xiàn)將模擬信號(hào)轉(zhuǎn)化為數(shù)字信號(hào)進(jìn)行

2010-02-24 13:53:04 106

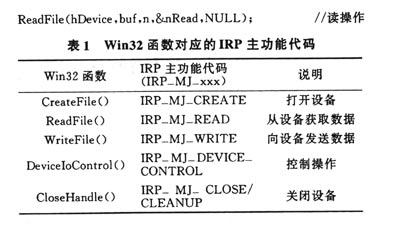

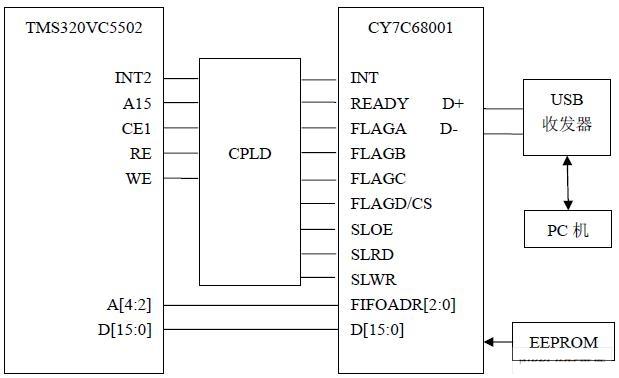

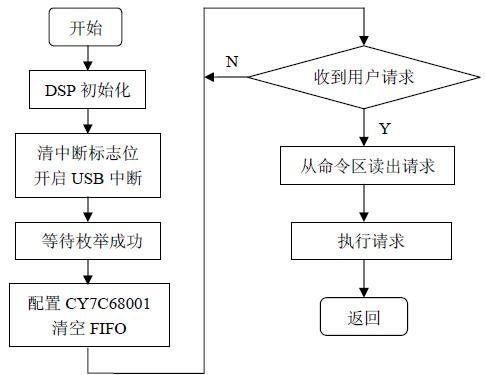

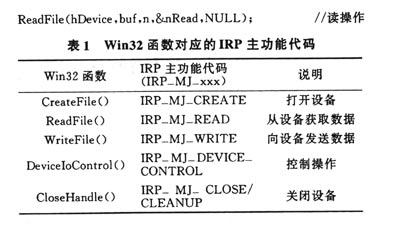

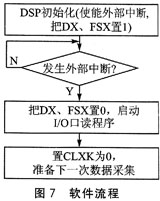

106 論述了基于USB的DSP核信號(hào)數(shù)據(jù)采集系統(tǒng)通訊接口的設(shè)計(jì)方法,其中數(shù)據(jù)采集系統(tǒng)中的USB通訊芯片采用CY7C68001,上位機(jī)通訊界面采用Microsoft Visual C++編寫,同時(shí)采用CPLD很好地解決了各芯片

2010-02-24 14:14:49 9

9 摘要:智能電池系統(tǒng)通常都需要一個(gè)靈活、高效地監(jiān)測(cè)和管理系統(tǒng),以在系統(tǒng)內(nèi)各種設(shè)備之間建立一種可靠、靈活的通訊接口機(jī)制。文中介紹了智能電池與PC機(jī)的通訊接口,提出了基

2010-07-12 11:57:34 18

18 論述了基于USB的DSP核信號(hào)數(shù)據(jù)采集系統(tǒng)通訊接口的設(shè)計(jì)方法,其中數(shù)據(jù)采集系統(tǒng)中的USB通訊芯片采用CY7C68001,上位機(jī)通訊界面采用Microsoft Visual C++編寫,同時(shí)采用CPLD很好地解決了各芯片

2010-07-17 17:26:41 17

17 目前環(huán)境監(jiān)測(cè)儀器迫切需求高速,準(zhǔn)確,實(shí)時(shí),連續(xù)采集分析性,網(wǎng)絡(luò)化遠(yuǎn)程控制系統(tǒng)。本文介紹一種通過單片機(jī)與數(shù)字信號(hào)處理器(DSP)的同步串行通訊實(shí)現(xiàn)單片機(jī)控制DSP完成信號(hào)的采集

2010-07-17 17:42:05 21

21 CCD信號(hào)采集系統(tǒng)的USB接口設(shè)計(jì)

CCD(ChargeCoupledDevices)電荷耦合器件是20世紀(jì)70年代初發(fā)展起來的新型半導(dǎo)體集成光電器件。由于CCD器件具有諸多優(yōu)點(diǎn):靈

2009-09-26 18:04:53 2249

2249

基于A/D和DSP的高速數(shù)據(jù)采集技術(shù)

中頻信號(hào)分為和差兩路,高速A/D與DSP組成的數(shù)據(jù)采集系統(tǒng)要分別對(duì)這兩路信號(hào)進(jìn)行采集。對(duì)于兩路數(shù)據(jù)采集電路,A/

2009-10-17 10:17:41 1201

1201

摘要:為了實(shí)現(xiàn)高速HDLC通訊協(xié)議,設(shè)計(jì)了DSP+FPGA結(jié)構(gòu)的485通訊接口,接口包括DSP、FPGA、485轉(zhuǎn)換等硬件電路,以及DSP與FPGA之間的數(shù)據(jù)交換程序和FPGA內(nèi)部狀態(tài)機(jī);其中DSP用于實(shí)現(xiàn)數(shù)據(jù)控制,F(xiàn)PGA用于實(shí)現(xiàn)HDLC通訊協(xié)議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 摘要:論述了基于DSP和USB2.0接口的高速便攜式數(shù)據(jù)采集處理系統(tǒng)的設(shè)計(jì),詳細(xì)地闡述了虛擬儀器系統(tǒng)的實(shí)現(xiàn)原理和方法。利用ADS8364模數(shù)轉(zhuǎn)換芯片可實(shí)現(xiàn)對(duì)6通道信號(hào)的同步采樣,分辨率達(dá)16位。利用EZUSBFX2作為USB2.0接口芯片,實(shí)現(xiàn)了主機(jī)和該系統(tǒng)的高速數(shù)據(jù)通訊

2011-03-01 01:13:49 132

132 摘要:研究了一種基于PCI總線的高速數(shù)據(jù)采集處理系統(tǒng),采用PCI9054作為PCI總線接口芯片和DSP芯片ADSP2188N作為系統(tǒng)通用硬件平臺(tái),詳細(xì)介紹了該系統(tǒng)的工作原理及軟硬件設(shè)計(jì)方案。該系統(tǒng)能滿足靈活加載程序、對(duì)采集的大容量數(shù)據(jù)進(jìn)行實(shí)時(shí)處理等要求,同時(shí)具有一

2011-03-01 23:52:26 43

43 針對(duì)傳統(tǒng)的IMU信號(hào)采集系統(tǒng)尺寸大、成本高和集成度低等不足,介紹了以DSP為核心的集成式IMU信號(hào)采集系統(tǒng)的解決方案,詳細(xì)闡述了系統(tǒng)硬件實(shí)現(xiàn)方案和軟件實(shí)時(shí)誤差校正算法。該系統(tǒng)具

2011-05-18 16:55:42 36

36 聲雷達(dá)信號(hào)采集系統(tǒng)主要由信號(hào)采集、信號(hào)處理、電源和時(shí)鐘四部分組成,本文介紹的基于美國(guó)模擬器件公司的DSP ADSP-TS201S和ADC AD7864的信號(hào)采集系統(tǒng)。

2011-08-17 11:17:52 1326

1326

中頻信號(hào)分為和差兩路,高速A/D與 DSP 組成的數(shù)據(jù)采集系統(tǒng)要分別對(duì)這兩路信號(hào)進(jìn)行采集。對(duì)于兩路數(shù)據(jù)采集電路,A/D與DSP的接口連接是一樣的。

2011-09-08 17:48:04 42

42 本文研究一種微控制器為基礎(chǔ)的信號(hào)采集系統(tǒng),以滿足信號(hào)采集的低成本和靈活模式。開發(fā)系統(tǒng)的主要硬件包括一臺(tái)微型計(jì)算機(jī)、一個(gè)以PIC18F1320為基礎(chǔ)的微控制器電路板以及串行通訊鏈

2011-09-14 12:02:49 5920

5920

在以DSP為核心的視頻處理系統(tǒng)中,視頻采集的方法通常可以分為兩大類:自動(dòng)的視頻采集和基于DSP的視頻采集。前者通常采用CPLD/FPGA控制視頻解碼芯片,通過FIFO或者雙口RAM向DSP傳送數(shù)據(jù)

2011-09-14 17:05:31 2302

2302

本文介紹了基于DSP的盤流伺服系統(tǒng)與上位機(jī)的通訊.詳細(xì)升紹了DsP串行通訊的硬件接口電路.寄存器漫置,軟件編程,通訊枷議。文中采用c語(yǔ)占編制了上位機(jī)通訊程序,實(shí)現(xiàn)丁上位機(jī)對(duì)

2011-10-12 15:40:03 73

73 中頻信號(hào)分為和差兩路,高速A/D與DSP組成的數(shù)據(jù)采集系統(tǒng)要分別對(duì)這兩路信號(hào)進(jìn)行采集。對(duì)于兩路數(shù)據(jù)采集電路,A/D與DSP的接口連接是一樣的。兩個(gè)A/D同時(shí)將和路與差路信號(hào)采

2012-03-28 10:41:38 4990

4990

在研究基于DSP的視頻監(jiān)控系統(tǒng)時(shí),考慮到高速實(shí)時(shí)處理及實(shí)用化兩方面的具體要求,需要開發(fā)一種具有高速、高集成度等特點(diǎn)的視頻圖象信號(hào)采集系統(tǒng),為此系統(tǒng)采用專用視頻解碼芯片

2012-05-25 09:44:08 2001

2001

通過測(cè)溫電路采集溫度數(shù)據(jù)經(jīng)AD轉(zhuǎn)換后給DSP控制器。重點(diǎn)給出疊代法計(jì)算方法DSP與AD轉(zhuǎn)換接口電路以及系統(tǒng)控制軟件的設(shè)計(jì)。

2015-10-30 10:03:35 4

4 為記錄多路振動(dòng)信號(hào)設(shè)計(jì)了一款基于USB接口的數(shù)據(jù)采集系統(tǒng)。該系統(tǒng)包含四路信號(hào)調(diào)理單元、模數(shù)轉(zhuǎn)換單元、以DSP器件為核心的控制單元和采用USB接口的與上位機(jī)通信單元。在采集頻率不高于300kHz

2015-12-28 09:57:29 17

17 基于LABVIEW與DSP串口的數(shù)據(jù)采集系統(tǒng)。

2016-01-20 16:26:53 41

41 《電網(wǎng)數(shù)據(jù)采集與監(jiān)控系統(tǒng)通用技術(shù)條件》,智能電網(wǎng)設(shè)備的通用標(biāo)準(zhǔn)。

2016-02-24 10:47:17 18

18 ARM與DSP雙核系統(tǒng)中的通信接口設(shè)計(jì)_趙學(xué)亮

2016-07-01 17:35:38 7

7 介紹了以DSP為核心的集成式IMU信號(hào)采集系統(tǒng)的解決方案,詳細(xì)闡述了系統(tǒng)硬件實(shí)現(xiàn)方案和軟件實(shí)時(shí)誤差校正算法。該系統(tǒng)具有速度快、體積小、功耗低等特點(diǎn)。

2017-09-08 16:39:17 7

7 非實(shí)時(shí)考勤系統(tǒng)的通訊接口設(shè)計(jì)

2017-10-17 10:47:40 0

0 基于DSP的數(shù)字信號(hào)采集處理系統(tǒng)設(shè)計(jì)

2017-10-19 15:10:22 25

25 基于DSP技術(shù)的圖像采集系統(tǒng)研究設(shè)計(jì)

2017-10-23 14:11:53 13

13 的系統(tǒng)中。核信號(hào)數(shù)據(jù)采集系統(tǒng)也不例外,利用 DSP 可以實(shí)時(shí)有效地處理采集的信號(hào),并將處理數(shù)據(jù)發(fā)送至上位機(jī)進(jìn)行進(jìn)一步處理。通常 數(shù)據(jù)采集系統(tǒng)下位機(jī)與上位機(jī)的通訊采用串口方式,這種方式不僅協(xié)議簡(jiǎn)單,而且連接方便。 但是這種

2017-10-25 11:23:47 0

0 需實(shí)時(shí)傳送數(shù)據(jù)的系統(tǒng)中。核信號(hào)數(shù)據(jù)采集系統(tǒng)也不例外,利用 DSP 可以實(shí)時(shí)有效地處理采集的信號(hào),并將處理數(shù)據(jù)發(fā)送至上位機(jī)進(jìn)行進(jìn)一步處理。通常 數(shù)據(jù)采集系統(tǒng)下位機(jī)與上位機(jī)的通訊采用串口方式,這種方式不僅協(xié)議簡(jiǎn)單,而且連接方便。

2017-10-26 15:00:11 2

2 的系統(tǒng)中。核信號(hào)數(shù)據(jù)采集系統(tǒng)也不例外,利用 DSP 可以實(shí)時(shí)有效地處理采集的信號(hào),并將處理數(shù)據(jù)發(fā)送至上位機(jī)進(jìn)行進(jìn)一步處理。通常 數(shù)據(jù)采集系統(tǒng)下位機(jī)與上位機(jī)的通訊采用串口方式,這種方式不僅協(xié)議簡(jiǎn)單,而且連接方便。 但是這種

2017-10-26 16:33:06 0

0 PCIE總線的多DSP系統(tǒng)接口設(shè)計(jì)

2017-10-31 10:42:03 23

23 在多CPU的分布式信號(hào)處理系統(tǒng)中,往往涉及CPU間的通訊與數(shù)據(jù)交換,大數(shù)據(jù)量的數(shù)據(jù)傳輸一般采用DMA方式,而小數(shù)據(jù)量的數(shù)據(jù)交換采用并行接口則比較快速靈活。因此,對(duì)于傳輸速度要求較高的DSP間的小數(shù)

2017-11-01 11:34:19 5

5 需實(shí)時(shí)傳送數(shù)據(jù)的系統(tǒng)中。核信號(hào)數(shù)據(jù)采集系統(tǒng)也不例外,利用 DSP 可以實(shí)時(shí)有效地處理采集的信號(hào),并將處理數(shù)據(jù)發(fā)送至上位機(jī)進(jìn)行進(jìn)一步處理。通常 數(shù)據(jù)采集系統(tǒng)下位機(jī)與上位機(jī)的通訊采用串口方式,這種方式不僅協(xié)議簡(jiǎn)單,而且連接方便。

2017-11-01 15:54:33 0

0 典型的DSP(數(shù)字信號(hào)處理器)內(nèi)部采用改進(jìn)的哈佛結(jié)構(gòu)和流水線技術(shù),可以在單指令周期內(nèi)完成乘加運(yùn)算,具有較高的處理能力。一個(gè)典型的基于DSP的信號(hào)采集處理系統(tǒng),通常由DSP、A/D轉(zhuǎn)換器、存儲(chǔ)器和相應(yīng)

2017-11-03 15:37:23 1

1 基于DSP處理器TMS320F2812與SD卡的接口,設(shè)計(jì)了一種便攜式的生理信號(hào)數(shù)據(jù)采集系統(tǒng),用于大容量多參數(shù)人體生理參數(shù)的采集。采用TMS320F2812作為主控芯片,以SD卡作為主要存儲(chǔ)介質(zhì)實(shí)現(xiàn)

2018-01-18 09:31:01 3395

3395

整個(gè)系統(tǒng)的組成如圖1所示。當(dāng)啟爆電路在DSP和FPGA的控制下啟爆時(shí),感應(yīng)線圈取出啟爆電流,首先是高速數(shù)據(jù)采集與存儲(chǔ)電路,以FPGA為核心,對(duì)數(shù)據(jù)進(jìn)行高速采集與存儲(chǔ)。數(shù)據(jù)存儲(chǔ)完畢,F(xiàn)PGA發(fā)信號(hào)告知DSP采集完畢,開始對(duì)采集的數(shù)據(jù)進(jìn)行相關(guān)的處理。

2018-10-07 12:03:03 2980

2980

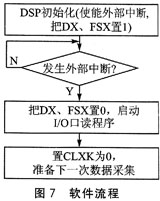

設(shè)計(jì)了一種基于16位定點(diǎn)DSP TMS320VC5410 的語(yǔ)音信號(hào)采集系統(tǒng), 該系統(tǒng)應(yīng)用了集ADC 和DAC 于一體的SIGMA-DELTA 型單片模擬接口芯片TLC320AD50C,采用FIFO

2019-01-24 15:06:10 3

3 設(shè)計(jì)了一種基于 TI DSP TMS320C6713B 和ALtera Cyclone 系列FPGA 的數(shù)據(jù)采集模塊,使用FPGA 做多路串行AD 器件的信號(hào)采集控制和數(shù)據(jù)緩沖,同時(shí)利用DSP

2019-03-05 16:30:29 16

16 設(shè)計(jì)了一套高速線陣CCD信號(hào)采集系統(tǒng),采用FPGA+DSP的數(shù)字處理方案,能滿足光信號(hào)的實(shí)時(shí)識(shí)別和處理,可用于研究靜態(tài)和動(dòng)態(tài)小粒子的光散射彩虹特性。

2019-11-21 17:32:39 24

24 石油測(cè)井中DSP采集系統(tǒng)詳解 DSP:數(shù)字信號(hào)處理器是一種智能微處理器能夠搞高效進(jìn)行各種數(shù)字信號(hào)處理。 在石油測(cè)井中DSP不是一般在常溫環(huán)境下的采集系統(tǒng),而是通過耐高溫厚膜技術(shù)封裝及優(yōu)化的一種可在

2020-03-07 14:29:10 880

880 。在眾多的DsP器件中,以n公司的DSP應(yīng)用最為廣泛,本文以TI DSP為例介紹系統(tǒng)接口電路的設(shè)計(jì)。一個(gè)完整地DSP控制系統(tǒng)的硬件接口電路一般包括電平變換電路.仿真器接口,JTAG電路.以及可擴(kuò)展的硬件接口

2020-11-04 18:50:45 15

15 用電信息采集系統(tǒng)通信協(xié)議第3部分

2021-08-27 09:32:57 3

3 用電信息采集系統(tǒng)通信協(xié)議第2部分

2021-08-27 09:22:12 3

3 用電信息采集系統(tǒng)通信協(xié)議之主站與采集終端

2021-08-27 09:21:11 3

3 CAN通訊設(shè)計(jì)DSP/MCU的CAN接口是指芯片外設(shè)中的CAN總線控制器,其輸出電平為TTL規(guī)格,如果直接將兩塊芯片的CANRX、CANTX引腳連接,無(wú)法實(shí)現(xiàn)CAN通訊。SAJ1000

2021-12-05 17:36:08 37

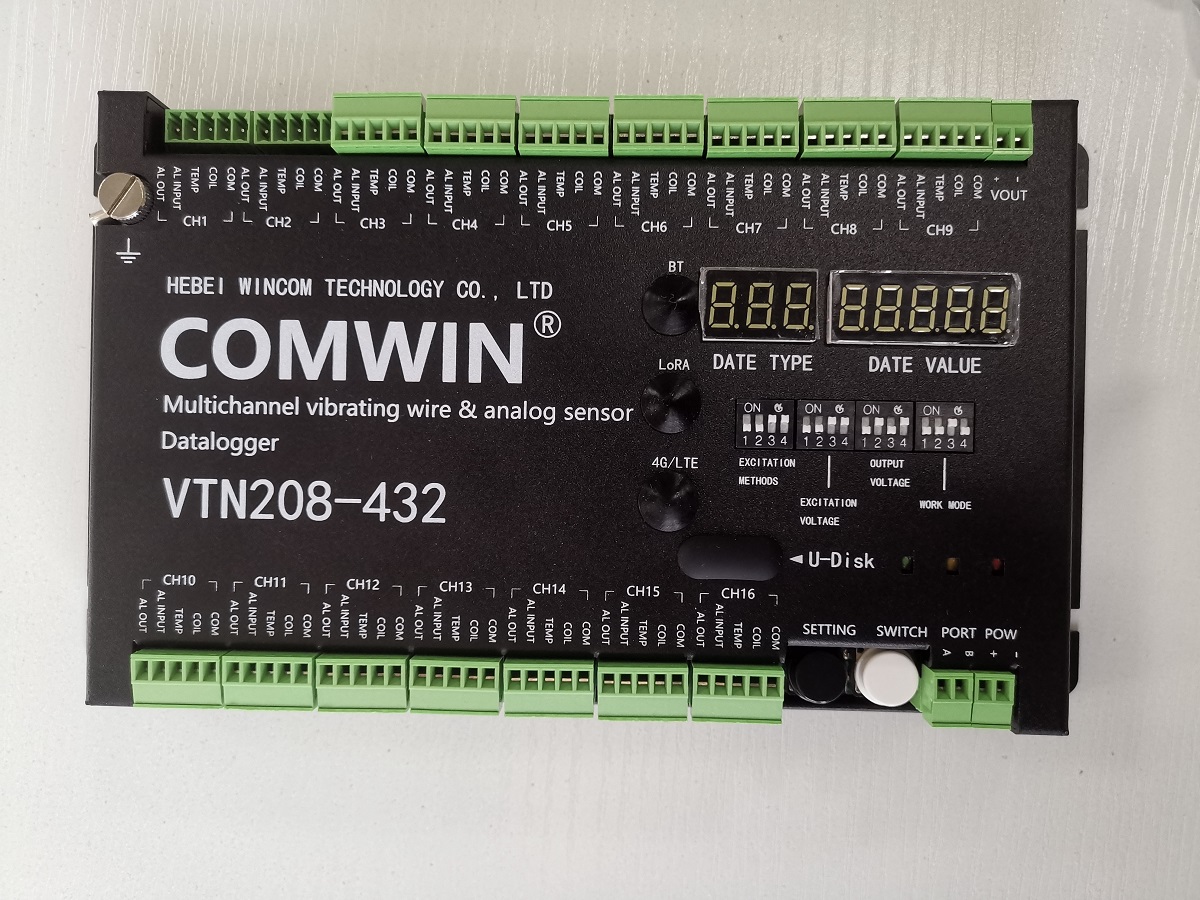

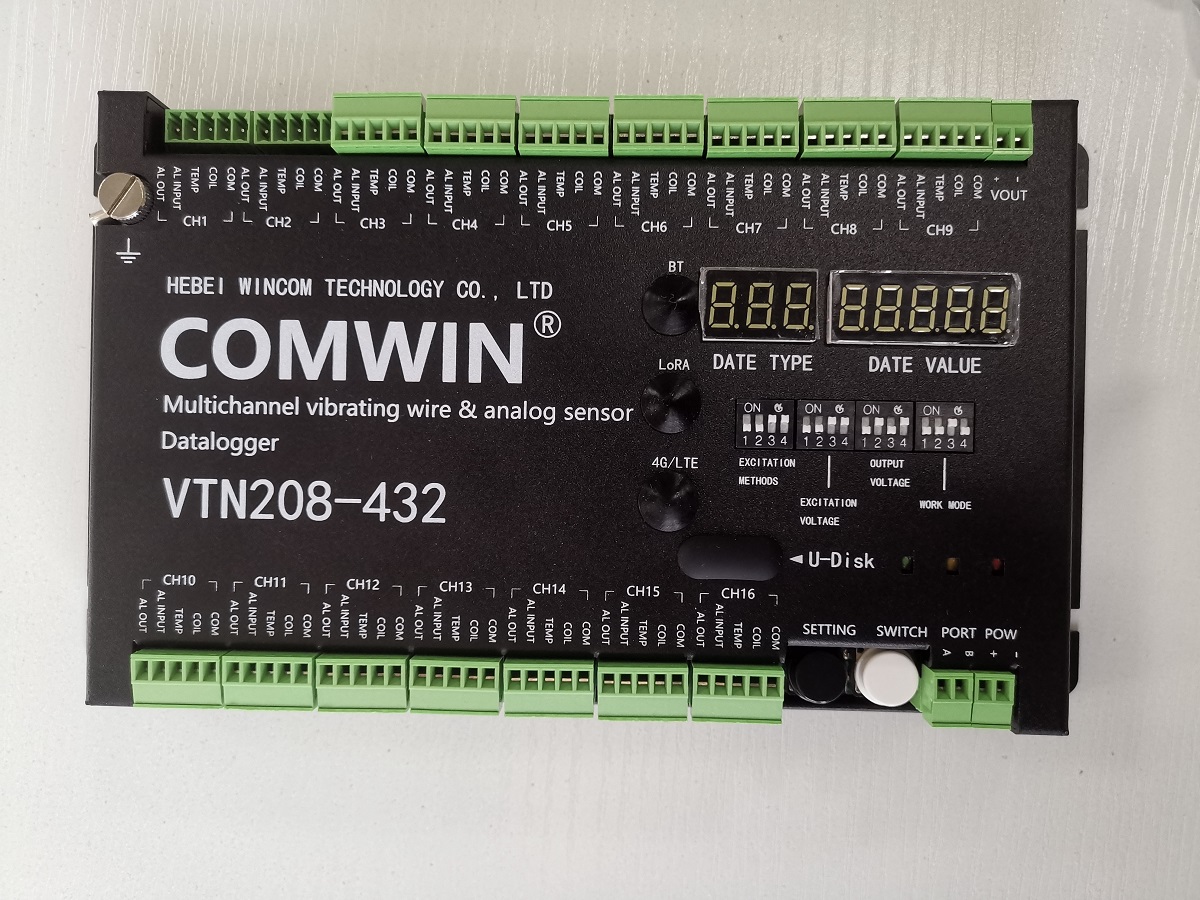

37 工程監(jiān)測(cè)多通道振弦模擬信號(hào)采集儀VTN通訊接口物理層參數(shù)配置 VTN208-432 是多通道振弦、溫度、模擬傳感信號(hào)采集儀,可對(duì)最多32通道振弦頻率、32通道溫度傳感器(熱敏電阻或 DS18B20

2023-03-15 10:21:16 381

381

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論