引言

世界正處于高科技下一波快速增長的開端, DSP已經成為業界公認的、將按指數增長的技術焦點。目前,大多數DSP設計已經能在半導體生產商(如T1、ADI、Freescale等)提供的通用DSP芯片上實現。通用處理器的價格相對比較便宜,并且有高質量和廉價的編程工具、方便快速實現DSP算法的支持,但開發人員更希望在原型創建和調試過程中能進行重新編程。

圖1 通用DSP處理器的性能與通信領域需要的DSP處理性能的比較

速度的需要

現在,對電子系統的性能要求已經超過了通用DSP處理器的能力。圖1顯示了由寬帶網絡市場驅動的對DSP算法的性能需求與通用DSP處理器性能的差異。可以看出通用DSP的性能容量與新的寬帶通信技術的需求之間的差距正以指數速率擴大。

傳統上DSP開發者可以獲得的改變通用DSP處理器性能的唯一方法就是將DSP算法注入到ASIC中,以達到加速硬件的目的。然而這種ASIC的解決方法實現起來非常困難,而且在ASIC上實現DSP算法是以犧牲可重編程的靈活性為代價的,同時還需要大量的非重復設計費用、漫長的原型初始化,以及購買大量昂貴的集成電路設計工具等。

隨著先進的FPGA架構如Xilinx Virtex-II和Altera Stratix-II的引入,DSP設計者可以獲得一種把通用DSP處理器的所有優點與ASIC的先進性能綜合在一起的新型硬件。這些新型的FPGA架構可以優化DSP的實現,并能提供滿足現今電子系統所必需的處理能力。

FPGA的優越性表現在它能允許DSP設計者做到“使結構適應算法”,設計者能夠根據實現系統性能的需要最大限度地使用FPGA內部的并行資源。而在通用DSP處理器中資源是固定的,因為每個處理器只包含一些數量有限的類似乘法器一樣的基本運算功能,設計者必須做到“使算法適應結構”,因而無法達到在FPGA中能夠獲得的性能。

圖2 全球DSP收入預測

半導體工業的亮點

圖2顯示了整個DSP市場和片內算法市場(由FPGA、結構化ASIC和ASIC幾部分組成)的年收入預測。其中,DSP片內算法市場今后三年內將以高于42%的年增長率增長,是整個半導體領域增長最快的部分。

現在DSP的設計團隊所面臨的挑戰和二十世紀九十年代ASIC的設計者所面臨的類似—DSP開發組如何用目標FPGA的設計方法代替通用DSP;如何去開發所需要的新的設計技巧;如何完善公司的設計流程;怎樣才能提出新的DSP算法的實現方法,同時又不危及當前產品的開發計劃。或許更重要的是,管理者怎樣才能夠使災難性結果發生的可能性降低到最小。

AccelChip公司認為DSP的未來取決于新型設計方法的采用,而這種方法必須能使公司滿足DSP市場對上市時間、成本的苛刻要求。和ASIC、FPGA的產生一樣,對DSP變革的方式就是采用真正的、自上而下的設計流程。

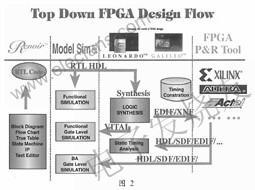

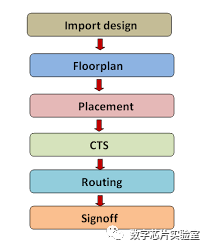

圖3 傳統的DSP設計流程

傳統自上而下的設計流程

傳統上,DSP設計被分為兩種類型的工作:系統/算法的開發和軟/硬件的實現。這兩類工作是由完全不同的兩組工程師完成,通常這兩個組在各自的接口之間被相對分開。算法開發者在不考慮系統的結構或軟/硬件實現細節的情況下使用數學分析工具來創建、分析和提煉所需要的DSP算法;系統設計者則主要考慮功能的定義和結構的設計,并保持與產品說明及接口標準相一致。軟/硬件設計組采用系統工程師和算法開發人員所建立的規范進而完成DSP設計的物理實現。

一般來講,細則規范可劃分成很多小的模塊,每個小模塊分配給各個成員,他們必須首先理解屬于自己的模塊的功能。

如果DSP算法的目標是FPGA、結構化ASIC或SoC,那么首要任務就是用Verilog或VHDL等硬件描述語言來建立一個RTL模型。這就需要實現工程師了解通信理論和信號處理以便明白系統工程師提出的細則規范。建立一個RTL模型和仿真測試平臺常常需要花費一至兩個月的時間,這主要是因為需要人工驗證RTL文件和MATLAB模型的準確匹配。RTL模型仿真環境一經建立,實現工程師就要同系統工程師和算法開發人員進行交流,共同分析DSP系統硬件實現的性能、范圍和功能。

由于系統工程師在算法開發階段無法看到物理層設計,因此通常會需要修改原來的算法和系統結構、更新文字性規范、修改RTL模型和測試平臺以及重新仿真,這些過程往往需要連續進行多次,直到DSP系統的性能要求能夠由硬件實現為止。接著,實現工程師使用邏輯綜合執行一種標準的FPGA/ASIC自上而下的設計流程,從而將RTL模型映射到門級網表,并且使用物理設計工具在給定的FPGA/ASIC器件中設置布局網表。圖3給出了基本的片內DSP算法的設計流程,主要由算法開發和硬件實現兩個相對分開的部分組成。

如上所述,只有花費很長的時間人工建立基于文字規范的RTL模型,才能避免因兩個設計域(design domains)之間缺乏聯系而造成設計開發進程的延遲,然而對這一設計工程更大的擔心是DSP算法的物理設計是基于硬件工程師對文字規范主觀的理解。

硬件工程師中缺乏DSP專家,因此常常會因為對要求功能的曲解而造成災難性的后果。隨著DSP復雜度的增加,在人工建立RTL模型的過程中,產生錯誤已司空見慣。由于相同的錯誤被寫入仿真測試平臺中,因此仿真中即便出現多次錯誤也無法被捕捉到,只有到了原型設計階段,硬件設計錯誤才會被發現。

改進方法

FPGA/ASIC設計人員采用真正意義上的自上而下的設計方法,最重要的好處之一就是設計數據管理的改善。但是當ASIC和FPGA采用和現有DSP設計相同的自下而上的設計方法時,由于缺乏單一且有效的設計數據源,將會引入許多錯誤。因此,在當今的DSP設計中,各個獨立的設計部門有義務使MATLAB模型和人工創建的RTL模型及測試平臺保持同步。可是如前所述,這兩個團隊很少交流,而且通常在地理位置上也相距很遠。所以管理這些數據變得非常困難。

CoWare在其SPW工具包里提供了一種模塊同步問題的解決方案:將輔助模擬設計方法的概念引入硬件設計系統中,從而達到從細則規范到實現的轉變。在這種方法中,CoWare 建議DSP設計組使用他們具有DSP硬件模型庫的硬件設計系統創建一個可以執行的規范,從而取代對DSP規范和算法進行詮釋的編程語言。

這種方法在消除硬件工程師開發RTL模型時造成的曲解方面很有優勢,但是,它對確保設計數據同步方面還存在不足。由于每次修正模塊都需要人工修改可執行規范,特別在現今復雜度不斷增加和產品上市時間越來越短的雙重壓力下,發生錯誤的可能性將會大幅增加。

真正自上而下的

DSP設計方法

Accelchip公司的DSP合成工具使用VHDL或Verilog硬件描述語言能夠直接讀出MATLAB模型并自動輸出可以合成的RTL模型和仿真測試平臺。通過連接DSP的兩個設計域,給DSP設計小組在設計的人力和時間、曲解的消除、高成本的重復工作、硬件實現的自動驗證,以及系統設計人員和算法開發人員在開發的初期階段進行結構探索時所需要的能力等方面帶來了很大的簡化。

Accelchip使硬件設計人員不需要人工創建RTL模型和仿真測試平臺,從而縮短了開發周期,減少了硬件實現所需要設計人員的數量。而且自動建立的RTL模型是目標FPGA器件的“結構化意識”,而不是簡單的、繼承下來的RTL模型。建立RTL模型后,其高級綜合工具將創建一個邏輯綜合的最佳實現,以確保所產生的門級網表具有FPGA器件的優點。

例如,DSP算法在不同供應商提供的FPGA器件列中實現,其性能和范圍有很大的差異,這是因為對于不同設備來講,結構、邏輯資源、布局資源以及布局方法都是不同的。通過“結構化意識”,Accelchip為DSP設計小組的目標FPGA器件提供了很好的物理實現。同時通過提供容易使用的、自動的從MATLAB到硬件實現的直接路徑,使得DSP系統設計人員和算法開發人員能夠在設計開發初期定義他們的算法。進而算法開發人員能夠很快地將MATLAB設計轉換成綜合了性能、范圍、成本和功率優點的目標FPGA的門級網表。有了來自算法物理實現的初期或開發周期中的反饋,就意味著設計流程后期所做的重復更少,再一次節省了寶貴的時間和人力。

結語

DSP技術的重要性日益增加,對其算法的性能要求遠遠超過了通用性DSP處理器的能力,從而促使DSP實現小組去尋找硬件的解決方法。FPGA給DSP實現提供了理想的平臺,Accelchip提供的真正的自上而下的設計方案無縫地融入了DSP的設計環境,從而確保了在轉向真正的自上而下的DSP設計方法時管理風險的最小化。

- 設計流程(8006)

- 自上而下(5563)

相關推薦

DSP的實現方法

DSP設計流程是什么?

FPGA 教程|PDS 軟件使用流程

FPGA培訓—基于FPGA的DSP系統設計與實現

IC設計流程介紹

RT-Thread smart內存虛擬地址到物理地址的轉換是一個什么樣的流程

[討論]FPGA培訓—基于FPGA的DSP系統設計與實現

【社招】DSP軟件工程師(物理層算法實現方向)

什么是以太網物理層?Ethernet物理層有哪些功能?

仿照firefly的方式在device/rockchip/rk3399下直接添加新的Product/Device

在IC物理設計中應用層次化設計流程Hopper提高產能

基于LabVIEW開發環境實現DSP設計

如何使用DCNXT實現物理綜合?

怎么實現基于DSP和SOPC數字信號發生器的設計?

用 TCL 定制 Vivado 設計實現流程

請問一下高清電視音頻解碼的定點DSP怎么實現?

請問如何通過物理綜合與優化去提升設計性能?

通過FPGA實現溫控電路接口及其與DSP通信接口的設計

采用DSP實現網絡通信接口設計

采用DSP實現網絡通信接口設計

Agent Technologies實現應用流程再造

6

6基于DSP實現的無差拍控制逆變器

39

39基于SOPC的DSP系統的設計與實現

29

29基于DSP的寬頻逆變算法的研究與實現

16

16基于串口實現DSP程序的在線編程

24

24FPGA實現DSP應用

14

14DSP無線電調制器的設計與實現

16

16基于DSP 的視頻PCI 采集壓縮卡的實現

11

11基于RTW 的DSP 控制系統研究

37

37實現密鑰的物理安全

9

9Xilinx DSP Primer 中文教程

75

75DSP互連分析與FPGA實現

22

22快速小波變換的定點DSP實現

1298

1298

基于DSP實現可并機的逆變電源

1166

1166

一種采用FPGA/DSP的靈巧干擾平臺設計與實現

975

975

FPGA/EPLD的自上而下設計方法

3679

3679

基于DSP的TETRA話音編碼設計與實現

56

56融合DSP設計與FPGA硬件實現

224

224Altera演示業界首款FPGA的浮點DSP設計流程

613

613基于DSP的閉環SPWM的實現方法

69

69基于Arria V和Cyclone V精度可調DSP模塊的高性能DSP應用與實現

35

35Vivado設計之Tcl定制化的實現流程

3294

3294

FPGA的開發流程和物理含義和實現目標詳解

1273

1273

如何在Vivado中應用物理優化獲得更好的設計性能

3728

3728如何進行DSP的軟件編程及使用算法實現的學習教程說明

17

17用Tcl實現Vivado設計全流程

1865

1865交流采樣技術及其DSP設計實現

23

23ASIC物理設計流程概述

680

680

廣凌全流程采購管理系統:能實現全流程監管留痕嗎?

275

275

PCB行業應如何實現全流程追溯?

325

325

Innodb中的Btree實現(一)·引言&insert篇

201

201

電子發燒友App

電子發燒友App

評論