C ++ 引入了構(gòu)造器(constructor,也叫構(gòu)造函數(shù))的概念,它是在創(chuàng)建對象時被自動調(diào)用的特殊方法。 Java 也采用了構(gòu)造器,并且還提供了一個垃圾收集器(garbage collector),當不再使用內(nèi)存資源的時候,垃圾收集器會自動將其釋放。

2022-11-22 09:32:16 293

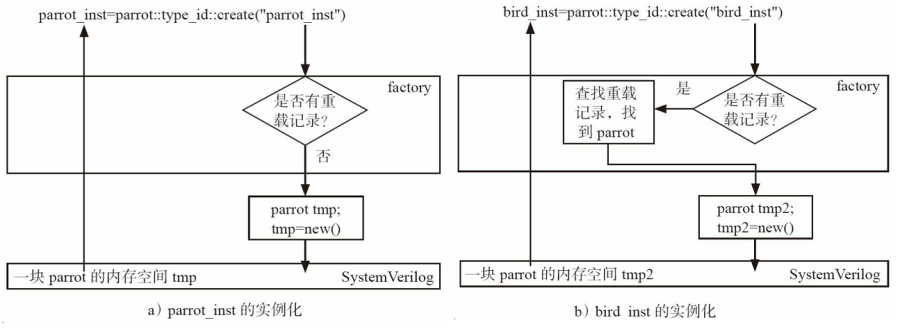

293 SystemVerilog中多態(tài)能夠工作的前提是父類中的方法被聲明為virtual的。

2022-11-28 11:12:42 466

466 SystemVerilog 的VMM 驗證方法學教程教材包含大量經(jīng)典的VMM源代碼,可以實際操作練習的例子,更是ic從業(yè)人員的絕佳學習資料。SystemVerilog 的VMM 驗證方法學教程教材[hide][/hide]

2012-01-11 11:21:38

shallow copy只能復制類中的對象句柄,如果我們還想為這個對象句柄實例化,并復制其中的內(nèi)容呢?那就是deep copy的概念了。deep copy是通過聲明自定義的copy函數(shù)來實現(xiàn)的,這個

2022-11-25 11:17:28

SystemVerilog有哪些標準?

2021-06-21 08:09:41

1、SystemVerilog編碼層面提速的若干策略介紹頻繁的函數(shù)/任務調(diào)用會增加開銷比如:用foreach遍歷方式計數(shù)(foreach有內(nèi)置函數(shù)),不如單獨的計數(shù)器!如下代碼:這樣寫比較慢:這樣寫

2022-08-01 15:13:13

官方的一個systemverilog詳解,很詳細。推薦給打算往IC方面發(fā)展的朋友。QQ群374590107歡迎有志于FPGA開發(fā),IC設(shè)計的朋友加入一起交流。一起為中國的IC加油!!!

2014-06-02 09:47:23

官方的一個systemverilog詳解,很詳細。推薦給打算往IC方面發(fā)展的朋友。

2014-06-02 09:30:16

systemverilog的一些基本語法以及和verilog語言之間的區(qū)別。

2015-04-01 14:24:14

類成員函數(shù)中const的使用,有什么注意事項?

2021-04-26 06:42:30

StreamWriter對象,.NET把這種編碼設(shè)置為默認的編碼方式。StreamWriter sw=new StreamWriter(@ “C:\test.txt”, true);在這個構(gòu)造函數(shù)中,第二個

2020-10-23 17:03:19

Handler 類來向主線程發(fā)送消息;主線程則可以通過 Handler 來處理消息,根據(jù)消息來對界面 UI 進行操作。Handler 的使用按照正常的方法,創(chuàng)建類只需要調(diào)用它的構(gòu)造函數(shù)即可,那么創(chuàng)建一個

2019-09-23 09:05:03

誰能指點一下,指針也是一個對象啊!為什么這個對象不會執(zhí)行構(gòu)造函數(shù)呢?

2020-03-23 04:37:25

為什么 TwoPhaseCons* obj = TwoPhaseCons::NewInstance();不會報錯??????????TwoPhaseCons* obj = TwoPhaseCons::NewInstance();這句話是繞開了構(gòu)造函數(shù)去執(zhí)行NewInstance();函數(shù)嗎?

2020-03-23 01:30:34

進行元素獲取,對于容器類而言,引擎會直接通過快速路徑訪問到元素存儲位置,返回該值。

圖2 容器類API的調(diào)用流程

(三)容器類對象模型

在方舟開發(fā)框架中,構(gòu)造容器類對象模型的流程如下圖所示,在運

2022-03-07 11:40:20

。2. 訪問?屬性包含四個特性,分別是:例:3. 創(chuàng)建對象的?法1. 最簡單粗暴:對象字?量2. ?廠模式3. 構(gòu)造函數(shù)模式● 創(chuàng)建 Person 實例,必須使? new 操作符,這種?式實際上經(jīng)歷了

2019-09-18 09:05:06

以上的JavaScript中已經(jīng)不再拋出該錯誤,但依然可以通過new關(guān)鍵字來自定義該類型的錯誤提示。以上的6種派生錯誤,連同原始的Error對象,都是構(gòu)造函數(shù)。開發(fā)者可以使用它們,認為生成錯誤對象的實例

2017-09-22 15:28:24

。當在程序框圖中放置了構(gòu)造函數(shù)節(jié)點后,可以單擊對話框中的Browse按鈕來瀏覽dll。

需要選中dll中想要操作的類和構(gòu)造函數(shù)。

注意:DLL中某個類可能有很多構(gòu)造函數(shù),需要查閱用戶手冊以確定

2023-11-09 19:08:37

的(C語言如何為實現(xiàn)面向?qū)ο缶幊蹋埿』锇閭冏孕芯W(wǎng)絡搜索和學習)。C面向?qū)ο缶幊?b class="flag-6" style="color: red">中,是通過構(gòu)造函數(shù)來對具體類的對象進行構(gòu)造和初始化的;C語言實現(xiàn)的驅(qū)動框架,在重要數(shù)據(jù)結(jié)構(gòu)(類)實例的構(gòu)造和初始化的時候

2022-05-12 17:00:38

. invoke copy constructor of T1}STL源碼剖析中的,這個new是什么用法?這個函數(shù)是用來干什么的

2011-03-21 10:47:45

學快速發(fā)展,這些趨勢你了解嗎?SystemVerilog + VM是目前的主流,在未來也將被大量采用,這些語言和方法學,你熟練掌握了嗎?對SoC芯片設(shè)計驗證感興趣的朋友,可以關(guān)注啟芯工作室推出的SoC芯片

2013-06-10 09:25:55

請問下各位大蝦,有使用過構(gòu)造器節(jié)點調(diào)用.NET做的dll文件嗎?為什么labview構(gòu)造器中嘗試程序集發(fā)生錯誤

2016-03-18 22:15:15

有沒有人用labview連接mongodb數(shù)據(jù)庫的?已下載mongodb的c#驅(qū)動,利用labview中的.net控件調(diào)用相關(guān)函數(shù),但是驅(qū)動中有部分函數(shù)在泛型類中, labview能調(diào)用c#中的泛型類嗎?labview 選擇.NET類找不到泛型類??

2021-04-08 13:38:02

大家好,我對一個 round robin 的 systemverilog 代碼有疑惑。https://www.edaplayground.com/x/2TzD代碼第49和54行是怎么解析呢 ?

2017-03-14 19:16:04

CRect:用來表示矩形的類,擁有四個成員變量:top left bottom right。分別表是左上角和右下角的坐標。可以通過以下的方法構(gòu)造:

2019-08-02 06:33:15

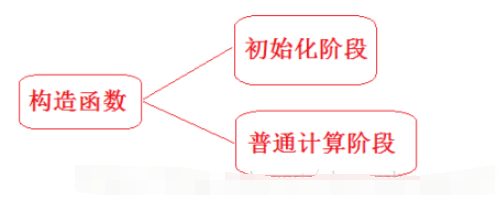

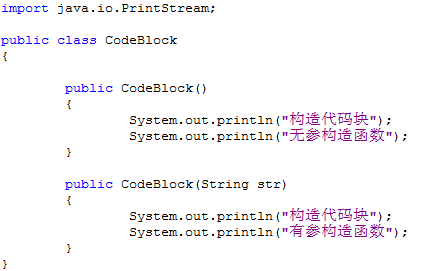

什么是構(gòu)造函數(shù)?怎樣去編寫構(gòu)造函數(shù)呢?

2022-02-22 08:31:27

FPGA中接口的連接方式。 ??也許很多FPGA工程師對SystemVerilog并不是很了解,因為以前的FPGA開發(fā)工具是不支持SystemVerilog的,導致大家都是用VHDL或者Verilog來

2021-01-08 17:23:22

在某大型科技公司的招聘網(wǎng)站上看到招聘邏輯硬件工程師需要掌握SystemVerilog語言,感覺SystemVerilog語言是用于ASIC驗證的,那么做FPGA工程師有沒有必要掌握SystemVerilog語言呢?

2017-08-02 20:30:21

::lcFun; ca.(*pFun)(2); } 在這里,指針的定義與使用都加上了“類限制”或“對象”,用來指明指針指向的函數(shù)是那個類的這里的類對象也可以是使用new得到的。比如: CA

2018-07-13 03:51:04

:1. 首先在基類中,采用使用copy_data函數(shù)的寫法class Transaction; rand bit[31:0] src, dst,data[8]; bit[31:0] crc

2016-04-07 14:28:11

函數(shù)體。當我合成c ++代碼時,這是我的警告。任何人都可以幫我解決它。我的代碼行是:Edge * edges = new Edge();它只是一個指向類等于Edges類構(gòu)造函數(shù)的類的指針。

2020-05-14 08:52:10

構(gòu)造函數(shù)和運算符的用途是什么

2020-11-05 07:02:49

我們將展示如何在SystemVerilog中為狀態(tài)機的命令序列的生成建模,并且我們將看到它是如何實現(xiàn)更高效的建模,以及實現(xiàn)更好的測試生成。?

2021-01-01 06:05:05

在參數(shù)列里也隱含有一個指向自身的this指針。3)對于靜態(tài)成員則要定義成全局變量或全局函數(shù),因為結(jié)構(gòu)體中不能有靜態(tài)成員。二.類的構(gòu)造函數(shù)類在實例化的時候會調(diào)用類的缺省構(gòu)造函數(shù),在struct里,要定義

2020-07-08 20:51:50

在參數(shù)列里也隱含有一個指向自身的this指針。3)對于靜態(tài)成員則要定義成全局變量或全局函數(shù),因為結(jié)構(gòu)體中不能有靜態(tài)成員。二.類的構(gòu)造函數(shù)類在實例化的時候會調(diào)用類的缺省構(gòu)造函數(shù),在struct里,要定義

2020-07-11 09:34:24

在參數(shù)列里也隱含有一個指向自身的this指針。3)對于靜態(tài)成員則要定義成全局變量或全局函數(shù),因為結(jié)構(gòu)體中不能有靜態(tài)成員。二.類的構(gòu)造函數(shù)類在實例化的時候會調(diào)用類的缺省構(gòu)造函數(shù),在struct里,要定義

2021-11-17 10:16:27

的this指針。3)對于靜態(tài)成員則要定義成全局變量或全局函數(shù),因為結(jié)構(gòu)體中不能有靜態(tài)成員。二.類的構(gòu)造函數(shù)類在實例化的時候會調(diào)用類的缺省構(gòu)造函數(shù),在struct里,要定義一個同名函數(shù)指針指向一個具有構(gòu)造函數(shù)

2021-07-05 14:59:39

的成員。在類的成員函數(shù)里,實際上在參數(shù)列里也隱含有一個指向自身的this指針。3)對于靜態(tài)成員則要定義成全局變量或全局函數(shù),因為結(jié)構(gòu)體中不能有靜態(tài)成員。二.類的構(gòu)造函數(shù)類在實例化的時候會調(diào)用類的缺省構(gòu)造

2021-06-30 10:54:41

,實際上在參數(shù)列里也隱含有一個指向自身的this指針。3)對于靜態(tài)成員則要定義成全局變量或全局函數(shù),因為結(jié)構(gòu)體中不能有靜態(tài)成員。二.類的構(gòu)造函數(shù)類在實例化的時候會調(diào)用類的缺省構(gòu)造函數(shù),在struct里,要

2021-07-07 09:31:16

剛接觸systemverilog,最近在采用questasim10.1版本進行仿真時,發(fā)現(xiàn)貌似questasim不支持擴展類的操作?代碼如下:`timescale 1ns/1nsmodule

2016-04-11 09:44:08

。static成員函數(shù)在不創(chuàng)建類對象的時候直接調(diào)用。很不幸的是MATLAB不支持static成員變量,只能定義static成員函數(shù),于是很多在C++中輕而易取實現(xiàn)的功能,在MATLAB中卻成了捉襟見肘

2012-03-07 10:42:47

()代碼可以自行添加到構(gòu)造函數(shù)的第一行(必須是第一行,否則報錯)2、如果父類沒有定義構(gòu)造函數(shù),系統(tǒng)會默認定義一個無參無返回值的構(gòu)造函數(shù),子類繼承時無需(無需的意思是:可以寫可以不寫)在子類構(gòu)造函數(shù)中顯式

2022-10-19 14:51:30

多態(tài)(Polymorphism) ,從字面意思上看指的是多種形式,在OOP(面向?qū)ο缶幊?中指的是同一個父類的函數(shù)可以體現(xiàn)為不同的行為。在SystemVerilog中,指的是我們可以使用父類句柄來

2022-12-05 17:34:00

;From B!");}}運行結(jié)果:From A!From B!在這個例子中,對象A的構(gòu)造函數(shù)中,用new B(this)把對象A自己作為參數(shù)傳遞給了對象B

2022-10-21 14:38:40

起初剛學C++時,很不習慣用new,后來看老外的程序,發(fā)現(xiàn)幾乎都是使用new,想一想?yún)^(qū)別也不是太大,但是在大一點的項目設(shè)計中,有時候不使用new的確會帶來很多問題。當然這都是跟new的用法有關(guān)

2020-11-05 07:27:40

在STM32F10X項目中使用了C++的特性,使用arm-none-eabi-g++編譯,程序可以正常運行。問題: C++定義的全局變量,其類的構(gòu)造函數(shù)不被執(zhí)行,在構(gòu)造函數(shù)中設(shè)置的變量值都無效(實際

2018-10-10 08:45:57

Systemverilog數(shù)據(jù)類型l 合并數(shù)組和非合并數(shù)組1)合并數(shù)組:存儲方式是連續(xù)的,中間沒有閑置空間。例如,32bit的寄存器,可以看成是4個8bit的數(shù)據(jù),或者也可以看成是1個32bit

2015-08-27 14:50:39

VIEW_MIN_INTERVAL10#define VIEW_MAX_INTERVAL30000[color=rgb(51, 102, 153) !important]復制代碼1.在CDocView構(gòu)造函數(shù)里添加初始話CDocView

2016-07-06 12:56:54

嵌入式LINUX驅(qū)動學習之15 i2c代碼舉例(三軸加速度傳感器MMA8653)方式二一、代碼舉例二、用戶空間程序(參考方式一)本實例是通過i2c_new_device函數(shù)添加I2C設(shè)備,相比于板級

2021-12-17 06:57:34

.......................................................................................................... 68第9 章 類的構(gòu)造函數(shù)、析構(gòu)函數(shù)與賦值函數(shù)

2008-06-27 10:22:25

給AVR 單片機構(gòu)造移位寄存器方式的輸出函數(shù)

2009-05-14 15:07:41 37

37 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 20

20 基于混沌理論和單向散列函數(shù)的性質(zhì),提出了用類Hènon 混沌映射構(gòu)造單向散列函數(shù)的算法,并討論了此算法的安全性。這種算法具有初值敏感性和不可逆性,且對任意長度的原始

2009-08-13 11:57:39 8

8 該文由傳統(tǒng)的格雷對構(gòu)造方法交織和級聯(lián)出發(fā),提出了一種新的稱之為生成函數(shù)的格雷對構(gòu)造方法,該方法適用于長度為2n 的格雷對。文中分析了格雷對生成函數(shù)和希爾維斯特Hadamard

2010-02-08 16:04:49 8

8 類式繼承:利用構(gòu)造函數(shù)(類)繼承的方式 類 : JS是沒有類的概念的 , 把JS中的構(gòu)造函數(shù)看做的類 舉例 function Aaa () { //父類 this .name = '小明

2017-11-24 15:26:02 526

526 的譜不相交plateaued函數(shù),一類特殊的布爾置換以及一個高非線性度平衡函數(shù),提出了一個構(gòu)造高非線性度平衡布爾函數(shù)的方法。通過分析可知,利用該方法可以構(gòu)造代數(shù)次數(shù)達到最優(yōu)、非線性度不小于的2k元平衡函數(shù)。

2017-12-17 09:43:32 0

0 本文檔的主要內(nèi)容詳細介紹的是如何深度解析C++拷貝構(gòu)造函數(shù)詳細資料說明。

2019-07-05 17:41:00 0

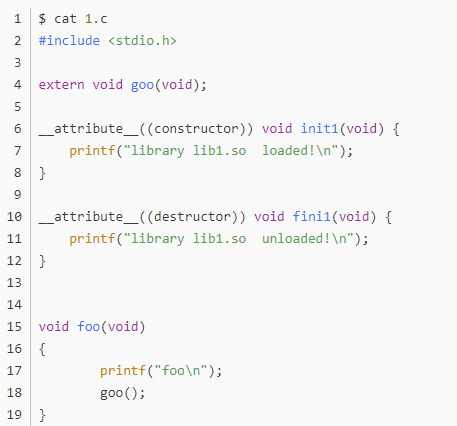

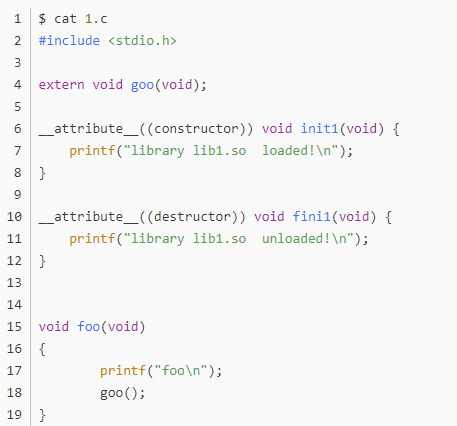

0 共享庫有類似C++類構(gòu)造和析構(gòu)函數(shù)的函數(shù),當動態(tài)庫加載和卸載的時候,函數(shù)會被分別執(zhí)行。一個函數(shù)加上 constructor的 attribute就成了構(gòu)造函數(shù);加上 destructor就成了析構(gòu)函數(shù)。

2020-06-22 09:18:48 2067

2067

類在實例化的時候會調(diào)用類的缺省構(gòu)造函數(shù),在struct里,要定義一個同名函數(shù)指針指向一個具有構(gòu)造函數(shù)功能的初始化函數(shù),與構(gòu)造函數(shù)不同的是,要在初始化函數(shù)里加入進行函數(shù)指針初始化的語句。使用的時候在創(chuàng)建結(jié)構(gòu)體變量的時候要用malloc而不是new,并且這個時候要手工調(diào)用初始化函數(shù)。

2020-06-24 14:28:21 4502

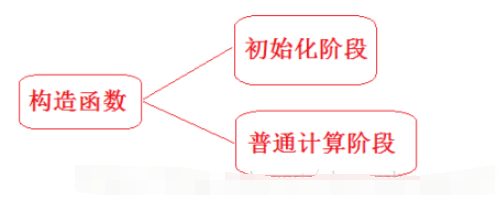

4502 構(gòu)造函數(shù)是一個特殊的成員函數(shù),名字與類名相同,創(chuàng)建類類型對象的時候,由編譯器自動調(diào)用,在對象的生命周期內(nèi)只且調(diào)用一次,以保證每個數(shù)據(jù)成員都有一個合適的初始值。

2020-06-29 11:44:15 1361

1361

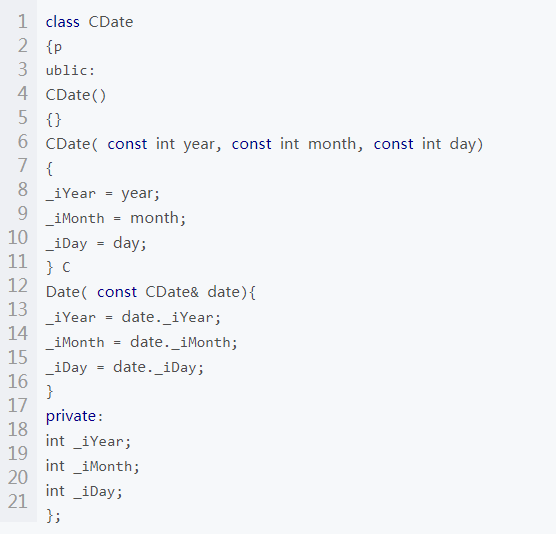

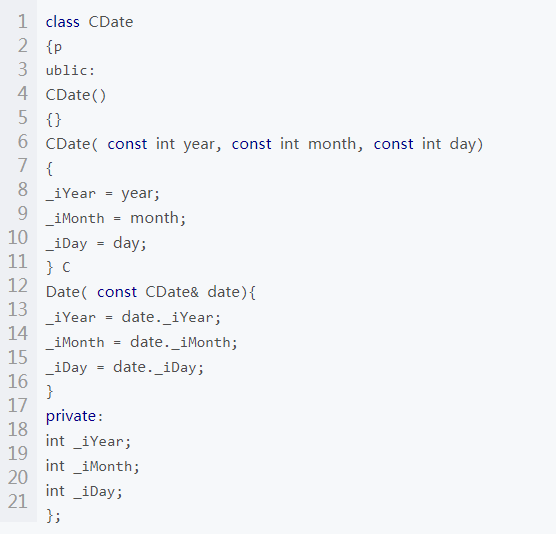

只有單個形參,而且該形參是對本類類型對象的引用(常用const修飾),這樣的構(gòu)造函數(shù)稱為拷貝構(gòu)造函數(shù)。拷貝構(gòu)造函數(shù)是特殊的構(gòu)造函數(shù),創(chuàng)建對象時使用已存在的同類對象來進行初始化,由編譯器自動調(diào)用。

2020-06-29 11:45:48 1870

1870

C++編譯器會默認提供構(gòu)造函數(shù);無參構(gòu)造函數(shù)用于定義對象的默認初始化狀態(tài);拷貝構(gòu)造函數(shù)在創(chuàng)建對象時拷貝對象的狀態(tài);對象的拷貝有淺拷貝和深拷貝兩種方式。

2020-12-24 15:31:02 491

491 在我們前面學習過類中的構(gòu)造函數(shù),以及析構(gòu)函數(shù),那么自然而然,在繼承關(guān)系中,必然是存在著析構(gòu)和構(gòu)造著。一、子類對象的構(gòu)造1、問題的引出如何初始化父類成員?父類構(gòu)造函數(shù)和子類構(gòu)造函數(shù)有什么關(guān)系?2、子類中

2020-12-24 16:10:17 516

516 當類中自定義了構(gòu)造函數(shù),并且析構(gòu)函數(shù)中使用了系統(tǒng)資源(比如說,內(nèi)存的申請,文件打開),那么就需要自定義析構(gòu)函數(shù)了。

2020-12-24 17:20:48 592

592 關(guān)于這個構(gòu)造函數(shù),簡單理解就是在一個類中,有一個函數(shù),它的函數(shù)名稱和類名同名,而且這個構(gòu)造函數(shù)沒有返回值類型的說法( Test()這個函數(shù)就是構(gòu)造函數(shù)了。)

2020-12-24 18:06:46 499

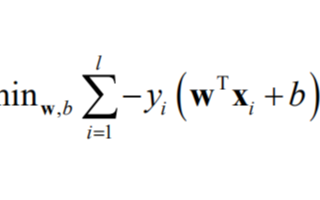

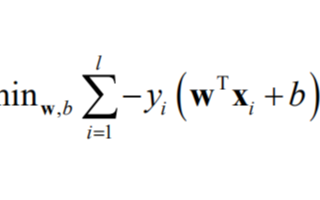

499 時通過最大化獎勵值得到策略函數(shù),然后用策略函數(shù)確定每種狀態(tài)下要執(zhí)行的動作。多任務學習、半監(jiān)督學習的核心步驟之一也是構(gòu)造目標函數(shù)。一旦目標函數(shù)確定,剩下的是求解最優(yōu)化問題,這在數(shù)學上通常有成熟的解決方案。因此

2020-12-26 09:52:10 3808

3808

placement new 就可以解決這個問題。我們構(gòu)造對象都是在一個預先準備好了的內(nèi)存緩沖區(qū)中進行,不需要查找內(nèi)存,內(nèi)存分配的時間是常數(shù);而且不會出現(xiàn)在程序運行中途出現(xiàn)內(nèi) 存不足的異常。所以,placement new非常適合那些對時間要求比較高,長時間運行不希望被打斷的應用程序。

2021-01-19 17:01:16 1770

1770 手冊的這一部分探討了使用SystemVerilog進行驗證,然后查看了使用SystemVerilog的優(yōu)點和缺點。

2021-03-29 10:32:46 23

23 布爾函數(shù)導數(shù)的性質(zhì)在密碼構(gòu)造中起著重要的作用。文中利用布爾函數(shù)導數(shù)的性質(zhì),構(gòu)造了一個新的平衡布爾函數(shù)然后基于平衡布爾函數(shù)與布爾置換的關(guān)系,構(gòu)造出一種新的布爾置換。

2021-06-17 10:58:14 15

15 10 學生類-構(gòu)造函數(shù) (15分)定義一個有關(guān)學生的Student類,內(nèi)含類成員變量: String name、String sex、int age,所有的變量必須為私有(private

2021-12-29 19:05:31 1

1 SystemVerilog casting意味著將一種數(shù)據(jù)類型轉(zhuǎn)換為另一種數(shù)據(jù)類型。在將一個變量賦值給另一個變量時,SystemVerilog要求這兩個變量具有相同的數(shù)據(jù)類型。

2022-10-17 14:35:40 1960

1960 SystemVerilog“struct”表示相同或不同數(shù)據(jù)類型的集合。

2022-11-07 10:18:20 1852

1852 SystemVerilog中的句柄賦值和對象復制的概念是有區(qū)別的。

2022-11-21 10:32:59 523

523 SystemVerilog是一種硬件描述和驗證語言(HDVL),它基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對其進行了擴展,包括擴充了 C語言 數(shù)據(jù)類型、結(jié)構(gòu)、壓縮

2022-12-08 10:35:05 1262

1262 new操作符從自由存儲區(qū)(free store)上為對象動態(tài)分配內(nèi)存空間,而malloc函數(shù)從堆上動態(tài)分配內(nèi)存。自由存儲區(qū)是C++基于new操作符的一個抽象概念,凡是通過new操作符進行內(nèi)存申請

2023-04-03 09:29:01 452

452 在理解拷貝構(gòu)造函數(shù)前,還是有必要回顧下類的構(gòu)造函數(shù)基本概念。類的構(gòu)造函數(shù)是一種特殊的成員函數(shù),它在創(chuàng)建類的對象時執(zhí)行。構(gòu)造函數(shù)的函數(shù)名和類名一致,它不會返回任何類型,同樣返回類型也不是void,一般構(gòu)造函數(shù)用來初始化類的成員變量。

2023-04-19 11:35:06 584

584 寫過Verilog和systemverilog的人肯定都用過系統(tǒng)自定義的函數(shù)$display,這是預定好的,可以直接調(diào)用的功能。

2023-05-16 09:27:02 581

581

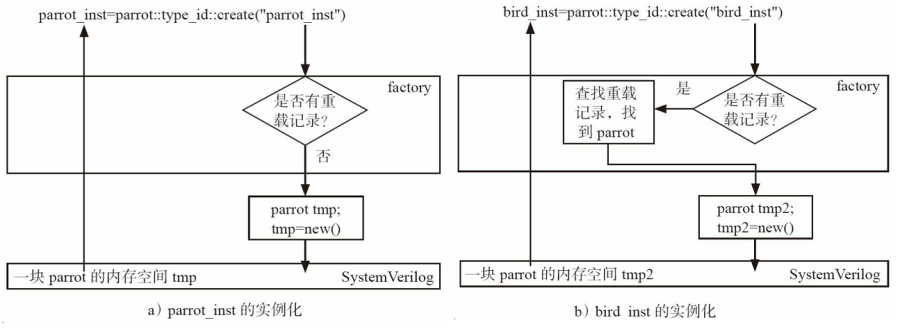

factory機制本質(zhì)是對SystemVerilog中new函數(shù)的重載

2023-05-26 14:55:12 579

579

本文講一下SystemVerilog的time slot里的regions以及events的調(diào)度。SystemVerilog語言是根據(jù)離散事件執(zhí)行模型定義的,由events驅(qū)動。

2023-07-12 11:20:32 775

775

C++11在原有的4個特殊成員函數(shù)(默認構(gòu)造函數(shù)、復制構(gòu)造函數(shù)、復制賦值運算符和析構(gòu)函數(shù))的基礎(chǔ)上新增了移動構(gòu)造函數(shù)和移動賦值運算符。

2023-07-18 16:02:13 255

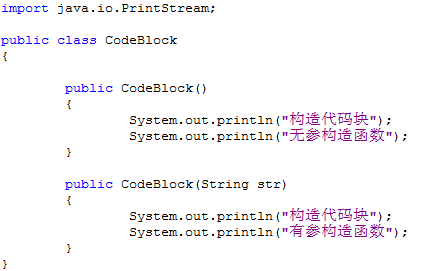

255 在Java中,靜態(tài)代碼塊、構(gòu)造代碼塊、構(gòu)造函數(shù)、普通代碼塊的執(zhí)行順序是一個筆試的考點,通過這篇文章希望大家能徹底了解它們之間的執(zhí)行順序。 1、靜態(tài)代碼塊 ①、格式 在java類中(方法中不能存在靜態(tài)

2023-10-09 15:40:56 370

370

InterruptedException ; boolean remove (Object o) ; 一起來看看,ArrayBlockingQueue 是如何實現(xiàn)的吧。 初識 首先看一下 ArrayBlockingQueue 的主要屬性和構(gòu)造函數(shù)。

2023-10-13 11:36:48 188

188 談到SystemVerilog,很多工程師都認為SystemVerilog僅僅是一門驗證語言,事實上不只如此。傳統(tǒng)的Verilog和VHDL被稱為HDL(Hardware Description

2023-10-19 11:19:19 342

342

我們先來回憶一下JVM系列1的文章中有提到,方法區(qū)存儲每個類的結(jié)構(gòu),比如:運行時常量池、屬性和方法數(shù)據(jù),以及方法和構(gòu)造函數(shù)等數(shù)據(jù)。所以我們這個obj1是存在方法區(qū)的,而new會創(chuàng)建一個對象實例,對象實例是存儲在堆內(nèi)的,于是就有了下面這幅圖(方法區(qū)指向堆 ):

2023-11-01 15:47:53 169

169

本文分享一些SystemVerilog的coding guideline。

2023-11-22 09:17:30 272

272

電子發(fā)燒友App

電子發(fā)燒友App

評論