因項目需要使用到STM32的ADC功能,雖然對ADC的使用并不陌生,但是第一接觸stm32的ADC功能還是有種無從下手的感覺,主要是因為STM32ADC設計較為復雜,一時對相關的專業術語較為生疏,此外固件庫中涉及到的函數雖都進行了分門別類但是還是感覺函數較多,難以很快掌握,現就將個人理解寫出,以便大家共同進步。

一、stm32 ADC特點

認識事物首先還是要從整體上把握,ADC也一樣的道理,STM32的ADC外設提供了非常完善的功能,雖然其中很大一部分不見得能在項目中使用,但加深對其的認識對于合理利用其資源也是非常有必要的。

下面以項目采用的STM32L151為例,其他類型大同小異。

先看原文:

? 12-bit, 10-bit, 8-bit or 6-bit configurable resolution

? Interrupt generation at the end of regular conversions, end of injected conversions, and in case of analog watchdog or overrun events (for regular conversions)

//在規則轉換結束、注入轉換結束以及模擬看門狗溢出和overrun事件(規則轉換模式)發生時能產生中斷

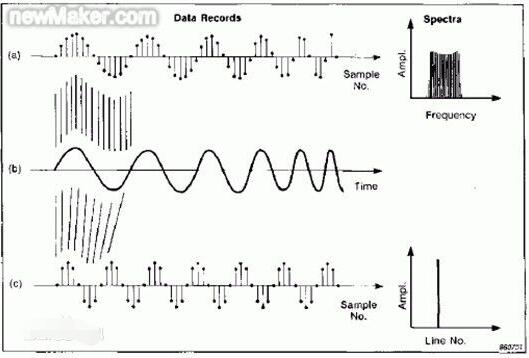

? Single and continuous conversion modes //有單次和連續轉換模式

? Scan mode for automatic conversions in a fully programmable order //在自動轉換中支持完成可編程的掃描模式

? Programmable data alignment with in-built data coherency //數據對齊方式可編程

? Programmable and individual sampling time for each ADC channel //可以為每個通道設置獨立的采樣時間

? External trigger option with configurable edge detection for both regular and injected

conversions //外部觸發模式對規則和注入轉換模式均支持可配置的邊沿觸發方式

? Discontinuous mode //非連續模式

? ADC conversion time: 1 μs at full speed (ADC clocked at 16 MHz) down to 4 μs at low speed (ADC clocked at 4 MHz), independent of the APB clock//最低采樣時間

? Automatic power-up/power-down to reduce the power consumption//自動的上下電便于節能

? ADC supply requirements:

– 2.4 V to 3.6 V at full speed or with reference zooming (VREF+ 《 VDDA)

– down to 1.8 V at slower speeds //工作電壓范圍

? ADC input range: VREF– ≤ VIN ≤ VREF+

? Automatic programmable hardware delay insertion between conversions

? DMA request generation during regular channel conversion //規則轉換支持DMA

從官方的描述中可以了解到STM32ADC所提供的強大功能,及一些工作特性,那么如何才能使用這些功能呢?

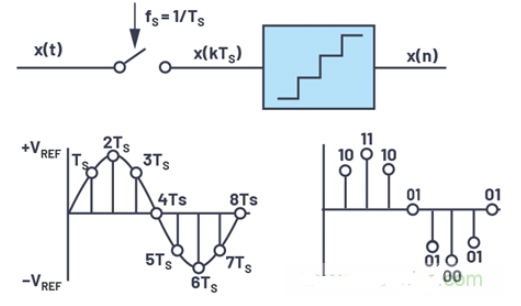

ADC轉換就是輸入模擬的信號量,單片機轉換成數字量。讀取數字量必須等轉換完成后,完成一個通道的讀取叫做采樣周期。采樣周期一般來說=轉換時間+讀取時間

轉換時間=采樣時間+12.5個時鐘周期。采樣時間是你通過寄存器告訴STM32采樣模擬量的時間,設置越長越精確。

二、STM32 ADC采樣頻率時間、周期、計算方法分析

1. :先看一些資料,確定一下ADC的時鐘:

(1),由時鐘控制器提供的ADCCLK時鐘和PCLK2(APB2時鐘)同步。CLK控制器為ADC時鐘提供一個專用的可編程預分頻器。

(2) 一般情況下在程序 中將 PCLK2 時鐘設為 與系統時鐘 相同

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);

/* PCLK2 = HCLK */

RCC_PCLK2Config(RCC_HCLK_Div1);

/* PCLK1 = HCLK/2 */

RCC_PCLK1Config(RCC_HCLK_Div2);

(3)在時鐘配置寄存器(RCC_CFGR) 中 有 為ADC時鐘提供一個專用的可編程預分器

位15:14 ADCPRE:ADC預分頻

由軟件設置來確定ADC時鐘頻率

00:PCLK2 2分頻后作為ADC時鐘

01:PCLK2 4分頻后作為ADC時鐘

10:PCLK2 6分頻后作為ADC時鐘

11:PCLK2 8分頻后作為ADC時鐘

我們可對其進行設置 例如:

/* ADCCLK = PCLK2/4 */

RCC_ADCCLKConfig(RCC_PCLK2_Div4);

另外 還有 ADC 時鐘使能設置

/* Enable ADC1, ADC2 and GPIOC clock */

RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1 | RCC_APB2Periph_ADC2 |

RCC_APB2Periph_GPIOC, ENABLE);

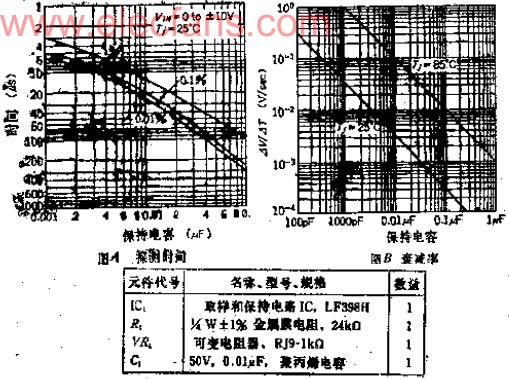

(4)16.7 可編程的通道采樣時間

ADC 使用若干個ADC_CLK 周期對輸入電壓采樣,采樣周期數目可以通過ADC_SMPR1和ADC_SMPR2寄存器中的SMP[2:0]位而更改。每個通道可以以不同的時間采樣。

總轉換時間如下計算:

TCONV(轉換時間) = 采樣時間+ 12.5 個周期

例如:

當ADCCLK=14MHz 和 1.5周期的采樣時間:

TCONV = 1.5 + 12.5 = 14周期= 1μs

SMPx[2:0]:選擇通道x的采樣時間

這些位用于獨立地選擇每個通道的采樣時間。在采樣周期中通道選擇位必須保持不變。

000:1.5周期100:41.5周期

001:7.5周期101:55.5周期

010:13.5周期110:71.5周期

011:28.5周期111:239.5周期

注:

– ADC1的模擬輸入通道16和通道17在芯片內部分別連到了溫度傳感器和VREFINT。

– ADC2的模擬輸入通道16和通道17在芯片內部連到了VSS。

2. 具體分析如下:

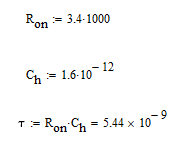

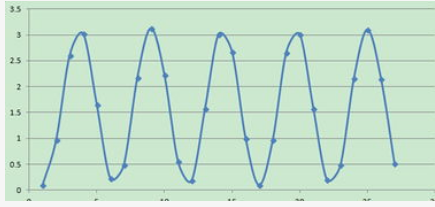

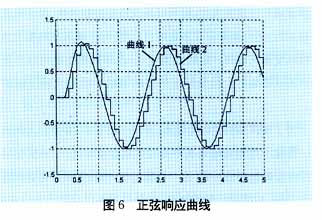

(1)我們的輸入信號是50Hz (周期為20ms),初步定為1周期200個采樣點,(注:一周期最少采20個點,即采樣率最少為1k) ,每2個 采樣點間隔為 20ms /200 = 100 us

ADC可編程的通道采樣時間 我們選最小的 1.5 周期,則 ADC采樣周期一周期大小為

100us /1.5=66us 。 ADC 時鐘頻率為 1/66us =15 KHz。

ADC可編程的通道采樣時間 我們選71.5 周期,則 ADC采樣周期一周期大小為

(100us /71.5) 。 ADC 時鐘頻率為 7.15MHz。

(2)接下來我們要確定系統時鐘:我們 用的是 8M Hz 的外部晶振做時鐘源(HSE),估計得 經過 PLL倍頻 PLL 倍頻系數分別為2的整數倍,最大72 MHz。為了 提高數據 計算效率,我們把系統時鐘定為72MHz,(PLL 9倍頻)。則PCLK2=72MHz,PCLK1=36MHz;

我們通過設置時鐘配置寄存器(RCC_CFGR) 中 有 為ADC時鐘提供一個專用的可編程預分器,將PCLK2 8 分頻后作為ADC 的時鐘,則可知ADC 時鐘頻率為 9MHz

從手冊可知: ADC 轉換時間:

STM32F103xx增強型產品:ADC時鐘為56MHz時為1μs(ADC時鐘為72MHz為1.17μs)

(3)由以上分析可知:不太對應,我們重新對以上中 內容調整,提出如下兩套方案:

方案一:我們的輸入信號是50Hz (周期為20ms),初步定為1周期2500個采樣點,(注:一周期最少采20個點,即采樣率最少為1k) ,每2個 采樣點間隔為 20ms /2500 = 8 us

ADC可編程的通道采樣時間 我們選71.5周期,則 ADC采樣周期一周期大小為

8us /71.5 。 ADC時鐘頻率約為 9 MHz。

將PCLK2 8 分頻后作為ADC 的時鐘,則可知ADC 時鐘頻率為 9MHz

方案二:我們的輸入信號是50Hz (周期為20ms),初步定為1周期1000個采樣點,(注:一周期最少采20個點,即采樣率最少為1k) ,每2個 采樣點間隔為 20ms /1000= 20 us

ADC可編程的通道采樣時間 我們選239.5周期,則 ADC采樣周期一周期大小為

20us /239.5 。 ADC時鐘頻率約為 12 MHz。

將PCLK2 6 分頻后作為ADC 的時鐘,則可知ADC 時鐘頻率為 12MHz

電子發燒友App

電子發燒友App

評論