DAC8800:八進(jìn)制8位D/A轉(zhuǎn)換器數(shù)據(jù)表

2021-05-22 08:00:06 4

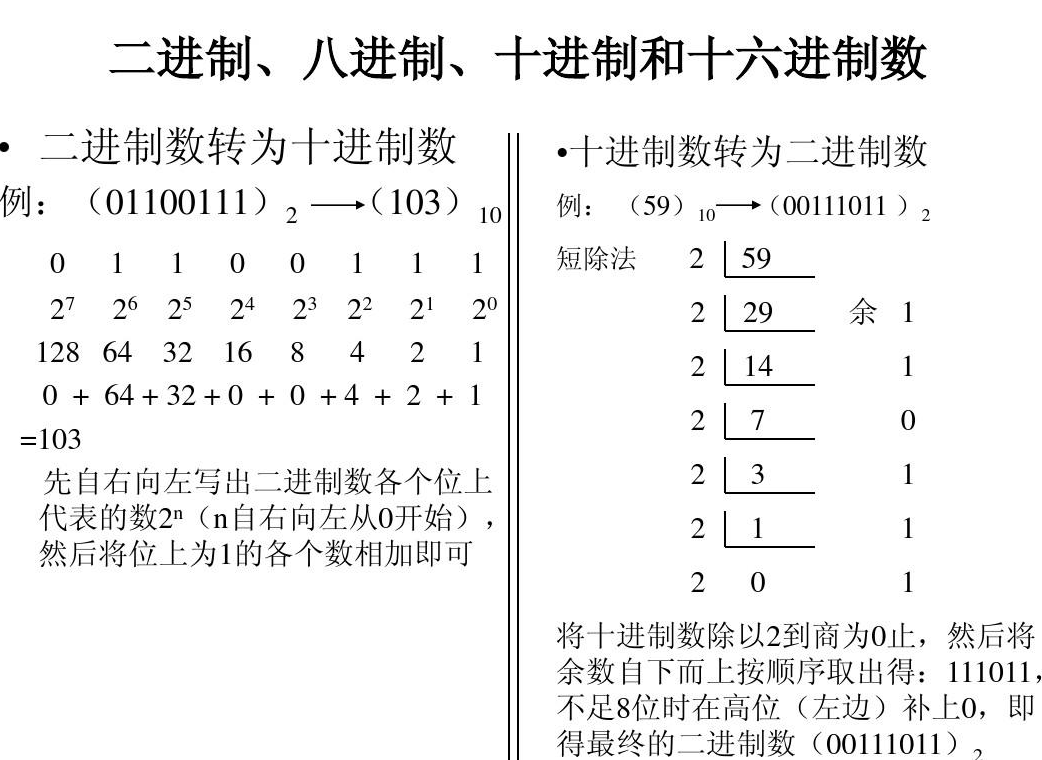

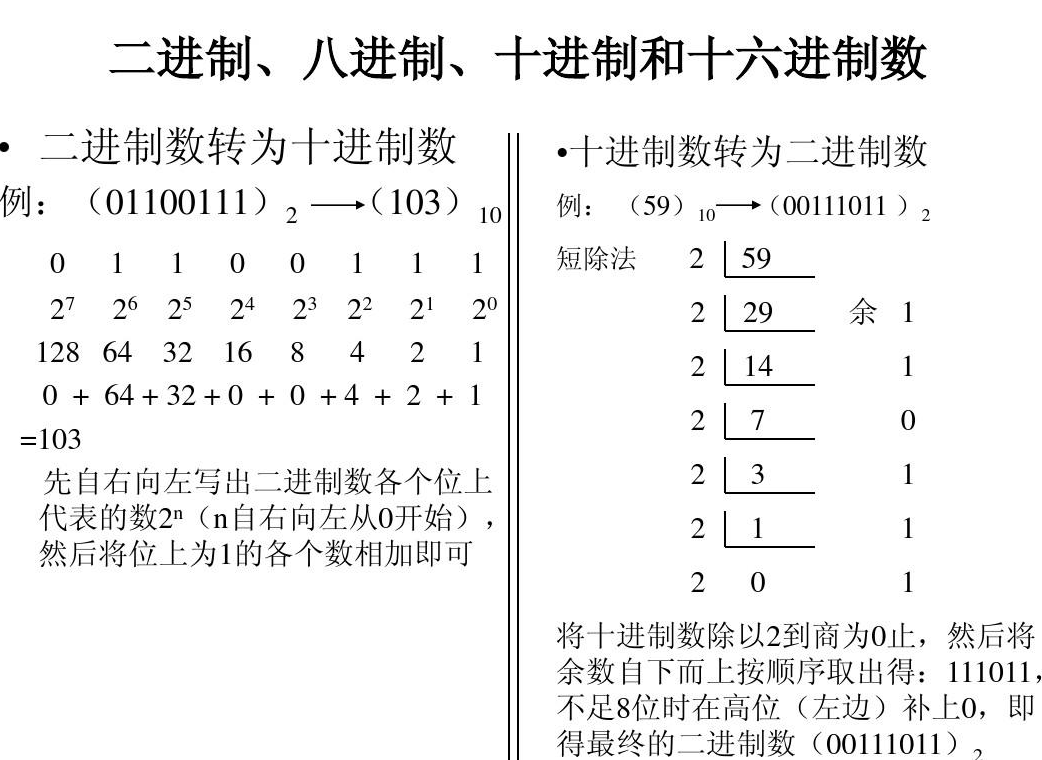

4 不同進(jìn)位數(shù)之間的轉(zhuǎn)換方法1. 二進(jìn)制與八進(jìn)制之間的相互轉(zhuǎn)換 由于 23= 8, 所以 3 位二進(jìn)制數(shù)相當(dāng)于 1 位八進(jìn)制數(shù), 它們之間是完全對(duì)應(yīng)的。因此, 只要把 1 位八進(jìn)制數(shù)字化成 3 位

2019-12-10 11:58:58

八進(jìn)制8位DA轉(zhuǎn)換器DAC-8800 TrimDAC?的AN-142電壓調(diào)整應(yīng)用

2021-06-17 16:49:10 2

2 八進(jìn)制電平,八進(jìn)制電平是什么意思

在二進(jìn)制數(shù)字通信系統(tǒng)中,每個(gè)碼元或每個(gè)符號(hào)只能是“1”和“0”兩個(gè)狀態(tài)之一。若將每個(gè)碼元可能取的狀態(tài)

2010-03-17 17:05:54 22501

22501 AN-142:八進(jìn)制8位D/A轉(zhuǎn)換器DAC-8800TrimDAC?的電壓調(diào)整應(yīng)用

2021-05-09 10:50:10 0

0 八進(jìn)制透明鎖存器(三態(tài));八進(jìn)制 D 觸發(fā)器(三態(tài))-74F373_374

2023-03-03 20:05:16 0

0 八進(jìn)制編號(hào)系統(tǒng)的主要特征是 0 到 7 ,每個(gè)數(shù)字的權(quán)重或值從最低有效位(LSB)開始僅為8。在計(jì)算的早期階段,八進(jìn)制數(shù)和八進(jìn)制編號(hào)系統(tǒng)非常適用于計(jì)數(shù)輸入和輸出,因?yàn)樗挠?jì)數(shù)為8,輸入和輸出的計(jì)數(shù)為8,一次一個(gè)字節(jié)。

2019-06-24 10:03:33 3764

3764

二進(jìn)制數(shù)與八進(jìn)制數(shù)的相互轉(zhuǎn)換

(1)二進(jìn)制數(shù)轉(zhuǎn)換為八進(jìn)制數(shù): 將二進(jìn)制數(shù)由小數(shù)點(diǎn)開始,整數(shù)部分向左,小數(shù)部分向右,每3位分

2009-09-24 11:27:30 16868

16868 電子發(fā)燒友網(wǎng)站提供《如何將十進(jìn)制數(shù)轉(zhuǎn)換為八進(jìn)制數(shù).zip》資料免費(fèi)下載

2023-02-02 14:59:47 0

0 AD9681:八進(jìn)制、14位、125 MSPS、串行LVDS、1.8 V模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

2021-05-09 12:12:58 1

1 AD9637:八進(jìn)制、12位、40/80 MSPS、串行LVDS、1.8 V模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

2021-04-16 20:14:42 1

1 十六進(jìn)制和八進(jìn)制

由于當(dāng)二進(jìn)制數(shù)的位數(shù)很多時(shí)書寫很麻煩,因此為了減少書寫一個(gè)數(shù)字的位數(shù),在計(jì)算機(jī)的資料中經(jīng)常采用十六進(jìn)制或八進(jìn)制數(shù)來表示二進(jìn)制數(shù)。

2009-04-06 23:54:07 2517

2517

14位125 Msps,八進(jìn)制ADC

2021-04-20 11:33:59 1

1 LTC2978:帶EEPROM數(shù)據(jù)表的八進(jìn)制數(shù)字電源管理器

2021-04-17 10:36:57 1

1 具有三態(tài)輸出的八進(jìn)制透明鎖存器-HEF40373B

2023-02-21 19:20:49 0

0 LTC2910:八進(jìn)制正/負(fù)電壓監(jiān)視器數(shù)據(jù)表

2021-04-17 15:18:15 0

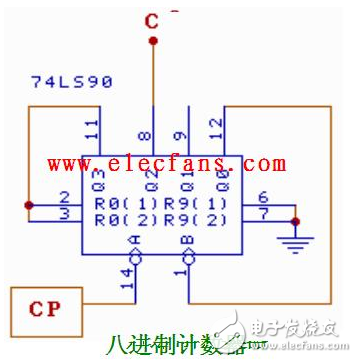

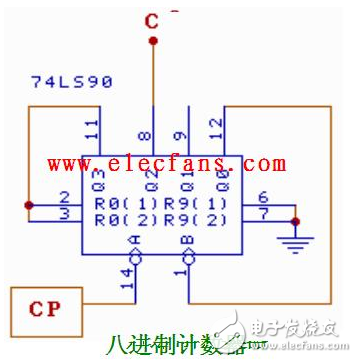

0 本文為大家?guī)硭膫€(gè)八進(jìn)制計(jì)數(shù)器設(shè)計(jì)方案。

2018-01-17 13:37:39 81874

81874

集成緩沖器的18位八進(jìn)制SAR ADC

2021-04-21 08:54:29 3

3 3.3 V 八進(jìn)制緩沖器/線路驅(qū)動(dòng)器;三態(tài)-74LVT241

2023-02-20 20:05:30 0

0 帶方向引腳的 3.3 V 八進(jìn)制收發(fā)器;三態(tài)-74LVT245B

2023-02-15 20:07:43 0

0 帶方向引腳的 3.3 V 八進(jìn)制收發(fā)器;三態(tài)-74LVT245

2023-02-15 20:05:07 0

0 AD9277:八進(jìn)制LNA/VGA/AAF/ADC和CW I&Q解調(diào)器數(shù)據(jù)表

2021-04-28 19:41:57 0

0 本文主要詳細(xì)闡述了二進(jìn)制、八進(jìn)制、十進(jìn)制、十六進(jìn)制之間的轉(zhuǎn)換步驟教程。

2018-08-22 16:37:53 10279

10279 3.3 V 八進(jìn)制 D 型透明鎖存器;三態(tài)-74LVT573

2023-02-15 20:08:01 0

0 SMP08:具有多路復(fù)用輸入數(shù)據(jù)表的八進(jìn)制采樣保持

2021-04-27 21:11:02 4

4 AD7839:八進(jìn)制13位并行輸入電壓輸出DAC數(shù)據(jù)表

2021-04-17 08:07:10 1

1 AD8842:8位八進(jìn)制、4象限乘法、CMOS TrimDAC數(shù)據(jù)表

2021-04-16 14:34:13 7

7 AD75089:?jiǎn)纹?b style="color: red">八進(jìn)制12位DACPORT數(shù)據(jù)表

2021-04-16 12:48:11 1

1 AD7841:八進(jìn)制14位并行輸入電壓輸出DAC數(shù)據(jù)表

2021-04-14 10:37:15 0

0 ADS52X/ADS524X系列器件是高性能八進(jìn)制 四通道模數(shù)轉(zhuǎn)換器(ADC),是最高系統(tǒng)密度的理想選擇。串行低電壓差分信號(hào)(LVDS)輸出減少了所需的I/O接口的數(shù)量、功率和整體封裝尺寸。這些設(shè)備

2018-05-18 11:47:09 5

5 電子發(fā)燒友網(wǎng)站提供《74AHC574/74AHCT574八進(jìn)制D型觸發(fā)器手冊(cè).pdf》資料免費(fèi)下載

2023-09-27 11:04:02 0

0 SMP18:具有多路復(fù)用輸入數(shù)據(jù)表的八進(jìn)制采樣保持

2021-04-18 10:53:38 0

0 本文匯總和定義模/數(shù)轉(zhuǎn)換器(ADC)和數(shù)/模轉(zhuǎn)換器(DAC)領(lǐng)域常用的技術(shù)術(shù)語。

2022-04-15 12:59:51 2111

2111 DAC128S085 EB設(shè)計(jì)套件(符合DAC128S085評(píng)估板和該用戶指南)旨在簡(jiǎn)化國家半導(dǎo)體DAC128S085 12位、DAC108S085 10位和DAC08S085 8位八進(jìn)制微功耗

2018-05-10 15:30:44 50

50 3.3 V 八進(jìn)制收發(fā)器,帶 30 歐姆終端電阻;3 - 狀態(tài)-74LVT_LVTH2245

2023-02-15 19:52:20 0

0 SN74LVCC3245A設(shè)備是8位(八進(jìn)制)非轉(zhuǎn)換總線收發(fā)器,包含兩個(gè)獨(dú)立的供電軌。B端口設(shè)計(jì)用于跟蹤接收3 V至5.5 V電壓的VOCB,而APort設(shè)計(jì)用于跟蹤工作在2.3 V至3.6 V電壓下的VCCA。這允許從3.3 V轉(zhuǎn)換為5 V系統(tǒng)環(huán)境,反之亦然,從A轉(zhuǎn)換為A。

2019-02-13 08:00:00 6

6 3.3 V 八進(jìn)制緩沖器/線路驅(qū)動(dòng)器;三態(tài)-74LVT_LVTH244A

2023-02-15 19:52:33 0

0 ADG714/ADG715:CMOS、低壓串控、八進(jìn)制SPST開關(guān)數(shù)據(jù)表

2021-05-10 13:42:22 0

0 3.3 V 八進(jìn)制緩沖器/線路驅(qū)動(dòng)器;三態(tài)-74LVT_LVTH244A_Q100

2023-02-17 19:42:10 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是LTC2600八進(jìn)制16位DAC的電路原理圖免費(fèi)下載。

2019-12-16 18:05:00 16

16 模_數(shù)轉(zhuǎn)換器設(shè)計(jì)指南 第十六版、模_數(shù)轉(zhuǎn)換器設(shè)計(jì)指南 第十八版。

2016-03-04 16:03:38 6

6 UG-867:評(píng)估AD5629R/AD5669R,八進(jìn)制,16/12位,密度DAC

2021-05-12 16:10:17 6

6 AD9271:八進(jìn)制LNA/VGA/AAF/ADC和交叉點(diǎn)交換機(jī)數(shù)據(jù)表

2021-04-28 18:51:52 0

0 AD9675:采用JESD204B的八進(jìn)制超聲波AFE數(shù)據(jù)表

2021-04-16 10:09:00 8

8 3.3 V 八進(jìn)制緩沖器/線路驅(qū)動(dòng)器;三態(tài)-74LVT_LVTH244B

2023-02-15 19:55:24 0

0 LTC2991:八進(jìn)制I2C電壓、電流和溫度監(jiān)視器數(shù)據(jù)表

2021-04-22 13:59:09 0

0 LTC2320-12:八進(jìn)制,12位+符號(hào),1.5Msps/CH同步采樣ADC數(shù)據(jù)表

2021-05-14 21:16:02 1

1 UG-155:AD5668八進(jìn)制16位串行電壓輸出DAC評(píng)估板

2021-04-19 10:31:25 8

8 LTC2320-14:八進(jìn)制,14位+符號(hào),1.5Msps/CH同步采樣ADC數(shù)據(jù)表

2021-04-18 17:33:15 3

3 DAC8840:8位、八進(jìn)制、4象限乘法、CMOS TrimDAC數(shù)據(jù)表

2021-05-09 12:17:43 10

10 DAC8841:8位八進(jìn)制2象限乘法CMOS TrimDAC數(shù)據(jù)表

2021-05-08 10:06:08 5

5 AD9252:八進(jìn)制、14位、50 MSPS、串行LVDS、1.8 V ADC數(shù)據(jù)表

2021-04-27 21:02:37 0

0 AD9212:八進(jìn)制,10位,40 MSPS/65 MSPS,串行LVDS,1.8 V ADC數(shù)據(jù)表

2021-04-18 09:23:03 7

7 AD7228A:LC2MOS八進(jìn)制8位DAC數(shù)據(jù)表

2021-04-29 16:15:27 3

3 UG1459:用數(shù)字解調(diào)恢復(fù)評(píng)估AD9670八進(jìn)制超聲AFE-AD9670

2021-05-11 10:40:30 7

7 基于單通道ADS1271,ADS1278(八進(jìn)制)是一個(gè)24位的δ∑(aミ) 模擬數(shù)字轉(zhuǎn)換器(ADC),數(shù)據(jù)速率高達(dá)每秒128 k個(gè)采樣點(diǎn)(SPS),允許同時(shí)對(duì)八個(gè)通道進(jìn)行采樣。

2022-10-19 16:10:12 15

15 進(jìn)制轉(zhuǎn)換器應(yīng)用程序免費(fèi)下載可以轉(zhuǎn)換十六進(jìn)制十進(jìn)制和二進(jìn)制。

2019-03-28 11:32:52 21

21 DAC7558是一個(gè)12位,八進(jìn)制通道,電壓輸出DAC具有出色的線性和單調(diào)性。它的專有架構(gòu)最小化了不希望的瞬態(tài),例如代碼到代碼故障和通道到通道串?dāng)_。

2018-05-15 09:30:17 15

15 AD5676:帶SPI接口的八進(jìn)制16位NanoDAC+數(shù)據(jù)表

2021-05-12 19:21:13 12

12 AD7568:LC2MOS八進(jìn)制12位DAC數(shù)據(jù)表

2021-04-26 11:50:27 7

7 AD9671:帶數(shù)字解調(diào)器的八進(jìn)制超聲波AFE,JESD204B數(shù)據(jù)表

2021-04-29 16:13:06 8

8 DDC118是一個(gè)20位,八進(jìn)制通道,電流輸入模數(shù)(A/D)轉(zhuǎn)換器。它結(jié)合了電流電壓和A/D轉(zhuǎn)換,使得八個(gè)低電平電流輸出器件,如發(fā)光二極管,可以直接連接到其輸入端并數(shù)字化。

2018-05-24 16:52:52 8

8

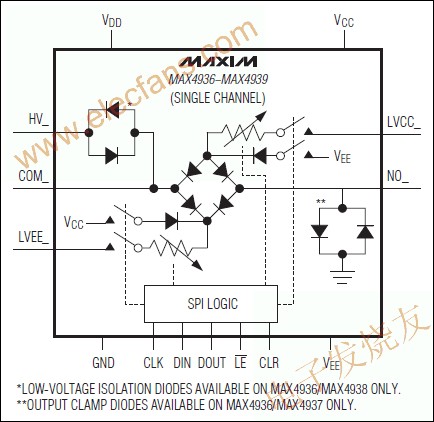

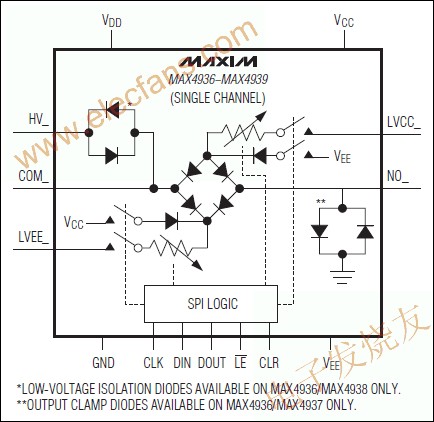

MAX4936 - MAX4939是八進(jìn)制,高電壓,發(fā)射/接收的開關(guān)。是基于一個(gè)二極管橋拓?fù)浣Y(jié)構(gòu),以及目前在二極管橋金

2011-03-13 22:32:49 3663

3663

電子發(fā)燒友網(wǎng)站提供《使用Arduino和OLED顯示器的二進(jìn)制到十進(jìn)制轉(zhuǎn)換器.zip》資料免費(fèi)下載

2022-10-31 14:30:12 6

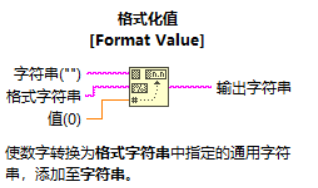

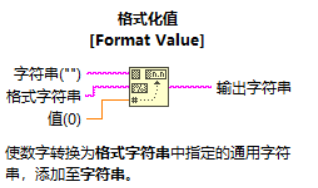

6 要了解數(shù)值轉(zhuǎn)化,首先要了解各個(gè)進(jìn)制的轉(zhuǎn)化代碼,這里附上利用LABVIEW中“格式化值”整型數(shù)轉(zhuǎn)化代碼。 十進(jìn)制轉(zhuǎn)化為二進(jìn)制。 2. 十進(jìn)制轉(zhuǎn)化為八進(jìn)制 3.十進(jìn)制轉(zhuǎn)化為十六進(jìn)制 4.二進(jìn)制轉(zhuǎn)化

2022-02-07 15:29:04 27194

27194

PCtoLCD2002字模轉(zhuǎn)換器

2013-09-04 15:29:28 139

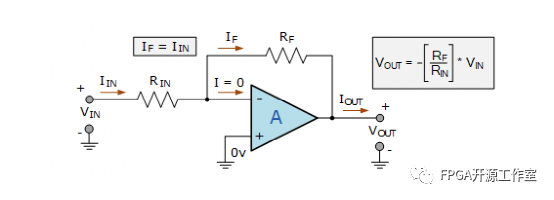

139 二進(jìn)制加權(quán)數(shù)模轉(zhuǎn)換器是一種將數(shù)字二進(jìn)制數(shù)轉(zhuǎn)換成與數(shù)字?jǐn)?shù)值成比例的等效模擬輸出信號(hào)的數(shù)據(jù)轉(zhuǎn)換器。

2023-06-29 11:34:47 405

405

74LV245是一種低壓硅柵CMOS器件,其引腳和功能與74HC245和74HCT 245兼容。74LV245是一個(gè)八進(jìn)制收發(fā)器,在發(fā)送和接收兩個(gè)方向上都有不可逆的3態(tài)總線兼容輸出。發(fā)送/接收(DIR)輸入控制方向,而輸出啟用(OE)輸入使級(jí)聯(lián)變得容易。引腳OE控制輸出,使總線有效隔離。

2019-12-12 08:00:00 3

3 LTC2345-16:八進(jìn)制、16位、200ksps差分軟量程ADC,支持寬輸入共模范圍數(shù)據(jù)表

2021-05-16 18:17:33 1

1 LTC2345-18:八進(jìn)制、18位、200ksps差分軟量程ADC,支持寬輸入共模范圍數(shù)據(jù)表

2021-05-17 11:22:11 3

3 MC74LCX245是高性能、相八進(jìn)制端收發(fā)器操作從2.0到5.5 v供應(yīng)。 高阻抗TTL兼容的輸入顯著降低電流負(fù)載輸入驅(qū)動(dòng)程序而TTL兼容輸出提供改進(jìn)的開關(guān)噪聲的性能。 V我規(guī)范的5.5 v可以

2017-04-11 09:28:31 5

5

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

4

4 2

2 22501

22501 0

0 0

0 3764

3764

16868

16868 0

0 1

1 1

1 2517

2517

1

1 0

0 81874

81874

0

0 0

0 0

0 0

0 10279

10279 4

4 1

1 7

7 1

1 0

0 5

5 0

0 0

0 2111

2111 50

50 0

0 6

6 0

0 0

0 0

0 16

16 6

6 6

6 0

0 8

8 0

0 0

0 1

1 8

8 3

3 10

10 5

5 0

0 7

7 3

3 7

7 15

15 21

21 15

15 12

12 7

7 8

8 8

8 3663

3663

6

6 27194

27194

405

405

3

3 1

1 3

3 5

5

評(píng)論