賽靈思 Virtex UltraScale 器件是業(yè)界首款量產(chǎn)的 20nm 高端產(chǎn)品系列,其為客戶帶來了“領(lǐng)先一代”的價值優(yōu)勢。讓 400G 和 500G 應(yīng)用從此有了業(yè)界唯一的單芯片解決方案。另外,面向有線通信、測試測量、航空航天以及數(shù)據(jù)中心等多種應(yīng)用領(lǐng)域,Virtex UltraScale 器件也為其帶來了高性能、高系統(tǒng)集成和高帶寬的實現(xiàn)方案。

Virtex UltraScale 器件在 20nm 提供最佳性能與集成,包含串行 I/O 帶寬和邏輯容量。作為在 20nm 工藝節(jié)點的業(yè)界僅有高端 FPGA,此系列適合從 400G 網(wǎng)絡(luò)到大型 ASIC 原型設(shè)計/仿真的應(yīng)用。

| 價值 | 優(yōu)勢 |

| 可編程系統(tǒng)集成 |

多達(dá)5.5M系統(tǒng)邏輯單元,采用20nm工藝,和第二代3D IC技術(shù); 集成式100G以太網(wǎng)MAC和150G Interlaken內(nèi)核。 |

| 提升的系統(tǒng)性能 |

高利用率使速度提升兩個等級; 30G 收發(fā)器: 用于芯片對芯片、芯片對光纖和 28G 背板的 30G 收發(fā)器; 功耗減半的 16G 背板收發(fā)器; 2400Mb/s DDR4 可穩(wěn)定工作在不同 PVT 條件下。 |

| BOM 成本消減 |

成本降低達(dá) 50% – 是 Nx100G 系統(tǒng)每端口成本的1/2; VCXO 與 fPLL (分頻鎖相環(huán)) 的集成可降低時鐘組件成本; 中間檔速率等級芯片可支持 2400 Mb/s DDR4。 |

| 總功耗消減 |

較之上一代,達(dá) 40% 功耗降低; 通過 的類似于 ASIC 的時鐘實現(xiàn)精細(xì)粒度時鐘門控功能; 增強型系統(tǒng)邏輯單元封裝減小動態(tài)功耗。 |

| 加速設(shè)計生產(chǎn)力 |

與 Kintex UltraScale 器件引腳兼容,可擴展性高; 從 20nm 平面到 16nm FinFET 的無縫引腳遷移; 與 Vivado Design Suite 協(xié)同優(yōu)化,加快設(shè)計收斂。 |

圖文:賽靈思 Virtex UltraScale 器件榮膺 2015 年度《電子產(chǎn)品世界》編輯推薦獎—最佳 FPGA 獎。

圖文:賽靈思渠道業(yè)務(wù)拓展經(jīng)理張寧接受獎杯。

關(guān)于 20nm Virtex UltraSclae 器件

賽靈思UltraScale器件擁有業(yè)界唯一的ASIC級可編程架構(gòu)、Vivado ASIC增強型設(shè)計套件和UltraFast設(shè)計方法,可提供各種ASIC級的優(yōu)勢。UltraScale產(chǎn)品系列采用臺積公司 (TSMC)的20SoC工藝技術(shù),所需功耗僅為目前市場上解決方案的一半, 但卻將系統(tǒng)性能和集成度提升了2倍以上。這些器件同時還采用了下一代互聯(lián)技術(shù)、類ASIC時鐘、更強的的邏輯結(jié)構(gòu)、第二代量產(chǎn)質(zhì)量級的3D IC技術(shù)。不僅突破了系統(tǒng)級的瓶頸問題,而且在不降低性能的同時讓器件保持了更高的利用率。

關(guān)于 2015 年度電子產(chǎn)品世界編輯推薦獎

該獎項由中國科技核心期刊《電子產(chǎn)品世界》雜志及網(wǎng)站(EEPW.com.cn) 舉辦的年度評選活動,旨在遴選過去一年中在電子工程方面涌現(xiàn)的最具代表性的新技術(shù)、新產(chǎn)品和新應(yīng)用。評獎借助媒體及行業(yè)從業(yè)者的多方視角,對一年來電子產(chǎn)業(yè)中出現(xiàn)的最新技術(shù)和熱門產(chǎn)品進(jìn)行一次總結(jié)和集中展示,最后由技術(shù)專家與電子工程師投票共同決定各個獎項歸屬。本次評選吸引了行業(yè)內(nèi)70余家企業(yè)的參與。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606036 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3454瀏覽量

106249 -

有線通信

+關(guān)注

關(guān)注

0文章

43瀏覽量

12725

發(fā)布評論請先 登錄

相關(guān)推薦

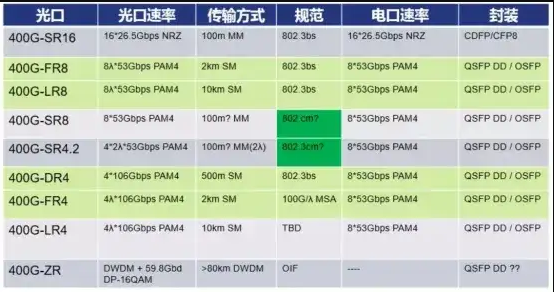

Mellanox CX7網(wǎng)卡適用的400G光模塊型號

400G ZR光模塊-高速長距離傳輸解決方案

400G 網(wǎng)絡(luò)如何測試

400G光模塊應(yīng)用:數(shù)據(jù)中心與云計算的新動力

400G BASE-SR16能帶給我們哪些有關(guān)高速網(wǎng)絡(luò)升級的啟示

400G光模塊有哪些分類

400G QSFP-DD ER4 光模塊概述

三種封裝形式下的400G光模塊概述

400G SR4光模塊:開啟高速網(wǎng)絡(luò)新時代

400G光模塊型號介紹

全方位了解400G光模塊

mpo預(yù)端接光纜可以支持100G或400G光網(wǎng)絡(luò)嗎

400G光模塊已經(jīng)部署,需求將進(jìn)一步擴大

400G QSFP-DD ER8光模塊最新解決方案

深入解析400G QSFP-DD LR4光模塊性能優(yōu)勢

賽靈思為客戶帶來了價值優(yōu)勢,讓400G和500G應(yīng)用有了單芯片解決方案

賽靈思為客戶帶來了價值優(yōu)勢,讓400G和500G應(yīng)用有了單芯片解決方案

評論