FPGA的實(shí)現(xiàn)技術(shù)

按傳統(tǒng)看法,F(xiàn)PGA使用內(nèi)存技術(shù)來存儲FPGA需要的邏輯配置。目前在用的有四種技術(shù)實(shí)現(xiàn)方式,每種都有其優(yōu)缺點(diǎn):基于SRAM的FPGA,帶內(nèi)部閃存的SRAM,基于閃存的,和反熔絲(又稱OTP,因?yàn)樗鼈儍H可編程一次)。

?基于SRAM的FPGA將邏輯單元配置文件存儲在靜態(tài)存儲器中,而靜態(tài)存儲器則由鎖在器陣列組成。由于SRAM是易失性,這種類型的FPGA必須在每次系統(tǒng)啟動時重新編程。存在兩種基本的編程模式:

o主模式,此時FPGA從外部存儲源讀取的配置數(shù)據(jù),比如從外部閃存芯片。

o從模式,此時FPGA由一個外部主設(shè)備來配置,比如由一個處理器。通常情況下,主要通過一個專用的配置界面或通過使用邊界掃描(JTAG)接口來完成。

o帶有內(nèi)部閃存的基于SRAM的FPGA省去了外部非易失性存儲的需求,所謂內(nèi)部閃存包含了內(nèi)部閃存塊。

o純正的基于Flash的FPGA采用Flash作為一個主要存儲源來進(jìn)行配置存儲,因此不需要外部非易失性存儲器。該技術(shù)比基于SRAM的FPGA耗電少,更耐輻射的影響。

o基于反熔絲(OTP)的FPGA與前面提到的技術(shù)差異很大,因?yàn)樗鼈儍H可編程一次。 (反熔絲器件最初不傳導(dǎo)電流,但可以燒寫成導(dǎo)通狀態(tài))。

當(dāng)前基于SRAM的FPGA密度最高,但功耗也大,需要一個外部非易失性存儲器來存儲配置數(shù)據(jù)流。帶有內(nèi)置閃存模塊的基于SRAM的FPGA不需要外部配置存儲器。相較于基于SRAM的技術(shù)來說,基于閃存和反熔絲的FPGA的功耗要小得多。

內(nèi)嵌處理器內(nèi)核

可編程器件最初是為了替代膠連邏輯,但隨著門密度的增長,F(xiàn)PGA和CPLD廠商開始加入獨(dú)特功能的電路,來增強(qiáng)其未分配的門和邏輯的功能。這就導(dǎo)致了可編程芯片(SOPC)的出現(xiàn),其中包含處理器這樣復(fù)雜器件的整個系統(tǒng)都被集成在單個可編程邏輯器件中。

今天,大多數(shù)FPGA和CPLD廠商提供一系列產(chǎn)品,供應(yīng)MCU和其它IP核功能。使用內(nèi)核使得系統(tǒng)設(shè)計人員接觸到熟悉的開發(fā)工具集、操作系統(tǒng)和適用應(yīng)用需求的可調(diào)性能。

有兩種內(nèi)核——硬核和軟核。軟核按邏輯功能描述——并非物理實(shí)現(xiàn)——并且一般由HDL代碼組成。硬核,如其名稱所示,帶物理實(shí)現(xiàn)。當(dāng)與FPGA和CPLD一同使用時,硬核通常稱為嵌入式內(nèi)核,因?yàn)樗鼈兦度朐诼阈局胁⒈豢删幊踢壿嫮h(huán)繞。

軟核有兩種實(shí)現(xiàn)方案。第一種——通常更常見——是采用供應(yīng)商已經(jīng)支持的設(shè)計(但仍取決于設(shè)計團(tuán)隊(duì)來決定增加I / O和其它外圍設(shè)備)。另外一個,設(shè)計團(tuán)隊(duì)HDL具有代碼購買權(quán),并把它納入FPGA的HDL代碼中。

為加快研發(fā)時間并讓系統(tǒng)設(shè)計者更容易使用,可編程邏輯供應(yīng)商提供了各種流行的MCU內(nèi)核。 例如Altera公司,提供來自ARM、飛思卡爾半導(dǎo)體和英特爾的可用內(nèi)核——同時附帶自己的Nios和Nios II處理器內(nèi)核,這些自有內(nèi)核不需要支付版權(quán)費(fèi)。

賽普拉斯半導(dǎo)體公司的PSoC5集成了可配置的模擬和數(shù)字外設(shè)功能、存儲器和微控制器。PSoC5使用67 MHz的ARMCortexTM-M3內(nèi)核。PSoC4集成了ARM的Cortex-M0核心,而PSoC3集成了英特爾的8位MCU8051核心。

SoPC的優(yōu)點(diǎn)

使用內(nèi)含MCU功能的SoPC有幾個強(qiáng)大理由。第一個是要意識到使用專用MCU的隱形成本。如果該部件不具備有關(guān)特性的適當(dāng)組合,例如,外部邏輯和軟件,那么必須重新開發(fā)以彌補(bǔ)功能缺口。盡管MCU供應(yīng)商提供具有專門特性的器件,以滿足特定的應(yīng)用需求,但這些芯片沒有考慮到動態(tài)的市場條件下可能需要在非常短的時間內(nèi)加入一個新的接口或外圍設(shè)備的可能情況。

設(shè)計目前最先進(jìn)工藝技術(shù)的新款微控制器成本很高,也需要很長的時間。MCU供應(yīng)商已經(jīng)通過加入更多的特性來回應(yīng)市場需求——但其中的一些特性在某些應(yīng)用中并無任何用途。這也增加了產(chǎn)品成本,而這在成本敏感的市場中是致命的。

SoPC的出現(xiàn)“帥氣”地解決了這些問題。這種芯片可在設(shè)計過程中根據(jù)需要進(jìn)行編程和重新編程,加快快速原型開發(fā)和縮短產(chǎn)品進(jìn)入市場時間。 如果需求發(fā)生變化,SoPC還可以現(xiàn)場升級——即便該設(shè)備已經(jīng)在某個產(chǎn)品中部署過。

因?yàn)榫邆淙骝?yàn)證、固件開發(fā)和現(xiàn)場測試等優(yōu)點(diǎn),開發(fā)風(fēng)險可以最小化。設(shè)計工程師可以在系統(tǒng)中運(yùn)行SoPC,從而檢測該設(shè)備在真實(shí)世界運(yùn)行情況,從而確定潛在的設(shè)計缺陷。

在單個SOPC開發(fā)系統(tǒng)級軟件可以大大縮短整個軟件的開發(fā)周期。采用FPGA供應(yīng)商的工具可以更容易地發(fā)現(xiàn)bug,并確定兼容性問題。如果所需功能不能在軟件中實(shí)現(xiàn),識別出額外的硬件支持需求也宜早不宜遲。對于之前未被發(fā)現(xiàn)的缺陷或加入新功能來說,SoPC可以快速修改,而不需要大量的一次性工程費(fèi)用或冗長的制造周期。他們還提供展示樣品,可供銷售人員使用來增加確保客戶預(yù)購的概率。除了快速原型的優(yōu)勢外,許多情況下SoPC也可用于批量生產(chǎn)。

案例:汽車電子中處理器的靈活性

汽車對集成MCU的需求基本無止境。每一個主要系統(tǒng)——僅列出其中的幾個:發(fā)動機(jī)控制、制動、底盤和娛樂信息——都至少需要一個MCU。傳統(tǒng)上,需求由定制的MCU來滿足,但隨著應(yīng)用(以及各種MCU變體)數(shù)量的增加,這一策略也受到質(zhì)疑。汽車制造商正在尋求更靈活、更易定制的解決方案,在某些情況下,F(xiàn)PGA是合適的選擇。

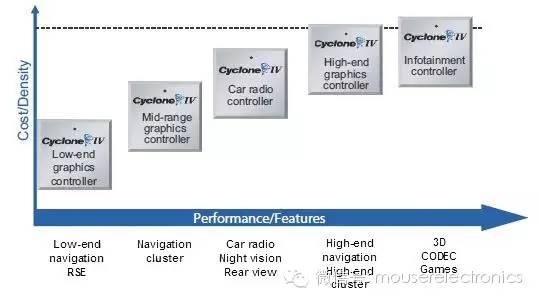

在汽車電子中已經(jīng)開始使用FPGA來實(shí)現(xiàn)圖形控制器,部分原因是因?yàn)殡S著計算和I / O需求的增長,F(xiàn)PGA能夠迅速重新配置,以在沒有大幅增加一次性工程費(fèi)用的前提下滿足新挑戰(zhàn)。圖4顯示了Altera的CycloneIV,它可以被重新配置以處理日益苛刻的應(yīng)用。

圖4:Altera的Cyclone IV是一系列汽車圖形應(yīng)用中具有成本效益的解決方案。

在每個實(shí)現(xiàn)中,Altera的Nios II MCU內(nèi)核可以根據(jù)設(shè)計人員的規(guī)格自動產(chǎn)生。通過使用QuartusII設(shè)計軟件中的Altera SOPC生成器,給設(shè)計選擇合適參數(shù)后,可以實(shí)現(xiàn)邏輯所需的精準(zhǔn)功能和相應(yīng)功耗。

NIOS II采用RISC架構(gòu),帶有獨(dú)立的32位地址和數(shù)據(jù)總線。兩種總線都有自己的緩存。然而設(shè)計師做出最終決定,比如是否為代碼和數(shù)據(jù)使用獨(dú)立的緩存——或者使用共享內(nèi)存方式。盡管Nios II具有其他先進(jìn)的處理器功能,但設(shè)置決定了它們的最終特性。舉例來說,硬件乘法器、桶形移位器以及硬件除法可以作為可選項(xiàng)。同樣的,指令和數(shù)據(jù)高速緩存也是可選項(xiàng),可以改變大小或完全省掉。

結(jié)論

使用SoPC的解決方案帶來的靈活性為設(shè)計人員提供更多的機(jī)會,比如為某個特定應(yīng)用開發(fā)精準(zhǔn)的微控制器。該芯片可在設(shè)計過程中根據(jù)需要進(jìn)行編程和重新編程,從而實(shí)現(xiàn)快速原型和縮短進(jìn)入市場時間。現(xiàn)場測試可以在設(shè)計周期結(jié)束后立即完成,甚至是同步完成。 如果需求發(fā)生變化,SoPC也可以現(xiàn)場升級——即便該器件已經(jīng)在某個產(chǎn)品中部署過。

-

處理器

+關(guān)注

關(guān)注

68文章

19409瀏覽量

231190 -

芯片

+關(guān)注

關(guān)注

456文章

51189瀏覽量

427293 -

存儲器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164345

發(fā)布評論請先 登錄

相關(guān)推薦

開源技術(shù)推動教育數(shù)字化高質(zhì)量發(fā)展

開源技術(shù)助力電力行業(yè)創(chuàng)新發(fā)展

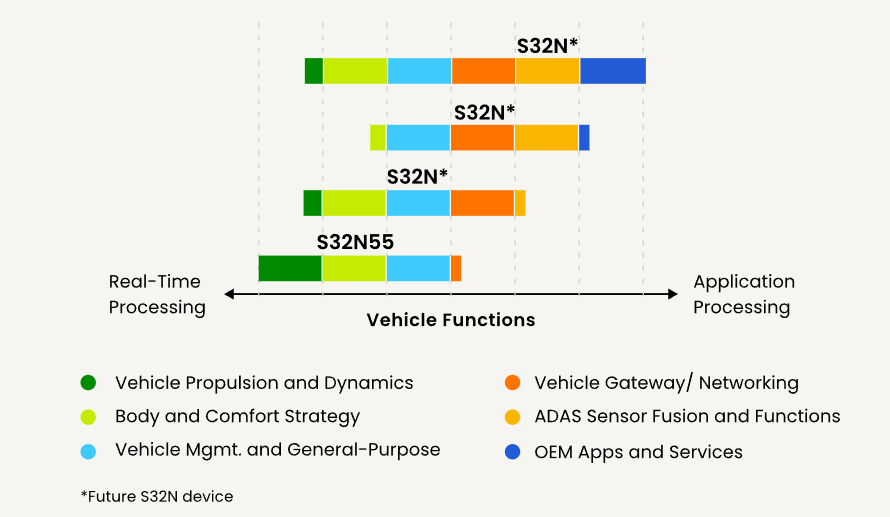

5nm制程,16核心?高性能汽車MCU發(fā)展趨勢

開源技術(shù)推動醫(yī)療行業(yè)創(chuàng)新發(fā)展

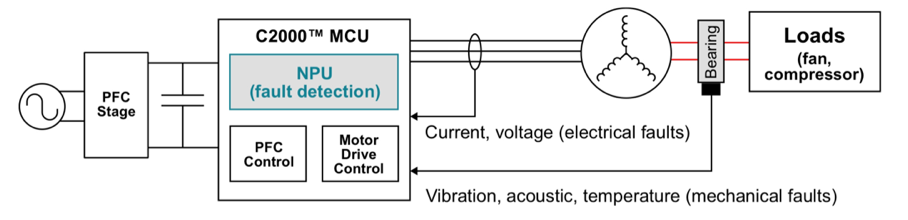

MCU如何增強(qiáng)高壓實(shí)時控制系統(tǒng)中的故障檢測功能

云臺解決方案中的無刷驅(qū)動技術(shù),為交通行業(yè)帶來了顯著變革

瑞薩電子亮相2024全球MCU及嵌入式生態(tài)發(fā)展大會

愛普特32位MCU在電機(jī)控制上的應(yīng)用

AI模型在MCU中的應(yīng)用

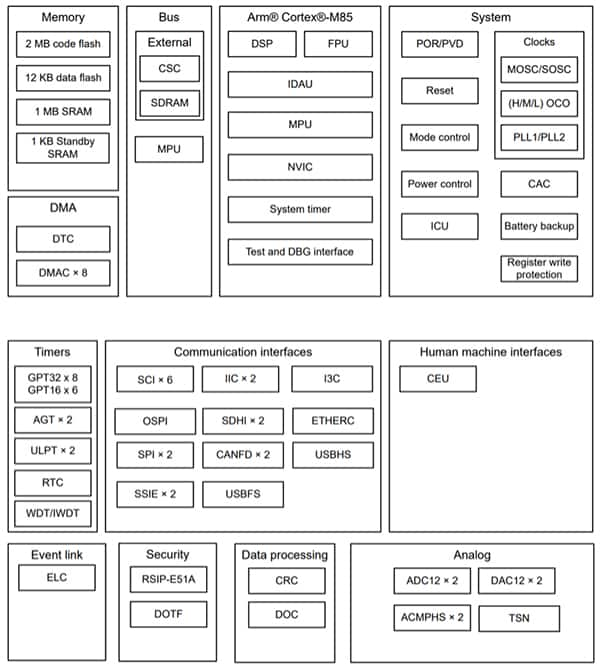

使用 Renesas RA8M1 MCU 快速地部署強(qiáng)大高效的 AI 和 ML 功能

RISC-V在服務(wù)器方面應(yīng)用與發(fā)展前景

未來,IPv6將帶來更強(qiáng)大的新興變革及應(yīng)用

瑞薩半導(dǎo)體:洞察MCU市場趨勢,積極應(yīng)對技術(shù)變革

Arm發(fā)布Neoverse V3和N3 CPU內(nèi)核

基于MCU的設(shè)計快速發(fā)展給SoPC帶來變革

基于MCU的設(shè)計快速發(fā)展給SoPC帶來變革

評論